1?

億靈思設計軟件介紹

億靈思設計軟件是中科億海微基于多年可編程邏輯芯片開發軟件技術攻關與工程實踐應用而研發的一款擁有國產自主知識產權的大規模可編程邏輯芯片開發軟件,可以支持千萬門級以上可編程邏輯芯片的設計開發,同時提供幾十種常用的IP核方便用戶進行開發設計。從使用方向上看,億靈思設計軟件可支持以下兩大設計功能:

大規模可編程邏輯芯片開發設計

嵌入式可編程電路IP核設計評估

2?

可編程邏輯芯片應用設計

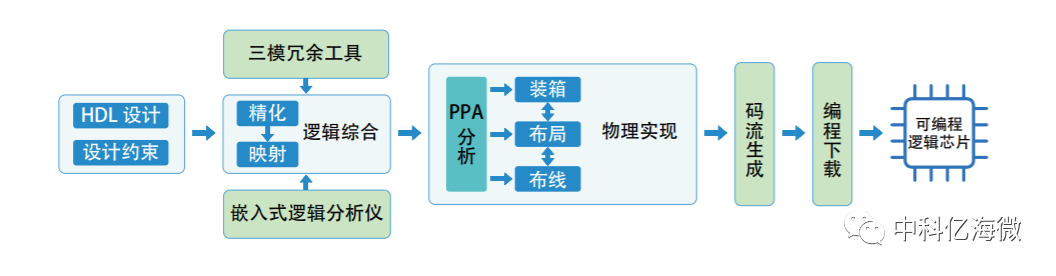

億靈思設計軟件支持工業界標準的可編程邏輯芯片開發流程,可以實現從RTL設計輸入、邏輯綜合、工藝映射、裝箱、布局布線、碼流生成、編程下載的全套操作。億靈思設計軟件處理流程如下圖所示:

軟件處理流程圖

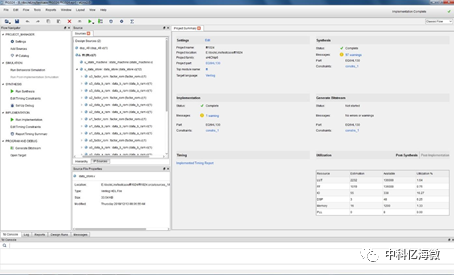

億靈思設計軟件的界面操作流程與國外知名廠家的軟件操作流程一致,并且界面風格也極為相似,用戶不需要重新學習即可上手操作,大大節約了開發人員的學習成本。億靈思設計軟件的開發界面如下圖所示:

億靈思設計軟件主界面

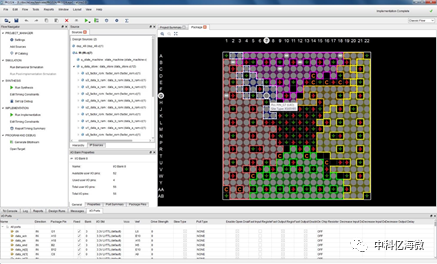

管腳指定界面

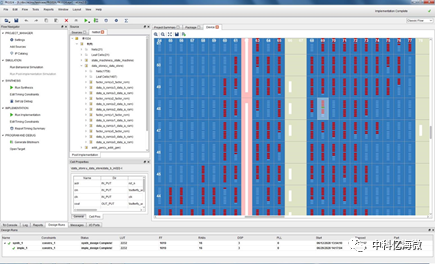

位置約束功能界面

3?

嵌入式可編程電路IP核設計評估

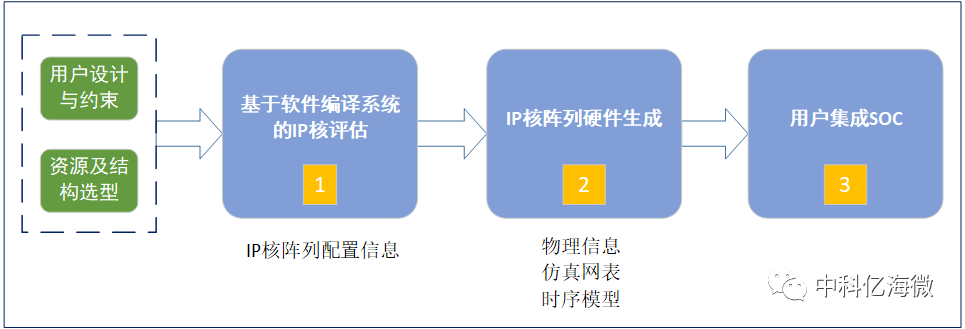

面向SoC集成,中科億海微為用戶提供基于正向軟硬件設計技術的嵌入式可編程電路IP核和配套的自主研發的可編程電路IP核評估軟件,可以針對用戶需求快速定制設計各種可編程電路IP,并進行初步的設計評估。從設計流程上看,首先,用戶綜合考慮設計約束和資源結構,進行IP核定制編程資源規模評估,生成IP核陣列配置信息;然后,根據陣列配置信息生成IP核硬件電路結構,并產生嵌入式可編程電路IP核的物理模型、功能模型和時序模型;最后,用戶可根據這些結果將嵌入式可編程電路IP核集成到SoC中,進行進一步的芯片集成設計。

嵌入式可編程電路IP核開發流程圖

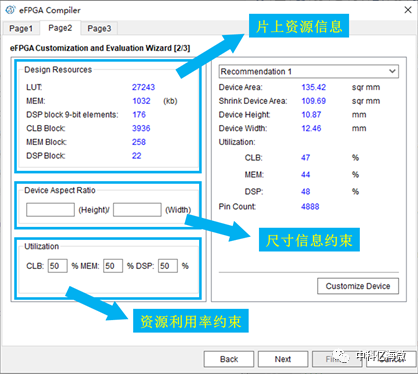

嵌入式可編程電路IP核參數評估軟件界面如下圖所示:

嵌入式可編程電路IP核參數評估軟件界面

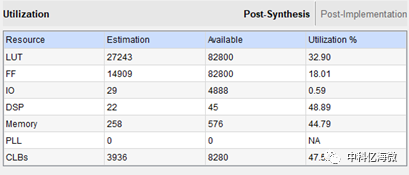

在嵌入式可編程電路IP核參數評估軟件界面中可直觀看到片上資源信息情況,用戶可根據實際應用情況對IP核尺寸信息或資源利用率進行靈活調配,從而獲得所需的IP核評估結果。下圖是具體電路占用IP核資源情況。

自定義嵌入式可編程電路IP核邏輯資源使用表

4?

優勢

億靈思設計軟件采用全正向自主設計,用戶可實現相關數據的加密處理,提高安全性;

具有嵌入式可編程電路IP核complier功能,可幫助用戶根據自己的需求靈活定制嵌入式可編程電路IP核的規模和排布;

集成高性能算法,在運行時間和性能上已經接近或達到國外同款主流商業軟件的水平;

兼容國外主流軟件的業務流程,且操作界面相似,工程師零學習成本便可快速上手;

提供三模冗余功能,通過軟件加固的方式可大幅提升設計可靠性。

-

芯片

+關注

關注

453文章

50405瀏覽量

421809 -

eda

+關注

關注

71文章

2708瀏覽量

172880

發布評論請先 登錄

相關推薦

德州儀器推出全新可編程邏輯產品系列

德州儀器 (TI) 全新可編程邏輯產品系列助力工程師在數分鐘內完成從概念到原型設計的整個過程

什么是現場可編程邏輯陣列?它有哪些特點和應用?

FPGA零基礎學習系列精選:半導體存儲器和可編程邏輯器件簡介

可編程片上系統的基本特征和主要應用

可編程片上系統是什么意思

可編程片上系統是什么

現場可編程門陣列的原理和應用

現場可編程門陣列簡介

現場可編程門陣列是什么

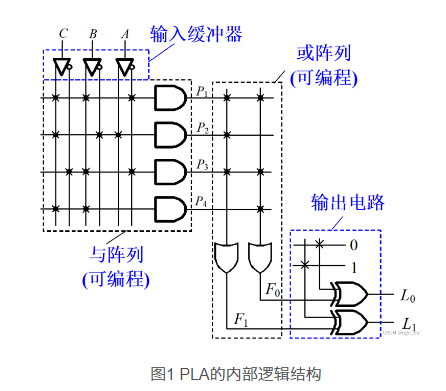

可編程邏輯陣列PLA內部邏輯結構示意

億靈思?國產可編程邏輯芯片EDA軟件系列二:零學習成本、輕松上手!

億靈思?國產可編程邏輯芯片EDA軟件系列二:零學習成本、輕松上手!

評論