MT41K256M16TW-107 IT:P DRAM 芯片 DDR3L SDRAM 4G-Bit 256M x 16 1.35V 96-Pin F-BGA

制造商: 美光

安富利制造商零件編號: 80AH8027

MT41K256M16TW-107 DDR3 SDRAM 使用雙倍數據速率架構來實現高速運行。雙倍數據速率架構是一種 8n 預取架構,其接口設計用于在 I/O 引腳上每個時鐘周期傳輸兩個數據字。

MT41K256M16TW-107 DDR3 SDRAM 的單個讀或寫操作實際上由內部 DRAM 內核的單個 8n 位寬、四個時鐘周期的數據傳輸和八個相應的 n 位寬、一個半時鐘周期的數據傳輸組成。 I/O 引腳。差分數據選通(DQS、DQS#)與數據一起從外部傳輸,用于 DDR3 SDRAM 輸入接收器的數據捕獲。DQS 與 WRITE 的數據居中對齊。

讀取數據由 DDR3 SDRAM 傳輸并與數據選通沿邊緣對齊。DDR3 SDRAM 使用差分時鐘(CK 和 CK#)運行。CK 變高和 CK# 變低的交叉點稱為 CK 的上升沿。控制、命令和地址信號在 CK 的每個上升沿被寄存。輸入數據在 WRITE 前導碼后 DQS 的第一個上升沿寄存,輸出數據在 READ 前導碼后 DQS 的第一個上升沿上參考。

對 DDR3 SDRAM 的讀寫訪問是面向突發的。訪問從選定的位置開始,并在編程序列中繼續編程數量的位置。訪問以注冊 ACTIVATE 命令開始,然后是 READ 或 WRITE 命令。與 ACTIVATE 命令同時注冊的地址位用于選擇要訪問的存儲體和行。與 READ 或 WRITE 命令同時注冊的地址位用于為突發訪問選擇存儲體和起始列位置。

該設備使用 READ 和 WRITE BL8 和 BC4。可以啟用自動預充電功能以提供在突發訪問結束時啟動的自定時行預充電。與標準 DDR SDRAM 一樣,DDR3 SDRAM 的流水線、多組架構允許并發操作,從而提供高帶寬 b 隱藏行預充電和激活時間。提供自刷新模式以及省電、掉電模式。

MT41K256M16TW-107 主要特點

- VDD = VDDQ = +1.35V(1.283V 至 1.45V)

- 向后兼容 VDD = VDDQ = 1.5V ±0.075V

- 差分雙向數據選通

- 8n 位預取架構

- 差分時鐘輸入(CK、CK#)

- 8家內部銀行

- 數據、選通和屏蔽信號的標稱和動態片上端接 (ODT)

- 可編程 CAS (READ) 延遲 (CL)

- 可編程 CAS 附加延遲 (AL)

- 可編程 CAS (WRITE) 延遲 (CWL)

- 固定突發長度 (BL) 為 8,突發斬波 (BC) 為 4(通過模式寄存器組 [MRS])

- 可選擇 BC4 或 BL8 即時 (OTF)

- 自刷新模式

- 0°C 至 95°C 的 TC

- 0°C 至 85°C 下 64 毫秒、8192 周期刷新

- 85°C 至 95°C 時為 32 毫秒

- 自刷新溫度 (SRT)

- 自動自刷新 (ASR)

- 寫調平

- 多用途寄存器

- 輸出驅動校準

-

三星電子

+關注

關注

34文章

15856瀏覽量

180933 -

汽車電子

+關注

關注

3024文章

7883瀏覽量

166552 -

內存條

+關注

關注

0文章

143瀏覽量

19504

發布評論請先 登錄

相關推薦

PCM1865做TDM模式4通道音頻采集,LRCK占空比不是1/256嗎?

TAS5731采樣率改為16k的時候,就沒有聲音了,為什么?

AP89682K/341k/170k/085k語音OTP IC英文手冊

TMS470R1A256 16/32位RISC閃存微控制器數據表

RM41L232 16位和32位RISC閃存微控制器數據表

CKS32F107xx系列MCU中ADC介紹

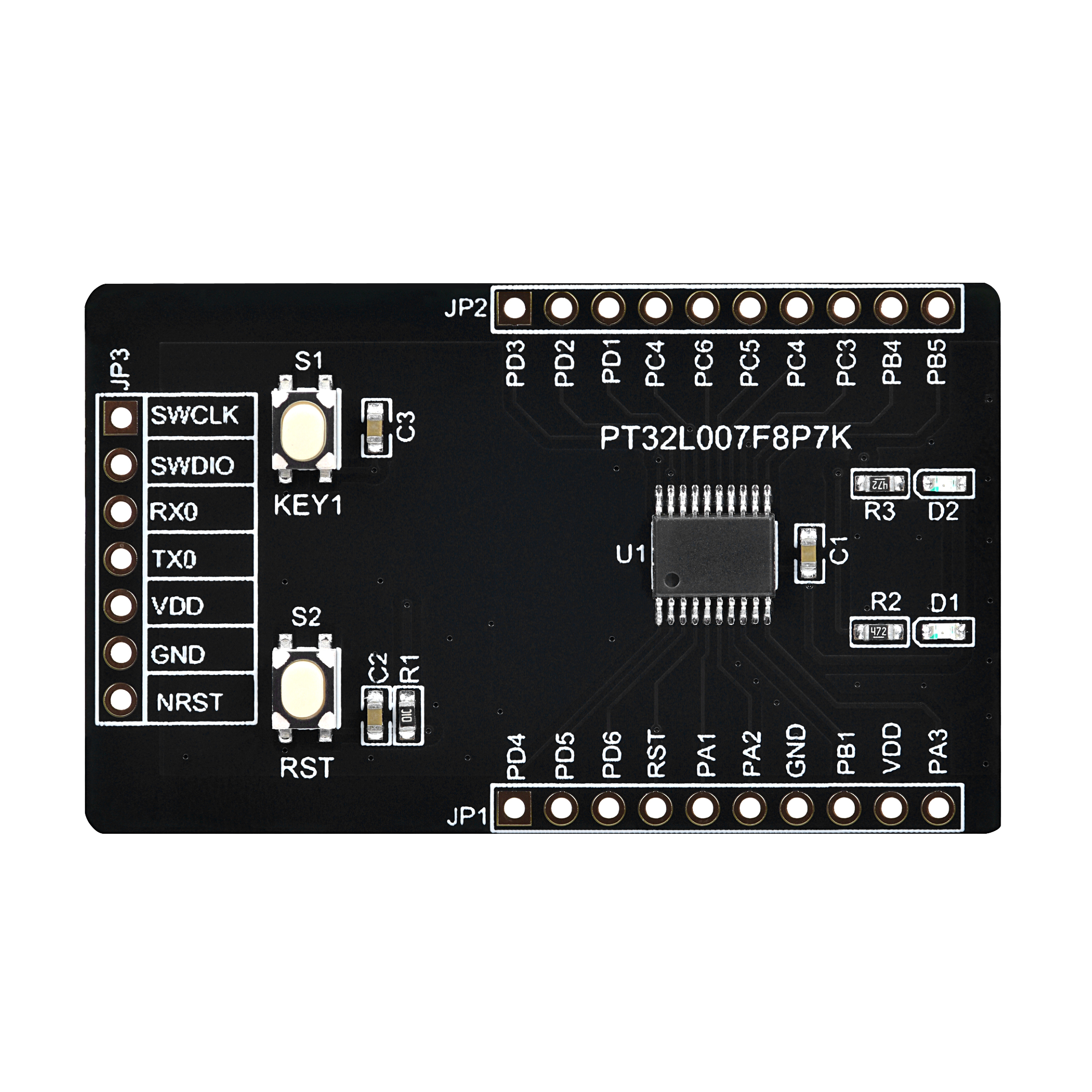

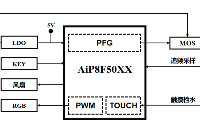

PT32L007F8P7K& QMA6100P IIC 通訊源代碼分享

CD54HC107,CD74HC107,CD74HCT107觸發器數據表

MT47H64M16HR 的IP核可以在哪下載

7芯M16插頭是否防水

MT41K256M16TW-107 IT:P STOCK

MT41K256M16TW-107 IT:P STOCK

評論