RJGT101應用筆記(二)

RJGT101應用開發概述

在應用開發(一)中簡單介紹了 RJGT101在版權保護應用的領域以及加密芯片應用的邏輯框圖,本章節介紹RJGT101在實際應用中硬件參考電路、軟件參考代碼的簡述,以方便在實際開發中能夠快速的上手和更好的把加密芯片應用的好。

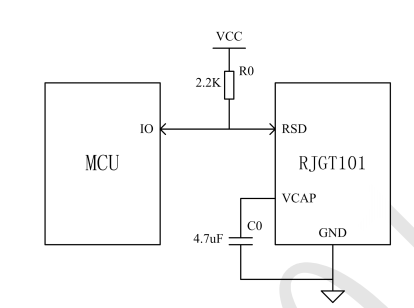

硬件參考設計(注意事項)

注意:

1.MCU的I/O配置輸出模式為 推挽輸出,I/O的驅動能力最少1mA.

2.R0=2.2k可適當小一些也沒問題;

C0= 4.7uF理論值C0 > 100nF就可以。

a.從硬件電路上看不到與RJGT101供電的引腳,在實際應用中電路安如上圖所示即可,RJGT101的供電有C0提供,MCU的RSD默認輸出高給電容充電,根據芯片設計最佳電容值為4.7uF。

b.若產品在設計時確定認證結束就斷開與RJGT101的通訊,需要注意再次連接認證時需先拉高RSD進行延時10ms以滿足C0的供能。

- 軟件參考設計(注意事項)

a.軟件設計提供基于STM32F103的demo歷程,應用時需要進行代碼移植。

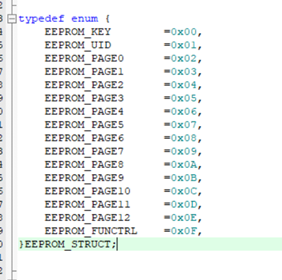

b.左圖為RJGT101在應用中常用的功能函數,demo中都已進行封好直接調用就可以達到功能需求,建議在剛調試時先驗證通訊是否正常(只讀版本號,能夠正確讀取版本號,說明通訊是沒有問題的)然后在進行功能的設計。

c.右圖來示意整片RJGT101的存儲,可以看到每頁代表了什么功能屬性。

d.EEPROM_FUNCTRL頁是整個芯片的控制使能,每字節的使能可詳細參考技術手冊。

e.芯片的正常使用需要滿足 EEPROM_FUNCTRL 0x09的值為5A;否則可以通過RJGT101_WriteEeprom();函數進行初始化。

f.demo歷程中的函數已詳細備注功能,如有其他疑問可聯系我們。

應用答疑(FAQ)

a.調試過程中讀取的版本號為FF是怎么回事(檢查硬件無誤)?

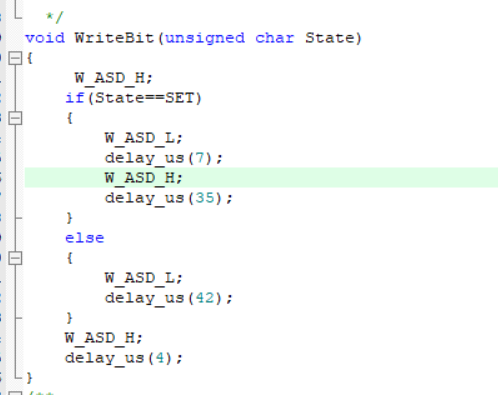

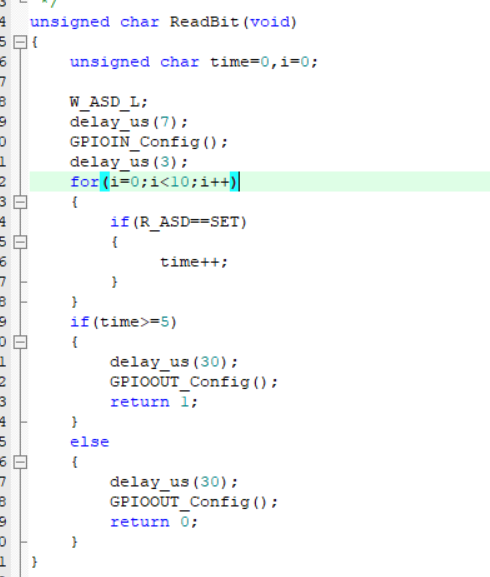

此類問題大概率為RSD的通訊時序不對造成的,可從以下兩個函數進行排查

ReadBit();WriteBit();

主要測試延時函數是否準確,可以配置個簡單的I/0翻轉,如果誤差比較大建議可以使用nop指令進行設計延時。時序正常狀態下,一個bit在50us左右。

b.芯片計次遞增怎么操作,每認證一次就會遞增一次嗎?

計次遞增需要保證 EEPROM_FUNCTRL頁 0x08字節為A5/5A才可以使能;遞增指令為RJGT101_WriteCmd(0x69);只有主控端進行發送指令才會+1和認證多少次沒有關系,需主動操作。

c.RJGT101的數據區怎么使用直接讀寫函數和認證讀寫函數都可以正常操作?

如果IC的EEPROM_FUNCTRL頁 0x08字節為非5A;可直接通過讀寫函數操作,同時也支持認證讀寫,只有此字節為5A時數據區的安全性最高只能通過認證讀寫進行操作。

d.如果EEPROM_FUNCTRL頁的數據丟失怎么辦?

建議先讀取確定是否真的丟失,是否還可以操作其他頁的數據,如果確定丟失可以調用讀寫函數直接對此頁進行初始化 寫入相應的使能值即可。

以上是在調試遇到頻率較高的問題,大家在使用過程中可以參考進行解答,如不能解答可以需求我司FAE進行支持。

-

芯片

+關注

關注

454文章

50430瀏覽量

421861

發布評論請先 登錄

相關推薦

RJGT101 應用筆記(二)

RJGT101 應用筆記(二)

評論