美浦森超結MOS在照明電源中的應用

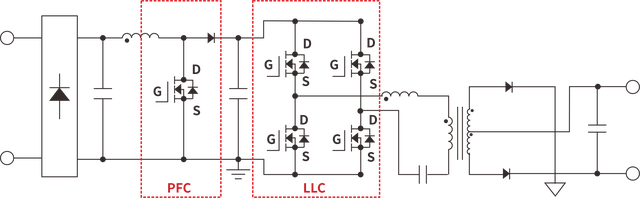

隨著電源技術和功率器件以及通信技術的發展,目前的照明產品越來越趨向于智能化,小型化。對電源的體積和功率密度的要求也越來越高。因此,越來越多的新型半導體器件也逐漸應用到LED照明產品上,比如超結MOS的應用就越來越普遍,許多LED電源廠商以開始用超結MOS去替代VDMOS,在達到高效率的同時,更節省了電源空間和生產成本。今天我們來討論一下在照明行業中改如何選擇合適的超結MOS。

首先,我們需要了解超結MOS和VDMOS的優缺點,以及在照明產品中我們應該注意MOS的哪些重要參數。

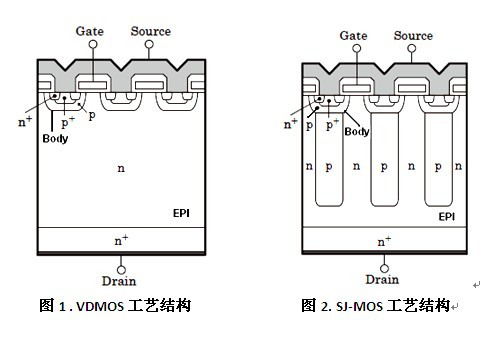

一、超結MOS與VDMOS的結構差異

為了克服傳統MOS導通電阻與擊穿電壓之間的矛盾,一些人在VDMOS基礎上提出了一種新型的理想器件結構,稱為超結器件或SJ-MOS,他們的結構如圖1和圖2所示,其由一些列的P型和N型半導體薄層交替排列組成。在截止態時,由于P型和N型層中的耗盡區電場產生相互補償效應,使P型和N型層的摻雜濃度可以做的很高而不會引起器件擊穿電壓的下降。導通時,這種高濃度的摻雜可以使其導通電阻顯著下降,大約有兩個數量級。因為這種特殊的結構,使得SJ-MOS的性能優于傳統的VDMOS.

二、超結MOS的優點

1、通態阻抗小,通態損耗小。

由于超結MOS的Rdson遠遠低于VDMOS,在系統電源類產品中超結MOS的導通損耗必然較之VDMOS要減少的多。其大大提高了系統產品上面的單體MOSFET的導通損耗,提高了系統產品的效率。

2、同等功率規格下封裝小,有利于功率密度的提高。

首先,同等電流以及電壓規格條件下,超結MOS的晶圓面積要小于VDMOS工藝的晶圓面積,這樣作為MOS的廠家,對于同一規格的產品,可以封裝出來體積相對較小的產品,有利于電源系統功率密度的提高。

其次,由于超結MOS的導通損耗的降低從而降低了電源類產品的損耗,因為這些損耗都是以熱量的形式散發出去,我們在實際中往往會增加散熱器體積來降低MOS單體的溫升,使其保證在合適的溫度范圍內。由于超結MOS可以有效的減少發熱量,減小了散熱器的體積,對于一些功率稍低的電源,甚至使用超結MOS后可以將散熱器徹底拿掉。有效的提高了系統電源類產品的功率密度。

3、柵電荷小,對電路的驅動能力要求降低。

傳統VDMOS的柵電荷相對較大,我們在實際應用中經常會遇到由于IC的驅動能力不足造成的溫升問題,部分產品在電路設計中為了增加IC的驅動能力,確保MOSFET的快速導通,我們不得不增加推挽或其它類型的驅動電路,從而增加了電路的復雜性。超結MOS的柵電容相對比較小,這樣就可以降低其對驅動能力的要求,提高了系統產品的可靠性。

4、結電容小,開關速度加快,開關損耗小。

由于超結MOS結構的改變,其輸出的結電容也有較大的降低,從而降低了其導通及關斷過程中的損耗。

同時由于超結MOS柵電容也有了響應的減小,電容充電時間變短,大大的提高了超結MOS的開關速度。對于頻率固定的電源來說,可以有效的降低其開通及關斷損耗。提高整個電源系統的效率。

三、超結MOS系統應用可能會出現的問題

1、EMI可能超標。

由于超結MOS擁有較小的寄生電容,造就了超結MOS具有極快的開關特性。因為這種快速開關特性伴有極高的dv/dt和di/dt,會通過器件和印刷電路板中的寄生元件而影響開關性能。對于在現代高頻開關電源來說,使用了超結MOS,EMI干擾肯定會變大。

2、柵極震蕩。

功率MOSFET的引線電感和寄生電容引起的柵極震蕩,由于超結MOSFET具有較高的開關dv/dt。其震蕩現象會更加突出。這種震蕩在啟動狀態、過載狀況和MOSFET并聯工作時,會發生嚴重問題,導致MOSFET失效的可能。

3、抗浪涌及耐壓能力差。

由于超結MOS的結構原因,很多廠商的超結MOS在實際應用推廣替代VDMOS的過程中,基本都出現過浪涌及耐壓測試不合格的情況。這種情況在通信電源及雷擊要求較高的電源產品上,表現的更為突出。這點必須引起我們的注意。

4、漏源極電壓尖峰比較大。

在反激的電路拓撲中,由于本身電路的原因,變壓器的漏感、散熱器接地、以及電源地線的處理等問題,不可避免的要在MOSFET上產生相應的電壓尖峰。針對這樣的問題,反激電源大多選用RCD SUNBER電路進行吸收。由于超結MOS擁有較快的開關速度,勢必會造成更高的VDS尖峰。如果反壓設計余量太小及漏感過大,更換超結MOS后,極有可能出現VD尖峰失效問題。

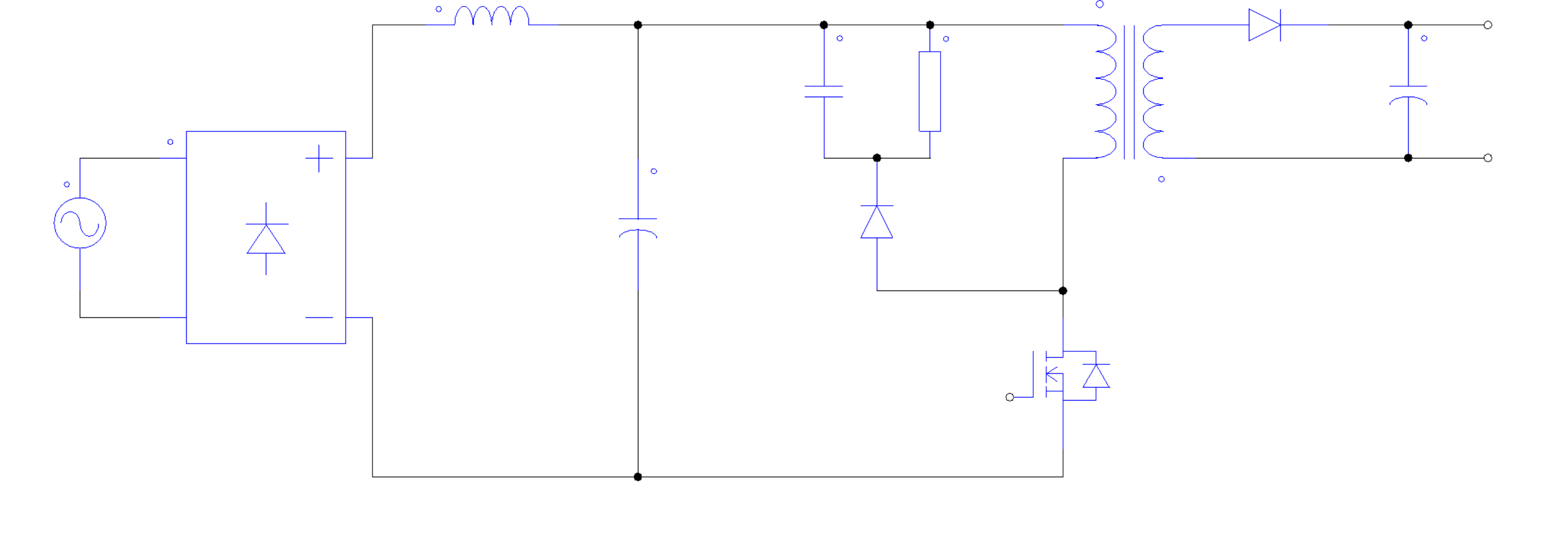

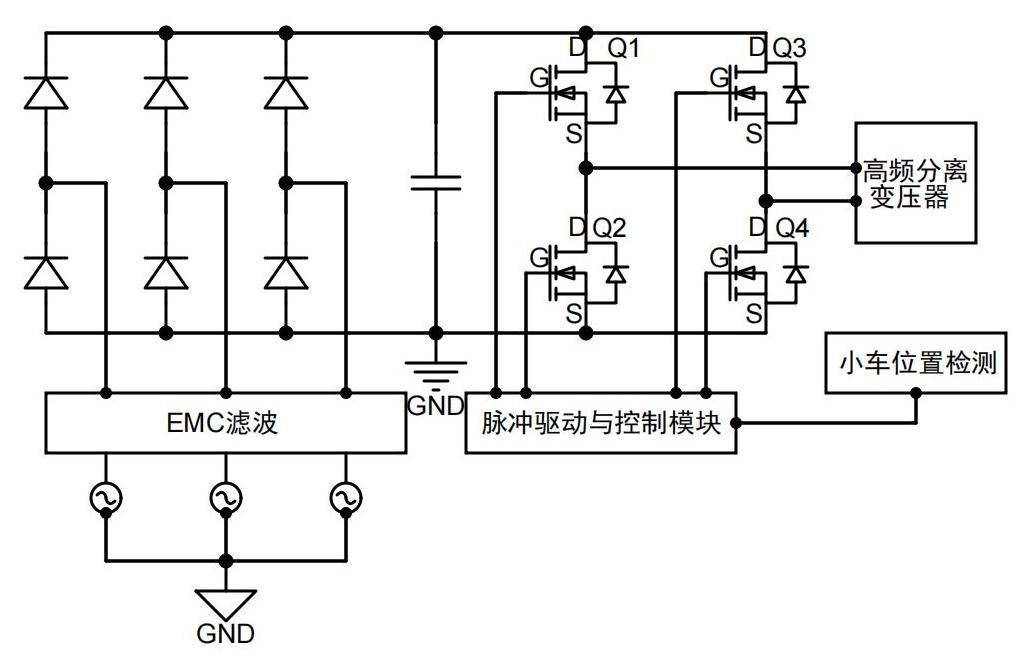

目前我們在100W內的照明市場主要采用的是PSR拓撲結構,如圖3:

在這種結構下,超結MOS相比VDMOS,其遠低于VDMOS的Rdson和小封裝體積的優勢非常明顯。例如,我們可以用252的封裝外型去替代220F,在節省了散熱器的同時,還能保證較高的效率和較低的溫升,也更加利于生產。

同時,在這種構架下,超結MOS的EMI和浪涌較差的缺點也非常突出。由于前端沒有濾波電解電容,在浪涌沖擊時,Vbus電壓會升的很高,隨著Ton的減小,ID電流變大,Vds會升的很高,對MOS的雪崩能力要求比較高。

如圖,在同樣的浪涌情況下,超結MOS失效的可能性更高。這就要求我們在選擇超結MOS的時候,必須重點考慮MOS的雪崩能力。

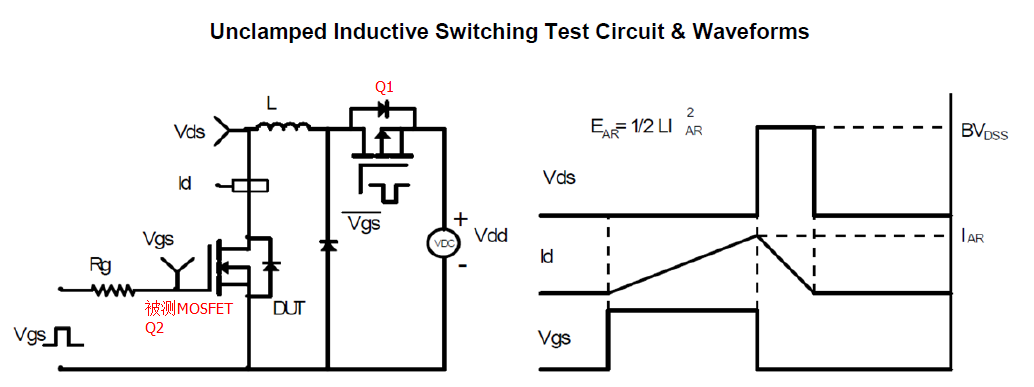

我們知道MOSFET的規格書中,EAS的指標值直接反應了MOS的抗浪涌能力。而實際中,我們看到各個廠家在此參數上的值相去甚遠,這主要是因為各個廠家的測試條件不一樣。通用的EAS測試電路如下:

由圖可知,L和I的取值不同,實測的EAS值也不同。一般情況下會采用較小的L以及較大的I進行測試。我們在選擇超結MOS時,應以相同測試條件下EAS值較大的為優。

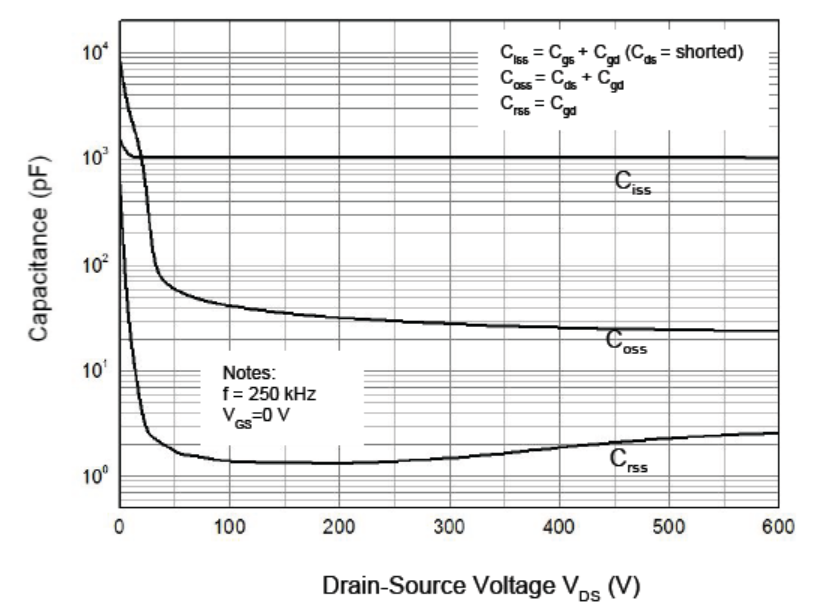

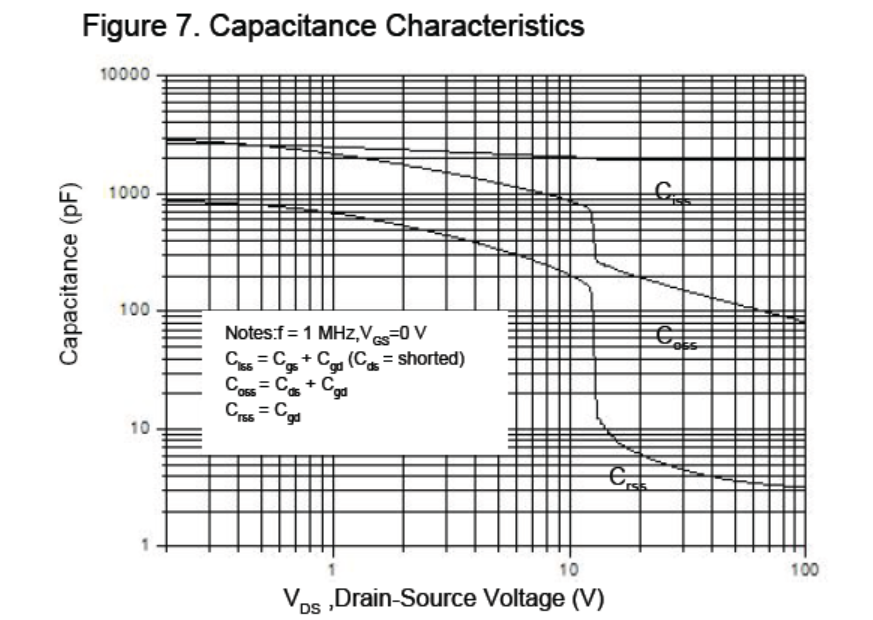

另外,由于超結的Qg很小,在快速開關中會產生較大的dv/dt和di/dt,從而造成EMI困擾。實際選用時,我們應關注MOS的電容的特性。如下圖:

芯晶圖電子潘17633824194

芯晶圖電子潘17633824194為12A的VDMOS和12A的超結MOS的電容曲線特性對比。超結MOS的電容特性突變更大。由此帶來更差的EMI效果。

-

芯片

+關注

關注

453文章

50406瀏覽量

421829 -

電子元器件

+關注

關注

133文章

3307瀏覽量

104939 -

MOSFET

+關注

關注

144文章

7088瀏覽量

212721 -

IC

+關注

關注

36文章

5900瀏覽量

175238

發布評論請先 登錄

相關推薦

美浦森超結MOS在照明電源中的應用

美浦森超結MOS在照明電源中的應用

評論