靜電放電保護器件種類與特點

概述

靜電放電(ESD)是一種意外的快速高壓瞬態(tài)波形,出現(xiàn)在電路內的導體上。ESD引起的高電壓和電流峰值可能導致靜電敏感IC等器件發(fā)生故障。人際接觸是ESD的常見來源。即使人與電路沒有直接接觸,電容式檢測開關等器件也可以允許電荷耦合到電導體上。在ESD放電可能導致電路故障的情況下,需要ESD保護。

電磁干擾(EMI):電磁輻射的存在,可能會破壞附近的系統(tǒng)。EMI的來源包括電風暴(閃電),主電源線中斷,太陽輻射和附近的電路(電源,變速電機驅動器,電弧焊機等)。

電磁兼容性 (EMC):衡量系統(tǒng)在以下兩方面的能力:

在電磁輻射 (EMI) 下正常工作。

不會發(fā)出超過系統(tǒng)類型及其使用環(huán)境所定義的法規(guī)的EMI。

靜電保護器件種類

下表總結了可用于 ESD 保護的不同組件。大致按從最低功率到最高功率分量排序。

優(yōu)勢:便宜、小

缺點:對高功率ESD事件無效

對高電壓|敏感適用于幫助降低由小 ESD 事件引起的電壓尖峰

?

優(yōu)勢:非常嚴格控制的“接通”電壓

缺點:對高功率ESD事件無效

齊納二極管是雪崩二極管的一種形式,就像TVS一樣。主要區(qū)別在于,齊納二極管通常設計用于更清晰的導通特性(用于電壓調節(jié)目的),而功耗則更小。

TVS瞬態(tài)電壓抑制二極管

優(yōu)勢:導通時間快(特別是單向,雙向較慢)

可處理中等功率 ESD 事件

缺點:不適合作為單個元件來有效應對高功率ESD事件(需要與MOV,火花間隙或GDT配對)。

MOV(金屬氧化物壓敏電阻)

優(yōu)勢:通流量大

缺點:累積退化

大漏電流

大電容 (10?1000pF10?1000pF)

氣體放電管

優(yōu)勢:可熄滅極高功率 ESD 事件(例如雷擊)

缺點:比TVS二極管更笨重、更昂貴

不要具有低而尖銳的導通電壓,因此通常與TVS二極管結合使用。

累積降級為高功率事件

GAP火花間隙

火花間隙非常簡單(只是PCB層上的銅形狀!工作原理與GDT相同,但沒有受控的氣氛和壓力。

標準

IEC-61312-1:雷電電磁脈沖保護,于1995年首次推出。

Telecordia GR-1089核心:電磁兼容性和電氣安全 - 網(wǎng)絡電信設備的通用標準:電信服務提供商使用。它包含 NEBS(網(wǎng)絡設備 - 建筑系統(tǒng))標準。

IEC 61643-1,第一版,1998年,連接到低壓配電系統(tǒng)的浪涌保護器件。最早引用8/20us雷電波形之一。

IEEE C62.41.2,關于低壓(1000 V及以下)交流電源電路中浪涌電壓特性化的推薦做法。

符合 IEC 61000-4系列標準

IEC 61000-4 完全是關于電磁兼容性 (EMC) 的。

符合 IEC 61000-4-2 標準

例如,上海雷卯 ULC0511CDN ESD 二極管陣列的 ESD 耐壓 VESD 的額定值為 ±30kV(符合 IEC61000-4-2(接觸),±30kV,符合 IEC61000-4-2(空氣)標準。

IEC 61000-4-4

特別令人感興趣的是第4部分(61000-4-4),標題為“測試和測量技術 - 電氣快速瞬變/突發(fā)抗擾度測試”。它詳細介紹了如何在電路上構建測試以測量其對ESD的敏感性,重點是來自源的ESD,例如感性負載的中斷和繼電器觸點反彈。第一版于1995年發(fā)布。截至2022年,2012年版本是最新的。

IEC 61000-4-4 定義了一些測試級別,以及端口必須能夠承受的相關峰值電壓。“電源端口”和“信號端口”之間是有區(qū)別的。

測試級別 | 峰值電壓 - 電源端口 | 峰值電壓 - 信號端口 |

| 1 | 0.5千伏 | 0.25千伏 |

| 2 | 1千伏 | 0.5千伏 |

| 3 | 2千伏 | 1千伏 |

| 4 | 4千伏 | 2千伏 |

| X | 不適用 | 不適用 |

測試級別 X 指定一個特殊測試,其中級別由用戶定義。所有級別的“重復頻率”均為5或100kHz。

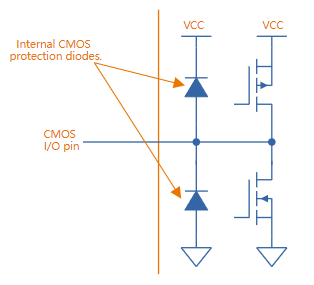

CMOS I/O 上的內部 ESD 保護

內置保護在CMOS I/O引腳上非常常見,這些引腳可能是器件的一部分(從簡單的負載開關到中等復雜性的微控制器,再到高復雜性的FPGA)。它們通常為每個 I/O 引腳兩個。一個連接在引腳和GND之間,一個連接在引腳和VCC之間。兩者在正常工作條件下均為反向偏置(GND<=VI/O<=VCC)。

CMOS數(shù)字I/O引腳示意圖,突出顯示了許多設計中普遍存在的內部保護二極管(即使IC數(shù)據(jù)手冊中沒有提到它們)。

它們用于在引腳發(fā)生故障時保護敏感的CMOS邏輯。如果VI/O 上的電壓高于 VCC(例如,正 ESD 電壓尖峰),則頂部二極管導通,將引腳上的電壓箝位至不超過VCC+Vf。同樣,如果VI/O上的電壓降至VGND以下(例如,負ESD電壓尖峰),則底部二極管導通,將引腳上的電壓箝位至不超過?Vf。

要小心,因為這些二極管通常具有相當?shù)偷淖畲箅娏鳌3^此最大電流將吹動ESD二極管,通常導致其開路,從而消除了敏感CMOS電路的保護,然后幾乎瞬間被油炸。然后,您的 I/O 引腳將停止工作。如果幸運的話,它只會是一個受影響的引腳。如果沒有,整個端口(如果適用),甚至整個設備都會被失效。

無論它們多么有用,它們也會在特定情況下產生設計挑戰(zhàn),因此在進行任何涉及CMOS I/O且存在ESD保護二極管的原理圖設計時,都需要仔細考慮。導致問題的兩種情況是:為具有多個電壓軌的電路上電時。當VI/O上的電壓在某些點上可能高于VCC時,由于輸入信號的性質。在低功耗設計中,當您有選擇地關斷為這些IC供電的電壓軌時。

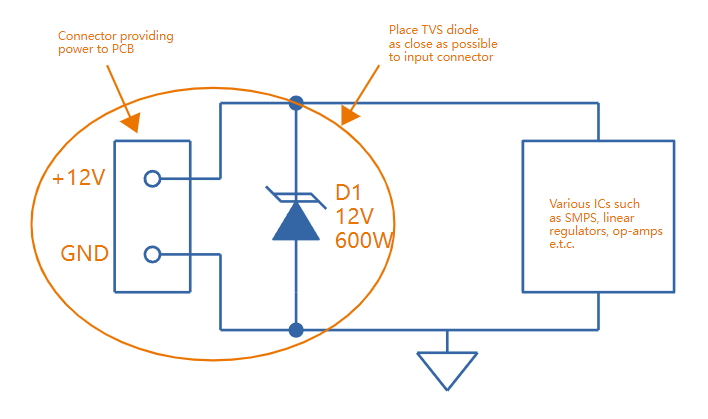

單通道普通 TVS 二極管

養(yǎng)成一個好習慣 - 將TVS二極管放置在PCB的輸入/輸出兩端(而不僅僅是電源軌,盡管這是本原理圖中所示的)。將TVS盡可能靠近PCB的入口位置放置。

如上所示的TVS還可以防止反極性。在這種情況下,TVS將正向導通并將電壓箝位至約?0.7V。確保這會熔斷保險絲,或者TVS足夠大,可以無限期地維持功耗。

在+12V電源上同時使用保險絲和TVS到PCB。在這種情況下,保險絲放置在TVS二極管之前,因此如果+12V以錯誤的方式連接(電流通過F1和D1),保險絲也會熔斷,此處F1采用leiditech的PPTC系列產品。

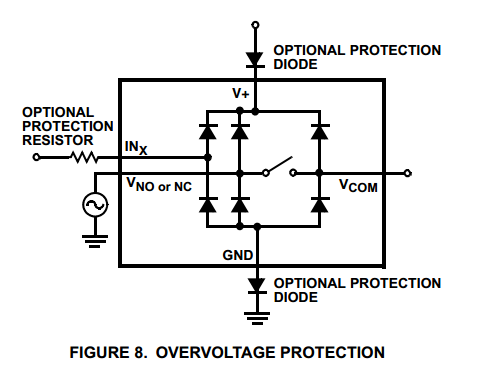

TVS陣列 ESD 二極管

可以添加IC外部的額外二極管,以防止通過具有VCC和GND的ESD保護二極管的器件上的CMOS IO引腳泄漏電流。下圖顯示了如何將它們連接到受保護的IC。

添加外部ESD二極管。

但是,這種方法有其缺點。IC看到的實際電源電壓在二極管上降低兩倍的壓降(VfVf)(通常為2x 0.5-0.7V = 1.0-1.4V)。此外,IC接地現(xiàn)在與系統(tǒng)接地有很大不同。這可能會干擾單端ADC測量和其他模擬功能。

串聯(lián)電阻進入 CMOS I/O

最常用的外部ESD保護方法是在ESD能量源和要保護的集成電路引腳之間添加一個小串聯(lián)電阻。有點違反直覺的是,小至50Ω的電阻可能會使CMOS IC的ESD抗擾度提高一倍。更高的免疫力是可能的;更高的保護水平與增加的串聯(lián)電阻成正比。此方法的工作原理有兩個原因。首先,串聯(lián)電阻與IC寄生引腳電容(通常為5至10 pF)配合使用,形成截止頻率低于1 GHz的單極點低通濾波器。這導致串聯(lián)電阻衰減大部分 ESD 事件的高頻能量(在 HBM 放電中高達 90% 的上升沿功率)。其次,當IC保護電路正常工作時,其阻抗非常低(在幾十歐姆或更低的量級)。這種低電阻與串聯(lián)電阻一起工作,形成分壓器,因此ESD事件產生的高電壓只能使IC內置保護電路偏置為總ESD電壓的一部分。這種衰減是對上升沿濾波的補充。這些影響的總和來自一個簡單的外部串聯(lián)電阻,在要求苛刻的應用中顯著提高了ESD性能。

最佳放置

如果要將TVS二極管和串聯(lián)電阻作為ESD保護添加到CMOS I/O引腳(例如微控制器上的GPIO引腳),則最好先放置串聯(lián)電阻(更接近ESD事件的源),然后再放置TVS二極管(更靠近微控制器)。

這是允許的,因為電阻不會受到ESD的損壞,并且可以消耗大部分功率,僅留下部分用于TVS二極管,這意味著CMOS I/O引腳上的電壓不會像其他方式那樣變化。

上拉/下拉問題

串聯(lián)電阻的一個問題是,當與上拉或下拉電阻配合使用時,它們可能會導致問題。上拉/下拉電阻在CMOS I/O輸出上很常見,這些輸出具有集電極開路(更常見的選擇)或發(fā)射極開路配置。問題在于,在特定情況下,ESD/限流串聯(lián)電阻和上拉/下拉電阻將形成分壓器。

檢查輸入的最大數(shù)字低電平和最小數(shù)字高電壓電平。如果它們仍然得到滿足,那么您不必擔心。

總結

電子產品的接口防護需用過壓保護器件,很多工程師意識到要用保護器件,但由于選型不當或沒按照ESD電路PCB設計原則,造成產品靜電測試或EMC測試不通過,產品多次驗證測試,浪費人力財力,造成產品延遲上市的事情總有發(fā)生,或過度設計,造成成本壓力。

雷卯電子專業(yè)為客戶提供電磁兼容EMC的設計服務,提供實驗室做摸底測試,從客戶高效,控本方便完成設計,希望為更多的客戶能快速通過EMC的項目,提高產品可靠性盡力。

雷卯電子電磁兼容實驗室,提供免費測試,提供外圍靜電保護參考電路。

-

保護器

+關注

關注

6文章

968瀏覽量

33266

發(fā)布評論請先 登錄

相關推薦

浪涌保護器的作用和特點

繼電保護器的種類及其優(yōu)缺點

Nexperia全新ESD保護器件如何保護汽車電路板

TPD5E003 5通道節(jié)省空間靜電放電(ESD)保護器件數(shù)據(jù)表

TPD2E1B06雙通道高速靜電放電(ESD)保護器件數(shù)據(jù)表

靜電放電保護器件種類與特點

靜電放電保護器件種類與特點

評論