在有源晶振,也就是石英振蕩器技術(shù)手冊(cè)中,CMOS模式是較為常見(jiàn)的一種輸出,屬于電壓控制形式,用來(lái)驅(qū)動(dòng)邏輯電平輸入。CMOS是TTL輸出模式的改進(jìn)方案,相比以往的TTL,CMOS輸出模式具有傳輸延遲時(shí)間慢,功耗較低,噪聲容限大等優(yōu)點(diǎn)。

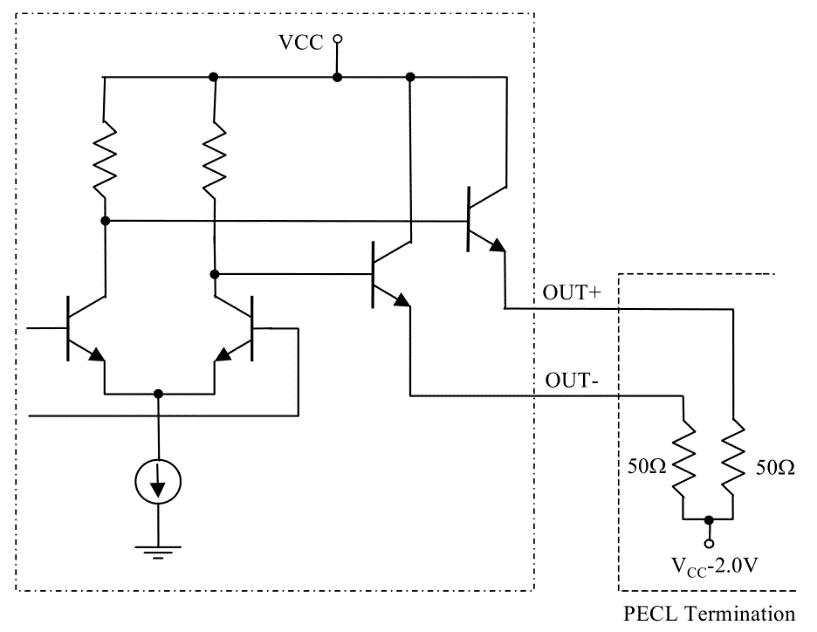

差分晶振我們常見(jiàn)的輸出模式有LVDS,LVPECL,HCSL,CML。那么LVCMOS屬于差分晶振的輸出模式嗎?

? 答案是否定的,LV代表極底電壓(Low-Voltage),對(duì)應(yīng)的另外一種輸出模式為HCMOS(Higt)高電壓。石英振蕩器中的額定電壓有1.8V,2.5V,2.8V,3.3V,5.0V。其中1.8V,2.5V,2.8V,3.3V屬于LVCMOS;5.0V屬于HCMOS。

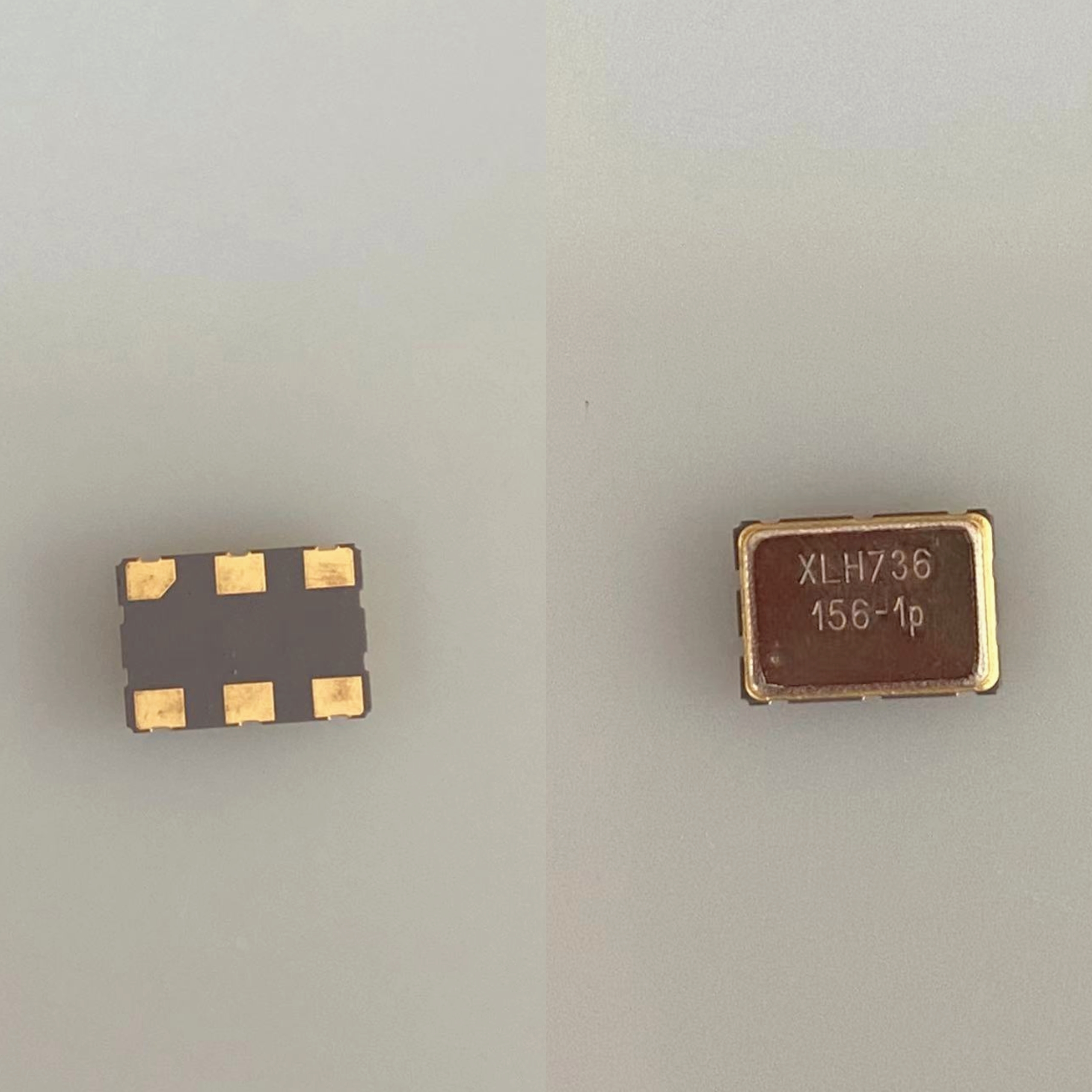

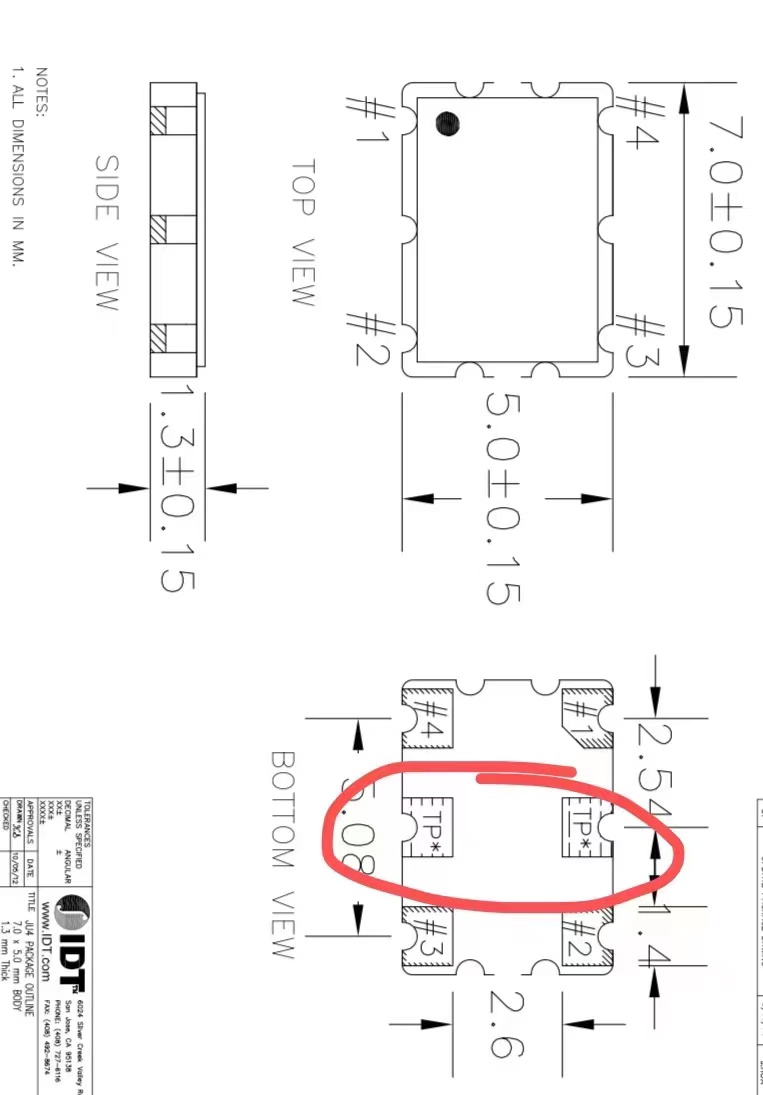

了解差分晶振的人清楚他的常用頻點(diǎn)通常是100M,125M,148M,156.25M,150M,200M,差分晶振的腳位一定是6個(gè),有一種迷幻現(xiàn)象即為晶振頻率為156.25MHZ,晶振腳位為6腳,輸出模式為L(zhǎng)VCMOS。

如果在你還沒(méi)有搞清楚LVCMOS的概念,你一定自信的以為這是一款差分晶振,實(shí)則上當(dāng)你看懂其中兩個(gè)腳位為空腳,LVCMOS也只是低電壓輸出模式的時(shí)候,你就能輕松判定這是一款普通的有源晶振。

-

晶振

+關(guān)注

關(guān)注

33文章

2728瀏覽量

67505 -

差分晶振

+關(guān)注

關(guān)注

0文章

78瀏覽量

97

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

差分晶振常用輸出模式、優(yōu)勢(shì)及應(yīng)用

差分晶振電氣參數(shù)簡(jiǎn)介

差分晶振在AI服務(wù)器中的應(yīng)用案例

差分晶振電路圖如何制作 影響差分晶振價(jià)格的原因

差分晶振的優(yōu)點(diǎn) 差分晶振在電子產(chǎn)品中的實(shí)際作用

如何定制差分晶振應(yīng)用電路方案

差分晶振有LVCMOS輸出模式嗎

差分晶振有LVCMOS輸出模式嗎

評(píng)論