01LDO裕量及其對輸出噪聲和PSRR 的影響

基于深亞微米工藝的最新千兆級模擬電路對電源電壓的要求越來越低,在有些情況下,還不到1 V。這些高頻電路往往需要較大的供電電流,因此,可能在散熱方面存在困難。設計目標之一是使功耗降至電路性能絕對需要的水平。

開關模式DC-DC轉換器是高效的電源,有些器件效率可超過95%,但其代價是電源噪聲,通常在較寬帶寬范圍內都存在噪聲問題。通常用低壓差線性調節器(LDO)清除供電軌中的噪聲,但也需要,在功耗和增加的系統熱負荷之間做出權衡。為了緩解這些問題,使用LDO 時,可使輸入和輸出電壓之間在較小的壓差(裕量電壓)本文旨在討論低裕量電壓對電源抑制和總輸出噪聲的影響。

02LDO電源抑制與裕量

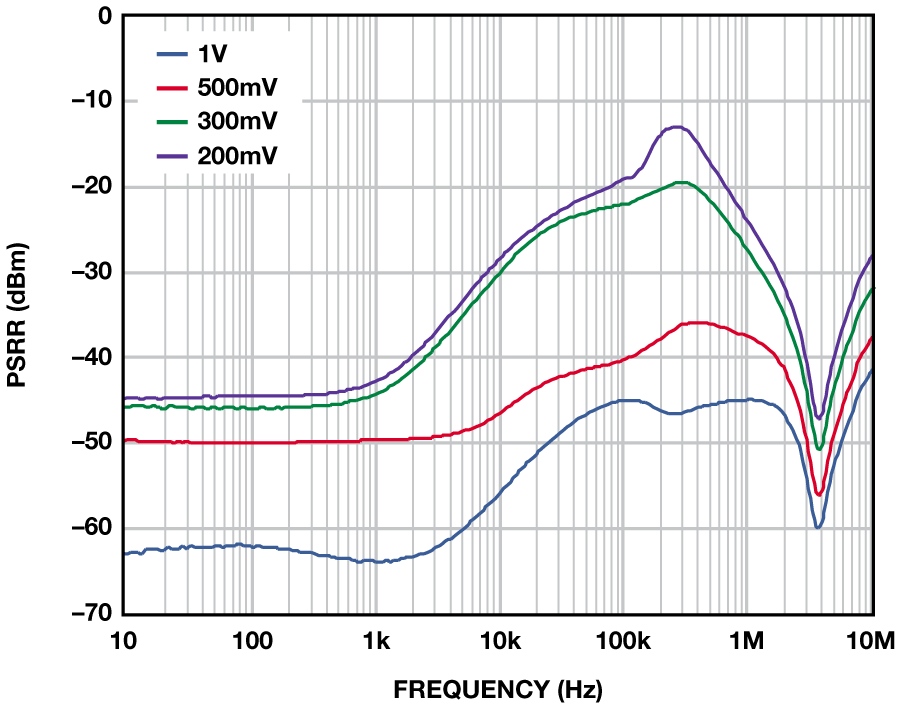

LDO 電源抑制比(PSRR)與裕量電壓相關——裕量電壓指輸入與輸出電壓之差。對于固定裕量電壓,PSRR隨著負載電流的提高而降低,大負載電流和小裕量電壓條件下尤其如此。圖1所示為ADM7160超低噪聲、2.5V線性調節器在200mA 負載電流和200mV、300mV、500mV 和1V 裕量電壓條件下的PSRR。隨著裕量電壓的減小,PSRR也會減小,壓差可能變得非常大。例如,在100kHz下,裕量電壓從1V 變為500 mV,結果將使PSRR減少5dB。然而,裕量電壓的較小變化,從500mV 變為300mV,結果會導致PSRR下降18dB 以上。

圖1. ADM7160 PSRR與裕量

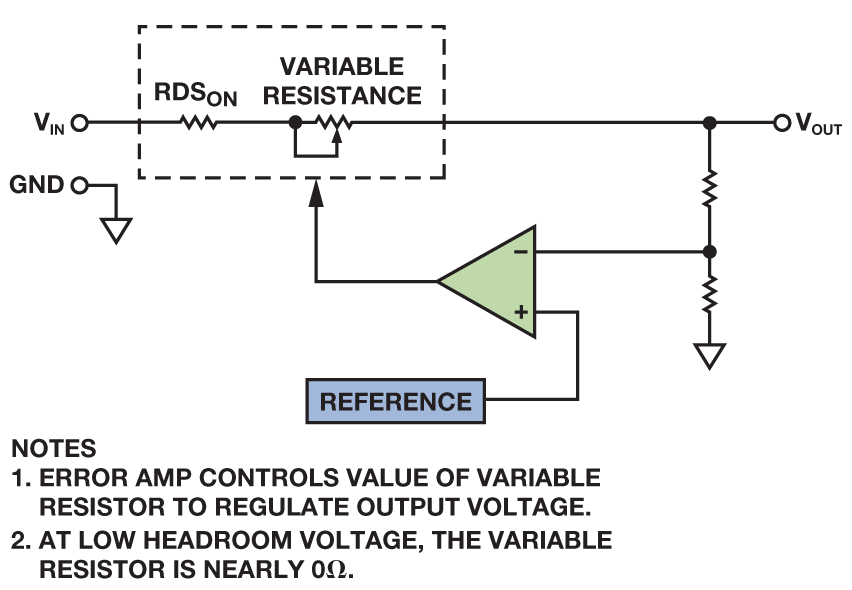

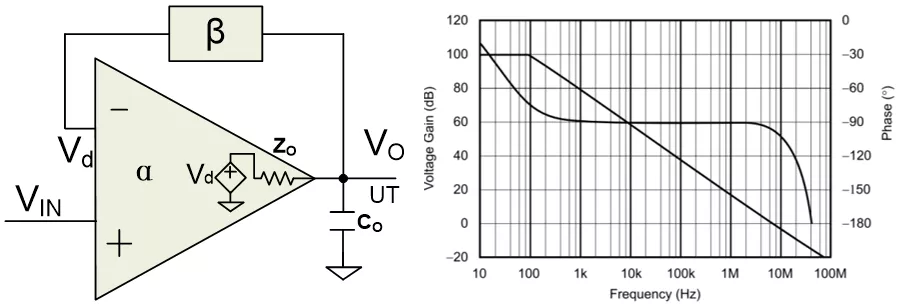

圖2 顯示了LDO 的框圖。隨著負載電流的增加,PMOS 調整元件的增益會減小,它脫離飽和狀態,進入三極工作區。結果使總環路增益減小,導致PSRR下降。裕量電壓越小,增益降幅越大。隨著裕量電壓繼續減小到一個點,此時,控制環路的增 益降至1,PSRR降至0dB。

導致環路增益減小的另一個因素是通路中元件的電阻,包括FET的導通電阻、片內互連電阻和焊線電阻。可以根據壓差推算出該電阻。例如,采用WLCSP封裝的ADM7160在200mA下的最大壓差為200mV。利用歐姆定律,調整元件的電阻約為1Ω,可以把調整元件近似地當作固定電阻與可變電阻之和。

流過該電阻的負載電流導致的壓差減去FET的漏極源極工作電壓。例如,在1 Ω FET條件下,200 mA的負載電流會使漏極源極電壓下降200 mV。在估算裕量為500 mV或1 V 的LDO的PSRR 時,必須考慮調整元件上的壓差,因為調整FET的工作電壓實際上只有300 mV或800 mV。

圖2. 低壓差調節器的框圖

03容差對LDO裕量的影響

客戶通常要求應用工程師幫助他們選擇合適的LDO,以便在負載電流Z 條件下從輸入電壓Y產生低噪聲電壓X,但在設置這些參數時,往往忽略了輸入和輸出電壓容差這個因素。隨著裕量電壓值變得越來越小,輸入和輸出電壓的容差可能對工作條件造成巨大的影響。輸入和輸出電壓的最差條件容差始終會導 致裕量電壓下降。例如,最差條件下的輸出電壓可能高1.5%,輸入電壓可能低3%。當通過一個3.8 V源驅動3.3 V的調節器時,最差條件裕量電壓為336.5 mV,遠低于預期值500 mV。在最差條件負載電流為200 mA的情況下,調整FET 的漏極源極電壓只有136.5 mV。在這種情況,ADM7160 PSRR可能遠遠低于標稱值55 dB(10 mA時)。

04壓差模式下的LDO的PSRR

客戶經常會就LDO在壓差模式下的PSRR請教應用工程師。開始時,這似乎是個合理的問題,但只要看看簡化的框圖,就知道這個問題毫無意義。當LDO工作于壓差模式時,調整FET 的可變電阻部分為零,輸出電壓等于輸入電壓與通過調整FET 的RDSON的負載電流導致的壓降之差。LDO不進行調節,而且沒有增益來抑制輸入端的噪聲;只是充當一個電阻。FET的RDSON與輸出電容一起形成一個RC濾波器,提供少量殘余PSRR,但一個簡單的電阻或鐵氧體磁珠即可完成同一任務,而且更加經濟高效。

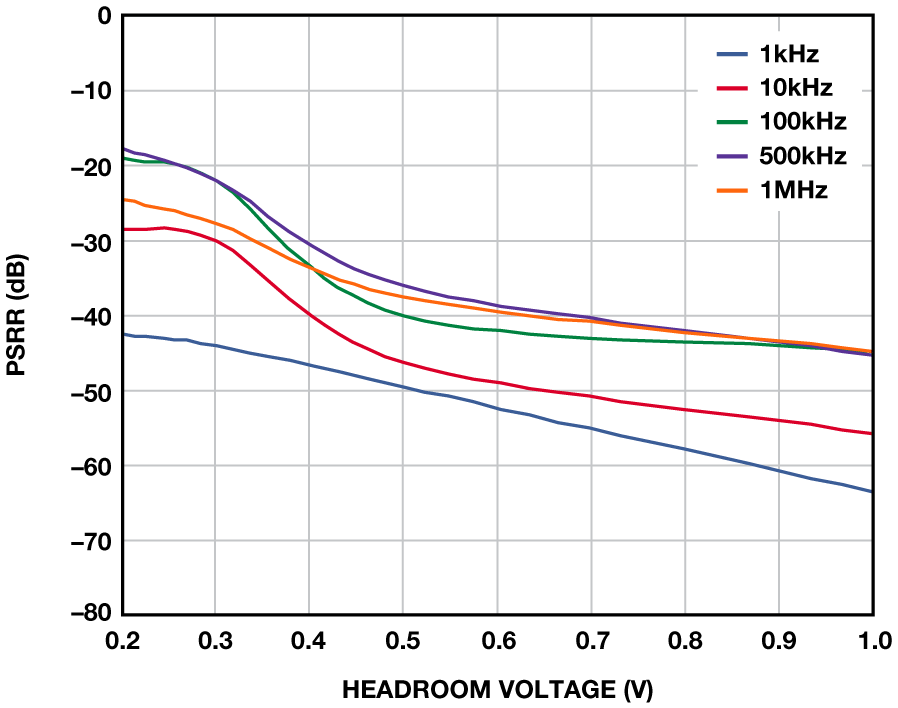

05在低裕量工作模式下維持性能

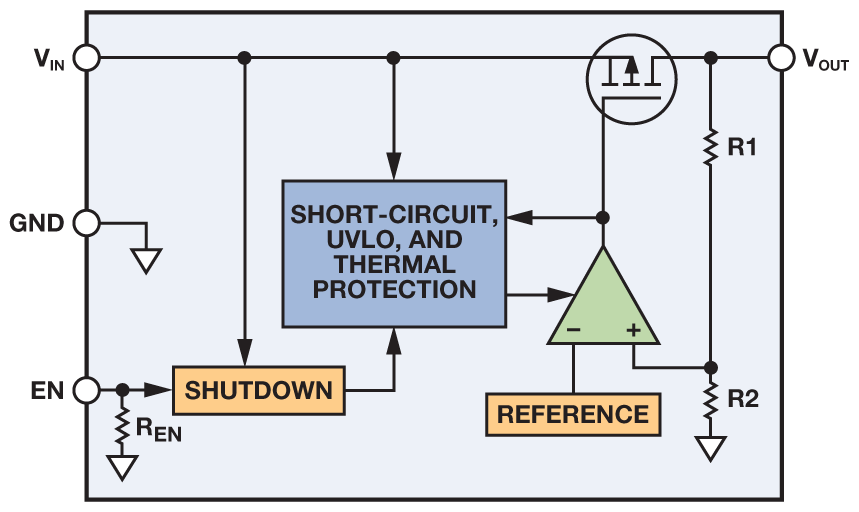

在低裕量工作模式下,需要考慮裕量電壓對PSRR的影響,否則,會導致輸出電壓噪聲水平高于預期。如圖3 所示的PSRR與裕量電壓關系曲線通常可在數據手冊中找到,而且可以用來確定給定條件下可以實現的噪聲抑制量。

圖3. PSRR與裕量電壓的關系

然而,有時候,通過展示LDO的PSRR如何有效濾除源電壓中的噪聲,可以更加容易地看到這種信息的利用價值。下面的曲線圖展示了LDO在不同裕量電壓下時,對總輸出噪聲的影響。

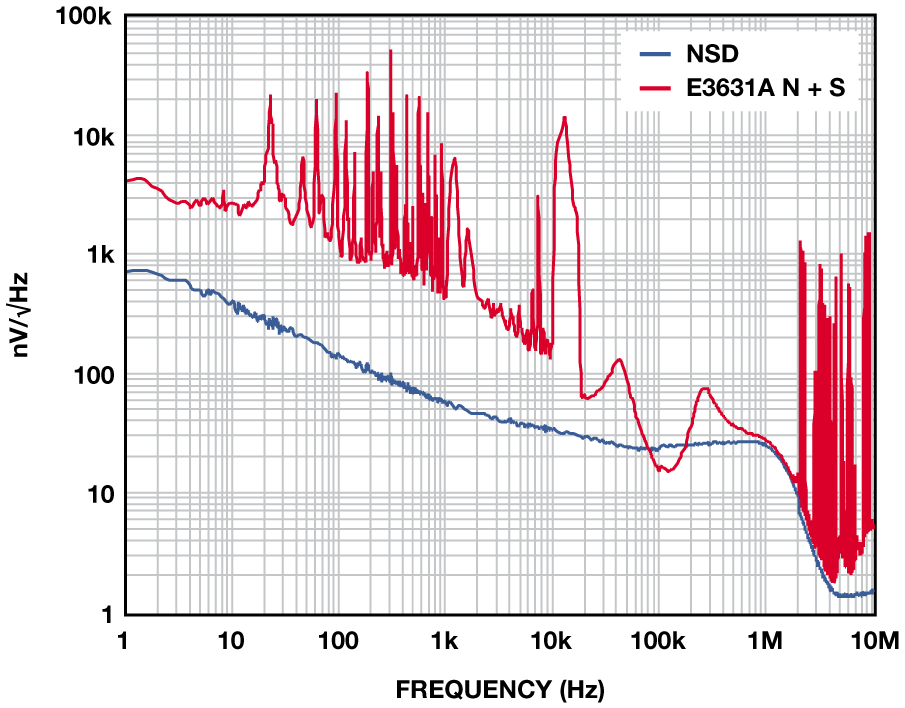

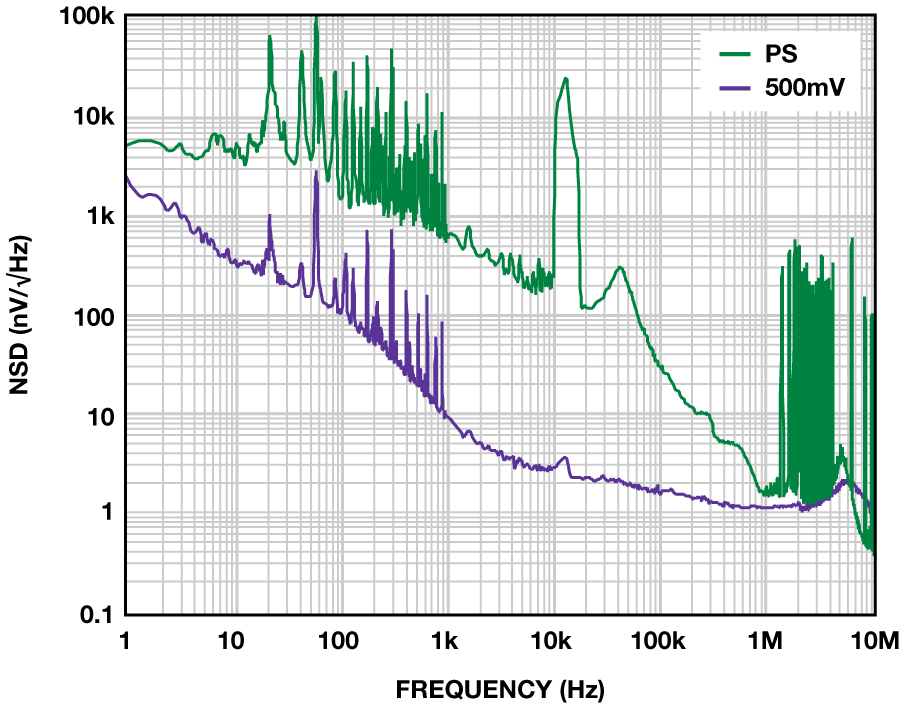

圖4 展示的是2.5 V ADM7160在500 mV裕量和100 mA負載條件下,相對于E3631A臺式電源的輸出噪聲,該臺式電源在20 Hz至20 MHz范圍內的額定噪聲低于350 μV-rms。1 kHz以下的許多雜散為與60 Hz線路頻率整流相關的諧波。10kHz以上的寬雜散來自產生最終輸出電壓的DC-DC轉換器。1 MHz以上的雜散源于環境中與電源噪聲不相關的RF 源。在10Hz至100kHz范圍內,這些測試所用電源的實測噪聲為56 μVrms,含雜散為104μV。LDO抑制電源上的所有噪聲,輸出噪聲約為9 μV-rms。

圖4. ADM7160噪聲頻譜密度(裕量為500 mV)

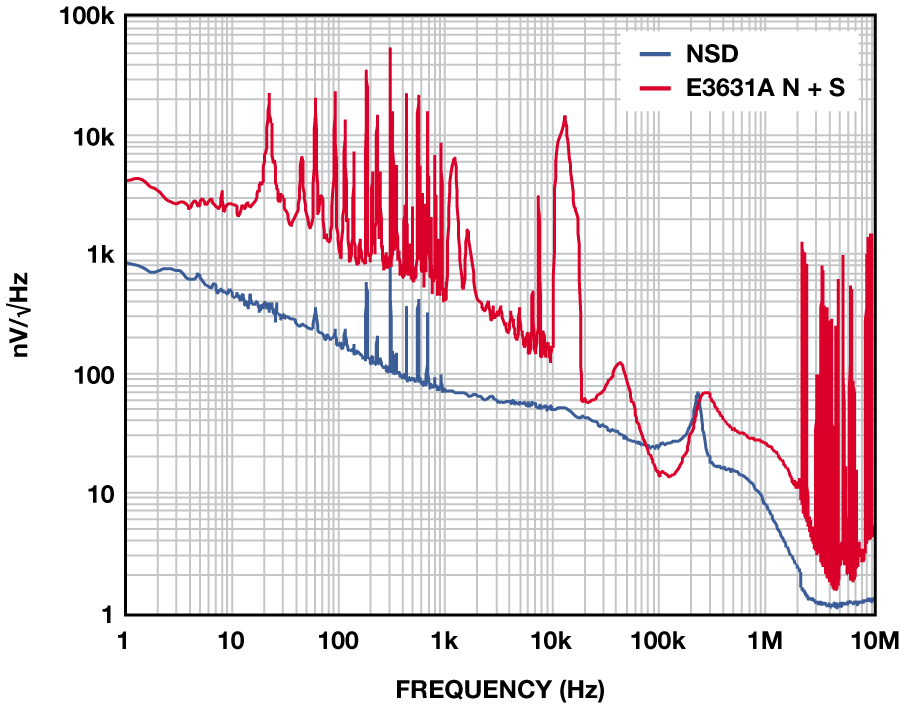

當裕量電壓降至200 mV時,隨著高頻PSRR接近0 dB,100 kHz以上的噪聲雜散開始穿過噪底。噪聲略升至10.8 μV rms。隨著裕量降至150 mV,整流諧波開始影響輸出噪聲,后者升至12μVrms。在大約250 kHz 處出現幅度適中的峰值,因而盡管總噪聲的增加量并不大,但敏感電路也可能受到不利影響。隨著裕量電壓進一步下降,性能受到影響,與整流相關的雜散開始在噪聲頻譜中顯現出來。圖5所示為100-mV裕量條件下的輸出。噪聲已上升至12.5 μV rms。諧波所含能量極少,因此,雜散噪聲只是略有增加,為12.7 μV rms。

圖5. ADM7160噪聲頻譜密度(裕量為100 mV)

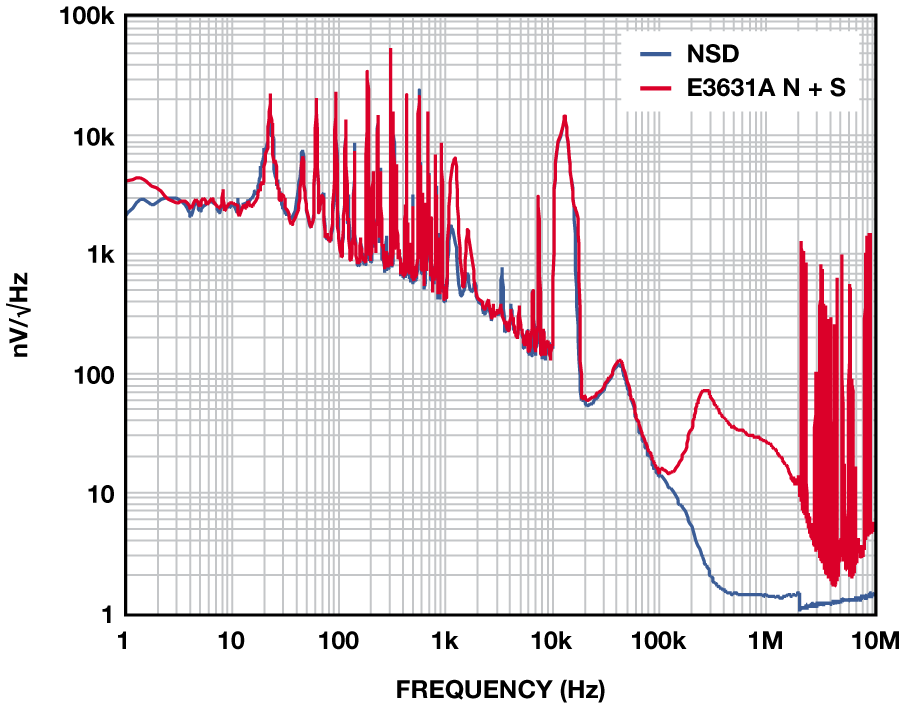

當裕量為75 mV時,輸出噪聲受到嚴重影響,整流諧波出現在整個頻譜中。Rms噪聲升至18 μV rms,噪聲與雜散之和升至27μV rms。超過~200 kHz范圍的噪聲被衰減,因為LDO環路無增益,充當一個無源RC濾波器。當裕量為65 mV時,ADM7160采用壓差工作模式。如圖6 所示,ADM7160的輸出電壓噪聲實際上與輸入噪聲相同。現在,rms噪聲為53 μVrms,噪聲與雜散之和為109 μV rms。超過~100 kHz 范圍的噪聲被衰減,因為LDO充當一個無源RC 濾波器。

圖6. ADM7160在壓差模式下的噪聲頻譜密度

06高PSRR、超低噪聲LDO

如ADM7150超低噪聲、高PSRR調節器一類的新型LDO實際上級聯了兩個LDO,因此,結果得到的PSRR約為各個級之和。這些LDO要求略高的裕量電壓,但能夠在1 MHz條件下實現超過60 dB的PSRR,較低頻率下,PSRR可以遠超100 dB。

圖7 所示為一個5 V的ADM7150的噪聲頻譜密度,其負載電流為500 mA,裕量為800 mV。10 Hz至100 kHz范圍內,輸出噪聲為2.2 μV rms。隨著裕量降至600 mV,整流諧波開始顯現,但當輸出噪聲升至2.3 μV rms時,其對噪聲的影響很小。

圖7. ADM7150噪聲頻譜密度(裕量為800 mV)

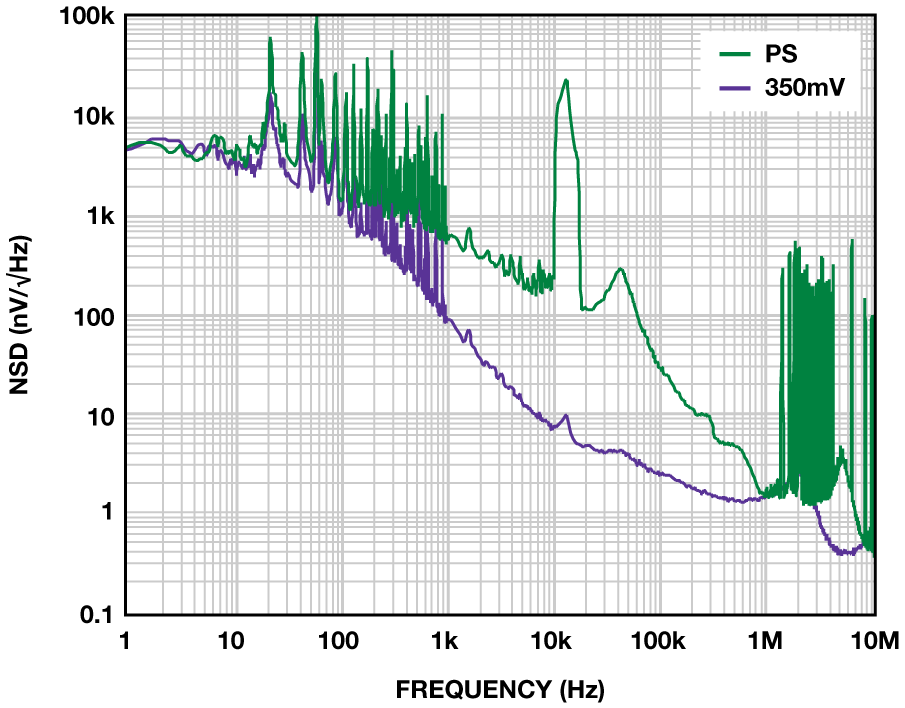

當裕量為500 mV時,可在12 kHz處明顯看到整流諧波和峰值,如圖8所示。輸出電壓噪聲升至3.9 μV rms。

圖8. ADM7150 噪聲頻譜密度(裕量為500 mV)

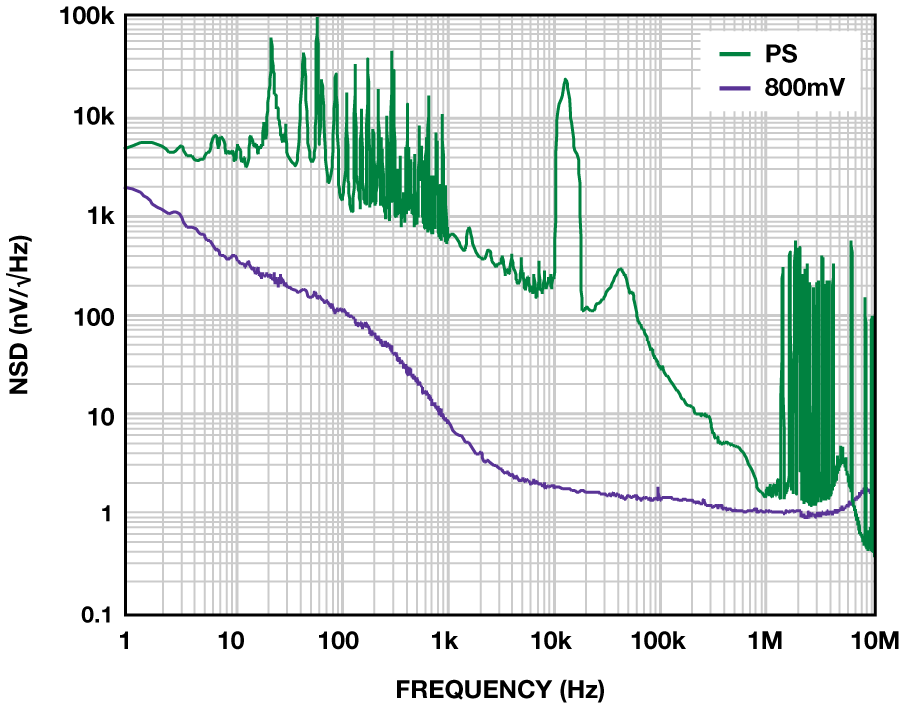

當裕量為350 mV時,LDO采用壓差工作模式。此時,LDO再也不能調節輸出電壓,充當一個電阻,輸出噪聲升至近76 μV rms,如圖9所示。只有FET的RDSON和輸出端的電容形成的極點衰減輸入噪聲。

圖9. ADM7150在壓差模式下的噪聲頻譜密度

07結論

現代LDO越來越多地用于清除供電軌中的噪聲,這些供電軌通常通過可以在較寬頻譜下產生噪聲的開關調節器實現。開關調節器以超高的效率形成這些電壓軌,但本身耗能的LDO既會減少噪聲,也會導致效率下降。因此,應盡量降低LDO的工作裕量電壓。

如前所述,LDO的PSRR為負載電流和裕量電壓的函數,會隨負載電流的增加或裕量電壓的減少而減少,因為,在調整管的工作點從飽和工作區移至三極工作區時,環路增益會下降。

通過考慮輸入源噪聲特性、PSRR 和最差條件容差,設計師可以優化功耗和輸出噪聲,為敏感型模擬電路打造出高效的低噪聲 電源。

在裕量電壓超低的條件下,輸入和輸出電壓的最差條件容差可能對PSRR形成影響。在設計時充分考慮最差條件容差可以確保可靠的設計,否則設計的具有較低的PSRR的電源解決方案,其總噪聲也會高于預期。

原文轉自亞德諾半導體

-

ldo

+關注

關注

35文章

1919瀏覽量

153190

發布評論請先 登錄

相關推薦

LDO線性電源轉換芯片-LDO14005

LDO穩壓器的負載瞬態響應特性

LDO的輸出電流和負載電流有什么區別

電源輸入電壓范圍裕量太小導致的設備運行故障

先積新品發布 ▏3A 低輸入電壓,低噪聲LDO--LTP7293

超小型、低輸入電壓、低RON負載開關TPS22908數據表

超小型、低輸入電壓、低rON負載開關TPS22934數據表

ROHM開發出一款采用高速負載響應技術QuiCur?的45V耐壓LDO穩壓器

【世說設計】LDO的運行困境:低裕量和最小負載

【世說設計】LDO的運行困境:低裕量和最小負載

評論