EDMA簡介

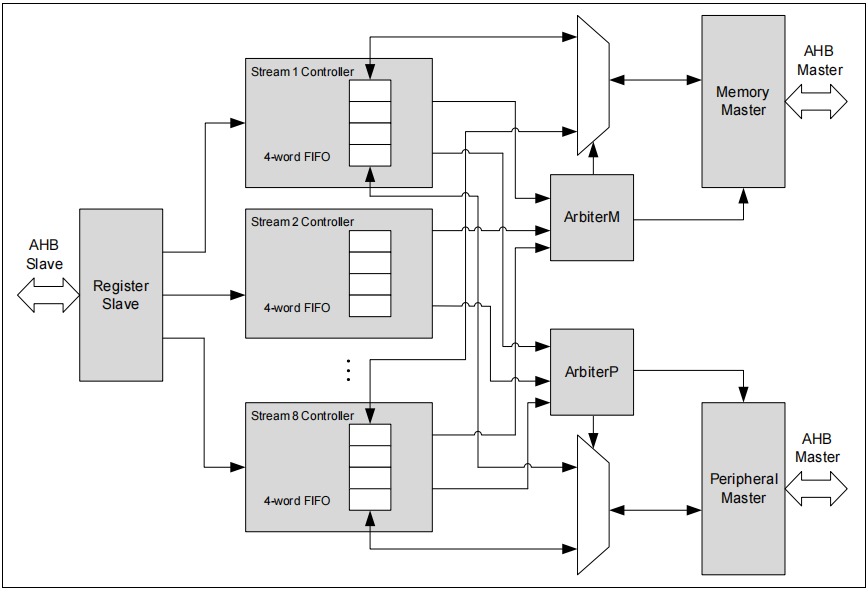

EDMA控制器的作用不僅在增強系統性能并減少處理器的中斷生成,而且還針對32位MCU應用程序專門優化設計。EDMA控制器為存儲器到存儲器,存儲器到外設和外設到存儲器的傳輸提供了八個數據流通道。每個通道都支持外設的DMA請求映射到任意數據流上、數據的打包與拆包、FIFO開啟與關閉、burst數據傳輸模式、存儲器端的雙buffer模式、可配置數據鏈傳輸、二維傳輸功能。基于復雜的總線矩陣架構,將功能強大的雙AHB總線架構與獨立的FIFO結合在一起,優化了系統的帶寬。圖1. EDMA控制器架構

DMAMUX簡介

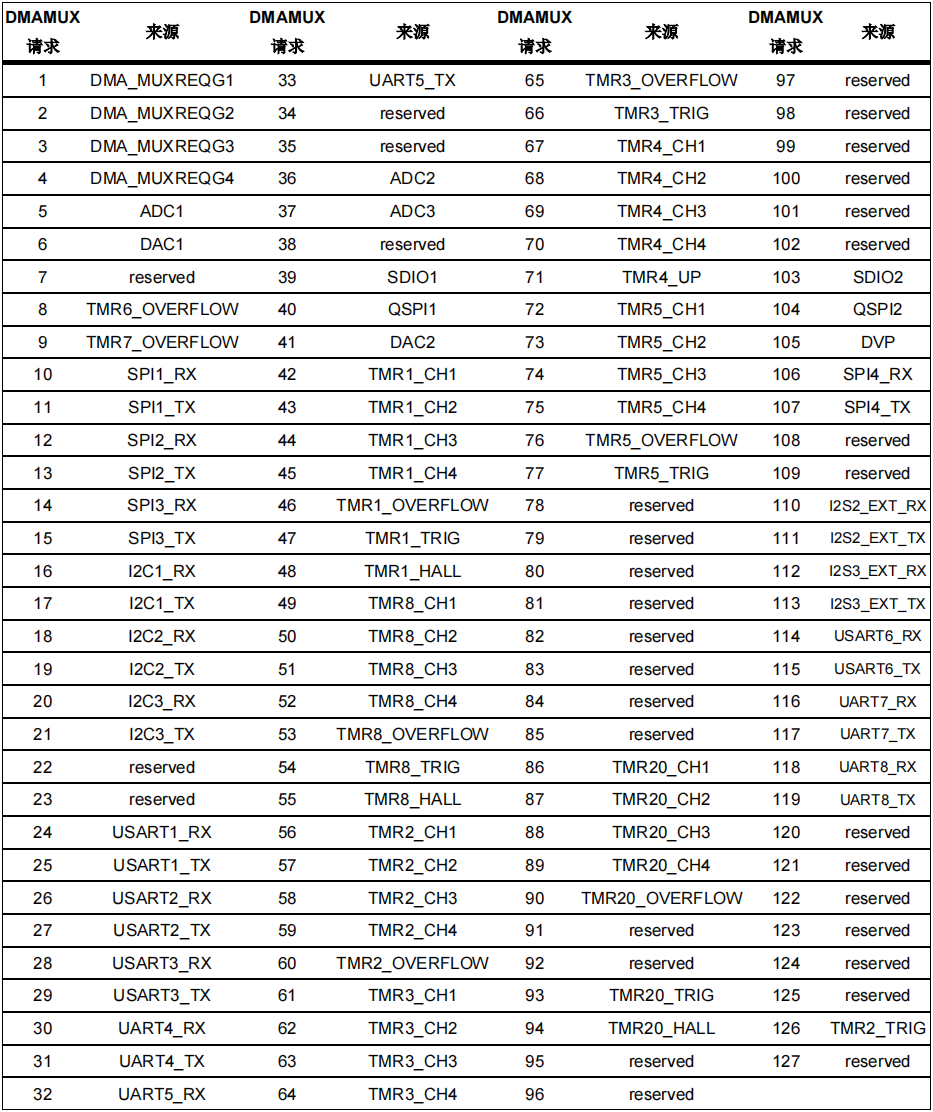

對于如何將外設的DMA請求映射到任意的數據流通道上,就需要使用到DMAMUX。DMAMUX針對每個外設都設計了獨有的ID號,使用者只需要將此ID號寫入對應的寄存器中并打開DMAMUX功能即可。DMAMUX的引入,使得EDMA相較于傳統DMA控制器變得更加靈活,使用者可以隨意的分配8個數據流通道的使用情況,不必再糾結與某個IP的DMA請求只能固定使用在某個或某幾個通道上。

各IP對應ID號如下表:

表1. 各IP對應ID號列表 注:表格中“DMAMUX請求”為ID號;“來源”為各IP的DMA請求。

注:表格中“DMAMUX請求”為ID號;“來源”為各IP的DMA請求。

EDMA功能解析

基本配置

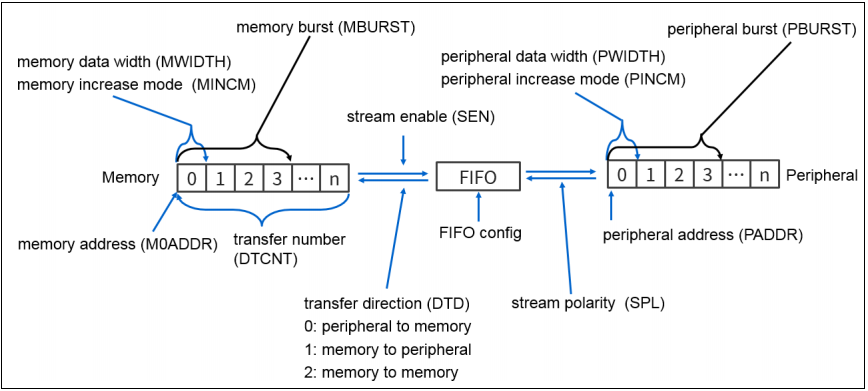

圖2. EDMA基本參數配置 EDMA傳輸所需要的基本參數配置如上圖所示,列舉如下內存端口― 地址(M0ADDR)― 數據寬度(MWIDTH):8位、16位、32位― 地址地址模式(MINCM):固定、遞增― 突發傳輸(MBURST):單次(1)、4、8、16節拍外設端口― 地址(PADDR)― 數據寬度(PWIDTH):8位、16位、32位― 地址地址模式(PINCM):固定、遞增― 突發傳輸(PBURST):單次(1)、4、8、16節拍其他― 傳輸方向(DTD):外設到內存、內存到外設、內存到內存― 通道優先級(SPL):低、中、高、非常高― 數據傳輸個數(DTCNT):范圍1~65535― FIFO配置― 流使能(SEN)

EDMA傳輸所需要的基本參數配置如上圖所示,列舉如下內存端口― 地址(M0ADDR)― 數據寬度(MWIDTH):8位、16位、32位― 地址地址模式(MINCM):固定、遞增― 突發傳輸(MBURST):單次(1)、4、8、16節拍外設端口― 地址(PADDR)― 數據寬度(PWIDTH):8位、16位、32位― 地址地址模式(PINCM):固定、遞增― 突發傳輸(PBURST):單次(1)、4、8、16節拍其他― 傳輸方向(DTD):外設到內存、內存到外設、內存到內存― 通道優先級(SPL):低、中、高、非常高― 數據傳輸個數(DTCNT):范圍1~65535― FIFO配置― 流使能(SEN)

FIFO功能

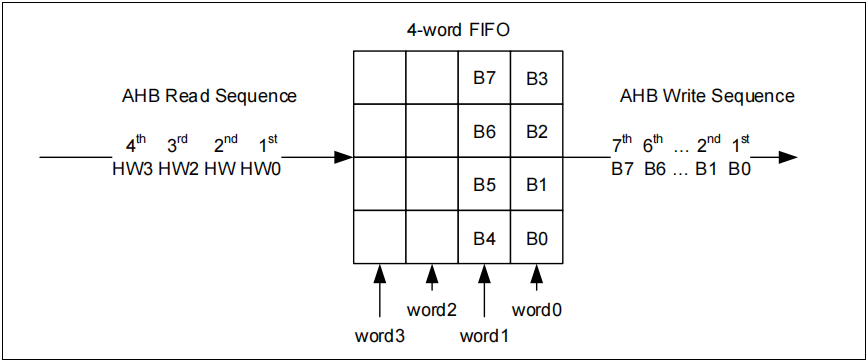

1、功能介紹EDMA控制器每個數據流都擁有獨立的4 word fifo,這使得EDMA傳輸變得更加靈活,所傳輸的數據在FIFO內可進行打包與拆包操作,不再限制源與目標的數據總線寬度必須相等。在FIFO模式下,源和目標數據寬度可以通過SxCTRL寄存器PWIDTH與MWIDTH位配置(byte,halfword,word),且允許PWIDTH與MWIDTH不同。

當PWIDTH與MWIDTH不同時:

- EDMA要傳輸的數據寬度等于PWIDTH,例如PWIDTH=halfword,則需傳輸的數據量為SxDTCNT*2。

- EDMA控制器僅按照小字節序尋址源和目標。

FIFO模式下外設到內存傳輸邏輯

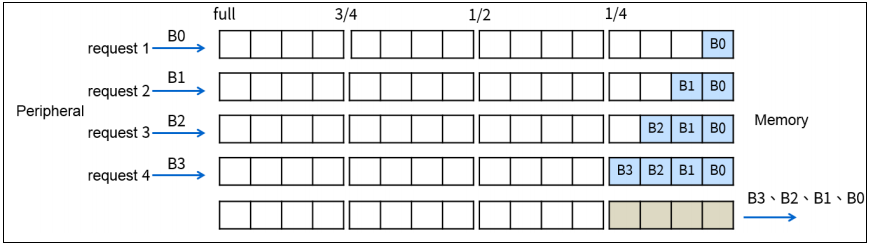

圖3. FIFO模式外設到內存傳輸 如上圖所示,例如FIFO閾值設置成1/4,外設和內存端數據都為字節。剛開始FIFO狀態為空,外設傳輸4筆數據后,FIFO狀態為1/4,此時達到FIFO閾值,一次傳輸4個字節到內存。

如上圖所示,例如FIFO閾值設置成1/4,外設和內存端數據都為字節。剛開始FIFO狀態為空,外設傳輸4筆數據后,FIFO狀態為1/4,此時達到FIFO閾值,一次傳輸4個字節到內存。

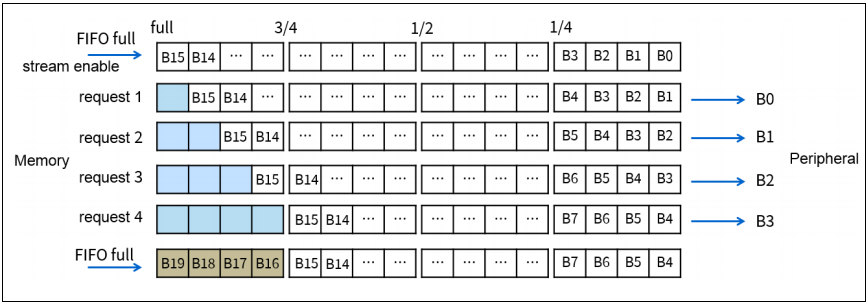

FIFO模式下內存到外設傳輸邏輯

圖4. FIFO模式內存到外設傳輸 如上圖所示,例如FIFO閾值設置成1/4,外設和內存端數據都為字節。剛開始FIFO狀態為空,當使能數據流后,立即從內存傳輸16個字節到FIFO,此時FIFO狀態為滿,然后外設傳輸4筆數據后,FIFO狀態為3/4,此時達到FIFO閾值,一次從內存傳輸4個字節到FIFO,再次填滿FIFO。

如上圖所示,例如FIFO閾值設置成1/4,外設和內存端數據都為字節。剛開始FIFO狀態為空,當使能數據流后,立即從內存傳輸16個字節到FIFO,此時FIFO狀態為滿,然后外設傳輸4筆數據后,FIFO狀態為3/4,此時達到FIFO閾值,一次從內存傳輸4個字節到FIFO,再次填滿FIFO。

FIFO模式下內存到內存傳輸邏輯

當使能數據流后,開始從源內存傳輸數據到FIFO,當達到FIFO閾值時,FIFO里的數據將被全部傳輸到目標內存,然后重復此步驟直到傳輸完成。在直接模式下(SxFCTRL內FEN=0),不可進行數據的打包與拆包。這種情況下,不允許源與目標的數據寬度不相等。數據寬度由PWIDTH定義,MWIDTH的設定無效。

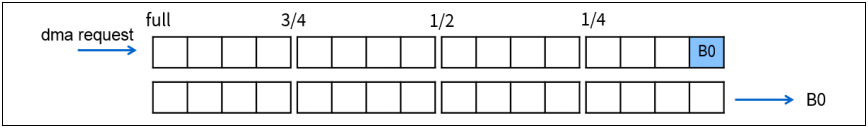

直接模式下外設到內存傳輸邏輯

圖5. 直接模式外設到內存傳輸 當產生DMA請求后,數據從外設傳輸到FIFO,然后FIFO內的數據將會立即傳輸到內存。

當產生DMA請求后,數據從外設傳輸到FIFO,然后FIFO內的數據將會立即傳輸到內存。

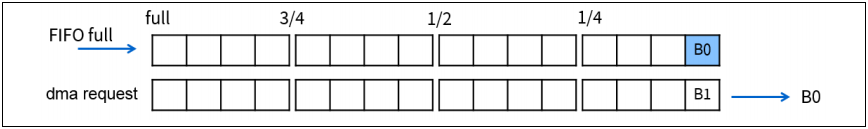

直接模式下內存到外設傳輸邏輯

圖6. 直接模式內存到外設傳輸 當使能數據流后,立即從內存傳輸一個數據到FIFO(數據大小由PWIDTH決定),當產生 DMA請求后,立即將數據從FIFO傳輸到外設,然后再次從內存傳輸一個數據到FIFO。

當使能數據流后,立即從內存傳輸一個數據到FIFO(數據大小由PWIDTH決定),當產生 DMA請求后,立即將數據從FIFO傳輸到外設,然后再次從內存傳輸一個數據到FIFO。

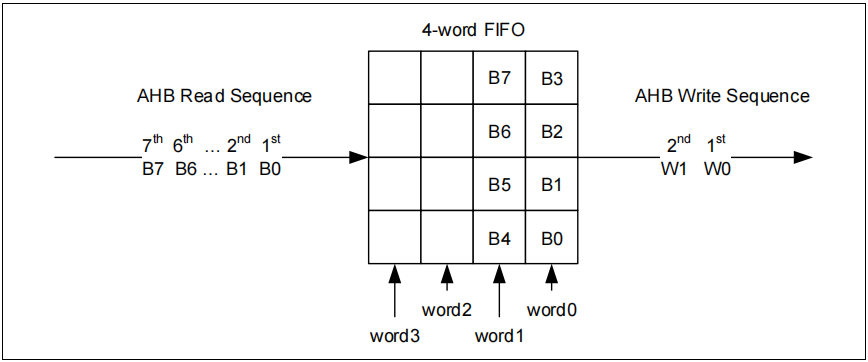

數據打包與拆包示意圖如下:

圖7. EDMA數據打包示意圖 圖8. EDMA數據拆包示意圖

圖8. EDMA數據拆包示意圖

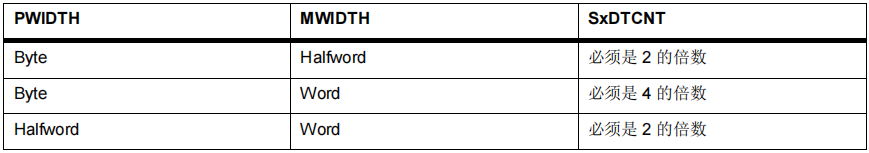

外設端口可以是源或者目標(在Memory to memory模式下,也可以是存儲器源),在使用FIFO時,一定要合理配置PWIDTH、MWIDTH和SxDTCNT,已確保數據傳輸的完整性,在PWIDTH小于MWIDTH時,需要按照如下條件配置:

表2. PWIDTH和MWIDTH與SxDTCNT的限制條件

FIFO可配置閾值級別,軟件可配置為1/4、1/2、3/4、滿這四種狀態(通過SxFCTRL寄存器FTHSEL配置),并且可通過SxFCTRL寄存器的FSTS位觀察FIFO當前狀態。

2、軟件接口設置FIFO的軟件接口包含在EDMA配置結構體內,以結構體成員的方式呈現,如下:

第一項為配置FIFO是否使能,當為TURE時,表示FIFO使能;當為FALSE時,表示FIFO禁止第二項為FIFO閾值設定,其選項可以是1/4、1/2、3/4和滿這四種狀態。

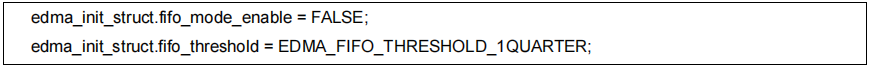

突發傳輸功能

功能介紹圖9. 突發傳輸示意圖 EDMA控制器可產生單次傳輸或4個、8個、16個節拍的突發傳輸。突發傳輸數量通過SxCTRL寄存器的PBURST與MBURST位設定。如上圖所示,傳輸方向為內存到外設,內存端MBURST=4,每一次數據傳輸,DMA都會從內存連續傳輸4個數據到FIFO(數據可以為字節、半字、字)。外設端PBURST=8,每一次數據傳輸,DMA都會從FIFO連續傳輸8個數據到外設(數據可以為字節、半字、字)。突發傳輸數量是按照節拍數來計算的,并非按照字節數計數,例如PBURST=4,PWIDTH=halfword,則一次突發傳輸的數據量為4*2bytes。突發傳輸只能在FIFO模式下才可使用;在直接模式下,數據流只能生成單次傳輸,而MBURST和PBURST位由硬件強制配置。

EDMA控制器可產生單次傳輸或4個、8個、16個節拍的突發傳輸。突發傳輸數量通過SxCTRL寄存器的PBURST與MBURST位設定。如上圖所示,傳輸方向為內存到外設,內存端MBURST=4,每一次數據傳輸,DMA都會從內存連續傳輸4個數據到FIFO(數據可以為字節、半字、字)。外設端PBURST=8,每一次數據傳輸,DMA都會從FIFO連續傳輸8個數據到外設(數據可以為字節、半字、字)。突發傳輸數量是按照節拍數來計算的,并非按照字節數計數,例如PBURST=4,PWIDTH=halfword,則一次突發傳輸的數據量為4*2bytes。突發傳輸只能在FIFO模式下才可使用;在直接模式下,數據流只能生成單次傳輸,而MBURST和PBURST位由硬件強制配置。

根據單次傳輸或突發傳輸的配置,每個DMA的請求在AHB外設端口上啟動相應配置下的數據量傳輸:

- 當AHB外設端口配置為單次傳輸時,根據PWIDTH配置的值,每次DMA請求傳輸一個byte、halfword或者word。

- 當AHB外設端口配置為突發傳輸時,根據PWIDTH配置的值,每次DMA請求傳輸4個、8個、16個byte、halfword或者word。

注:源和目的地址自增模式下,才可使用突發傳輸。

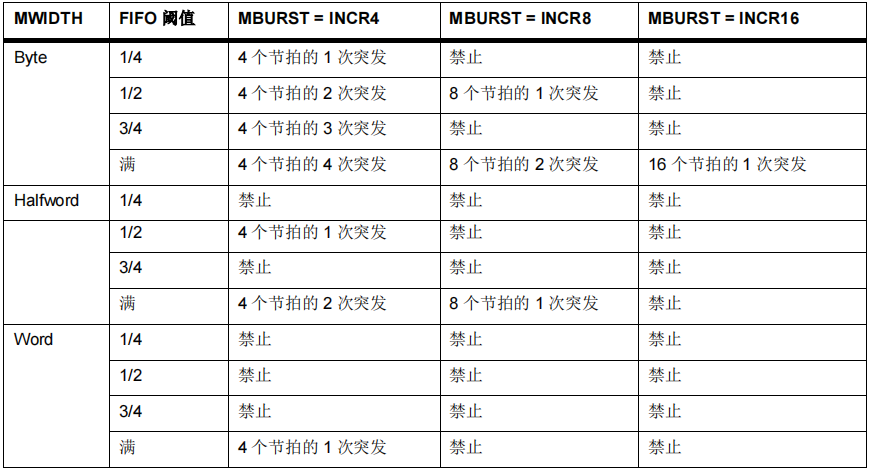

EDMA的FIFO閾值設定與存儲器突發傳輸大小需要滿足一定的關系才能正常啟動數據流,否則在啟動數據流時,就會產生FIFOerror,然后將禁止數據流。FIFO閾值設定與存儲器突發傳輸大小關系需滿足如下:

表3. MWIDTH與MBURST配置關系

從此表個可以得出結論:突發傳輸數據量與數據大小乘積不能超過FIFO閾值大小。

軟件接口設置突發傳輸軟件接口與設置FIFO類似,其被包含在EDMA配置結構體內,以結構體成員的方式呈現:

第一項為配置外設端口突發傳輸量;第二項為配置內存端口突發傳輸量。

注:在使用突發傳輸時,必須使能FIFO模式。

存儲器端雙緩存區功能

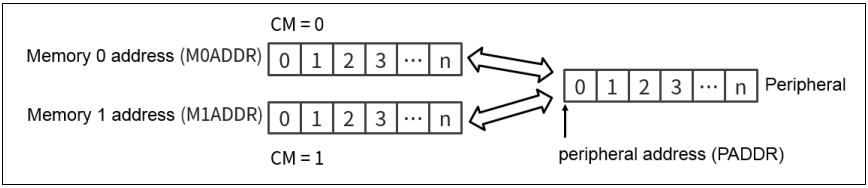

功能介紹圖10. 雙緩存區示意圖 通過設置SxCTRL寄存器的DMM位,即可使能雙緩存區功能。與常規(單緩存區)數據流工作模式相比,雙緩存區功能擁有兩個存儲器指針;啟動雙緩存區功能時,EDMA控制器的相應數據流通道會自動開啟循環模式,在每次SxDTCNT減到0時自動交換存儲區。

通過設置SxCTRL寄存器的DMM位,即可使能雙緩存區功能。與常規(單緩存區)數據流工作模式相比,雙緩存區功能擁有兩個存儲器指針;啟動雙緩存區功能時,EDMA控制器的相應數據流通道會自動開啟循環模式,在每次SxDTCNT減到0時自動交換存儲區。

根據SxCTRL寄存器的CM位,可知道數據流當前使用的存儲區是memory0/1。當CM=0,表示當前目標是memory0;當CM=1,表示當前目標為memory1。

在使用雙緩存區,需要注意以下幾點:

- 當硬件正在使用某一塊緩存時,當前緩存的基地址不可改變,即寄存器SxM0ADDR和

SxM1ADDR。例如數據流正在將數據填入SxM0ADDR時,那么軟件只能改變SxM1ADDR的基地址。可根據CM位的狀態,確定數據流當前操作的緩存區。

- 當使用雙緩存區功能時,禁止使用存儲器到存儲器模式。

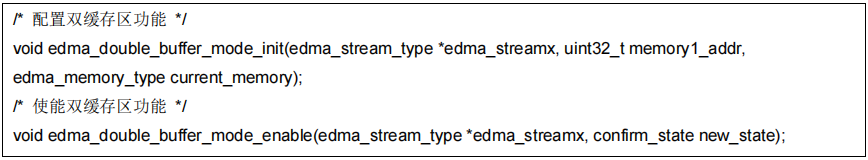

軟件接口對于雙緩存區功能,軟件實現了單獨的函數接口,如下:

對于雙緩存區功能,第一個緩存區地址會在EDMA初始化結構體中配置,即SxM0ADDR寄存器的配置。

在配置雙緩存區功能時,調用edma_double_buffer_mode_init();函數,此函數第一個參數表示當前配置雙緩存區的數據流,第二個參數為第二個緩存區的地址,第三個參數為啟動后硬件使用的緩存區。以上函數的調用,雙緩存區功能就配置好了,現在只需要調用 edma_double_buffer_mode_enable();函數開啟雙緩存區功能即可。

鏈接列表傳輸功能

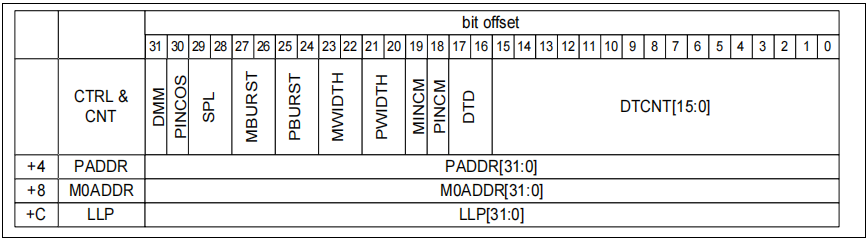

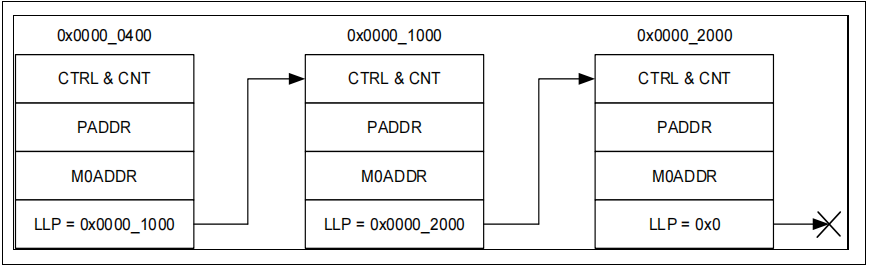

功能介紹鏈接列表傳輸可實現將幾塊不連續的存儲區的數據使用同一個數據流按照一定順序發送出去或者同一數據流接收到數據按照一定順序存儲在幾塊不連續的存儲區內。EDMA控制器如何知道數據存儲規則的呢?此規則是由軟件按照特定格式給出的,其格式如下圖所示:圖11. 鏈接描述符格式

將此格式成為鏈接描述符,此描述符存儲在片上存儲器中,當打開數據流時,EDMA 控制器從片上存儲器加載此描述符配置數據流,然后開啟數據的傳輸。

描述符分為4項:

- 數據流基礎配置和數據傳輸數量配置

- 外設基地址

- 存儲器基地址

- 下一個描述符的首地址

通過描述符的具體實現,最終實現一個單向鏈表結構,如下:圖12. 鏈接描述符鏈表結構

注:描述符在片上存儲地址必須要4 word對齊,否則不能正常啟動數據流。

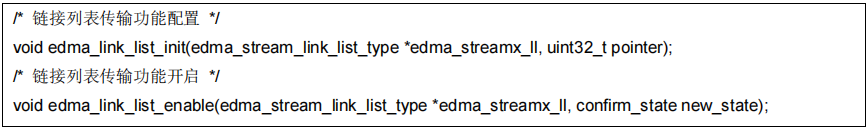

軟件接口對于鏈接列表傳輸功能,軟件單獨實現了函數接口,如下:

第一個函數是對鏈接列表傳輸功能的一些配置。參數有兩個,第一個參數表示所配置的數據流號,第二個參數表示鏈表描述符的首地址。

經過此函數的配置后,只需調用第二個函數即可開啟鏈表傳輸功能。

二維處理功能

功能介紹二維數據傳輸(2D)功能,使用者可以較為方便的對數據塊進行一些操作,提高對數據的處理效率,在圖像處理方面效果較為明顯。

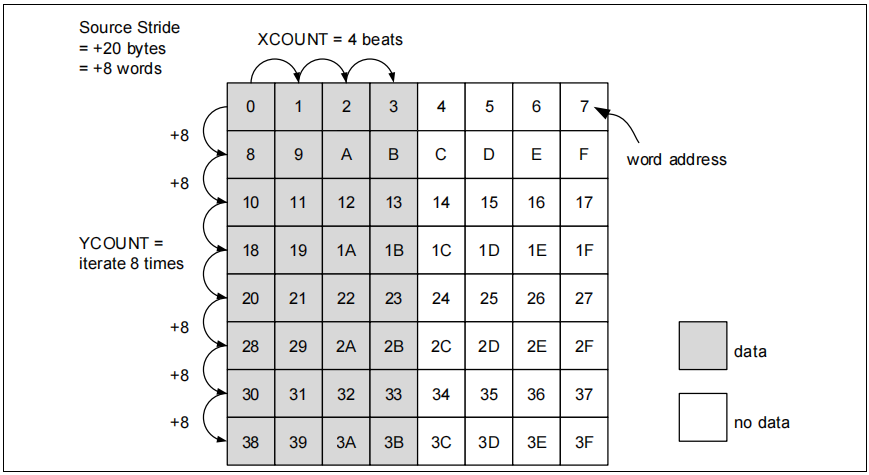

EDMA為二維數據傳輸(2D)提供了4個可配置的參數值:

- DMA_Sx2DCNT中的XCOUNT:跳轉到下一個跨步之前要傳輸的數據計數;

- DMA_Sx2DCNT中的YCOUTNT:迭代計數;

- DMA_Sx2DSTRIDE中的SRCSTD:源跨步值,該值應在源端迭代之前添加或減去;

- DMA_Sx2DSTRIDE中的DSTSTD:目的跨步值,該值應在目標端迭代之前添加或減

去。

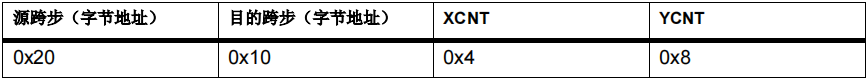

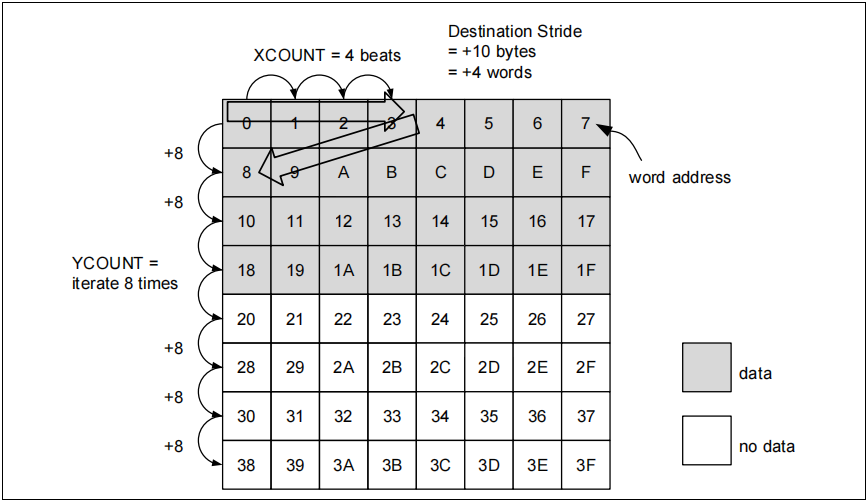

二維數據傳輸(2D)舉例:

表4. 2D傳輸舉例

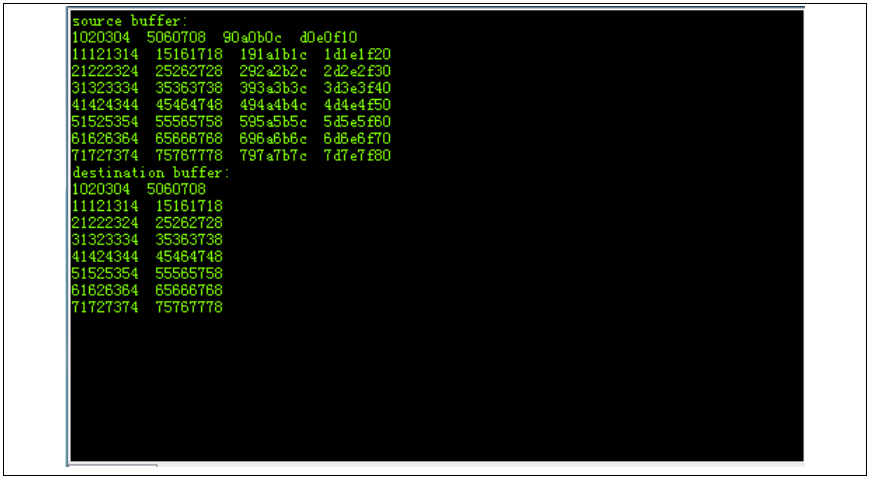

傳輸前數據在源存儲器中:

圖13. 2D傳輸前數據

傳輸后數據在目的存儲器中:

圖14. 2D傳輸后數據

圖4和圖5的陰影部分為真實數據。根據圖中可以清晰看到將數據看成二維的存儲在存儲器中,2D傳輸將此數據塊的左邊1/2的數據取走并存儲在新二維數據塊的上1/2處。

在使用二維傳輸時,有一些限制條件需要注意:

- 僅支持memory to memory傳輸

- PWIDTH和MISZE需要設置為0x2(字)

- 源和目標跨步值需與字對齊

- 源和目標跨步值均為二補數

- PINCM和MINCM均需設置為1(增量模式)

- PFCTRL需設置為0

- PINCOS需設置為0

- 不支持循環模式、雙緩沖模式

- 不支持鏈接列表傳輸

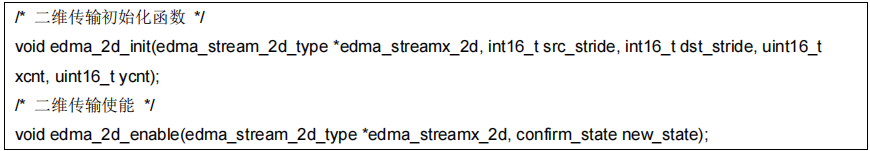

軟件接口對于二維數據傳輸功能,軟件單獨實現了接口函數,如下:

通過函數edma_2d_init(); 可以配置二維傳輸的源跨步、目的跨步、XCNT和YCNT,這四個參數的在使能2D傳輸前就需要配置好;然后調用函數edma_2d_enable();即可開啟二維傳輸功能。

EDMA配置解析

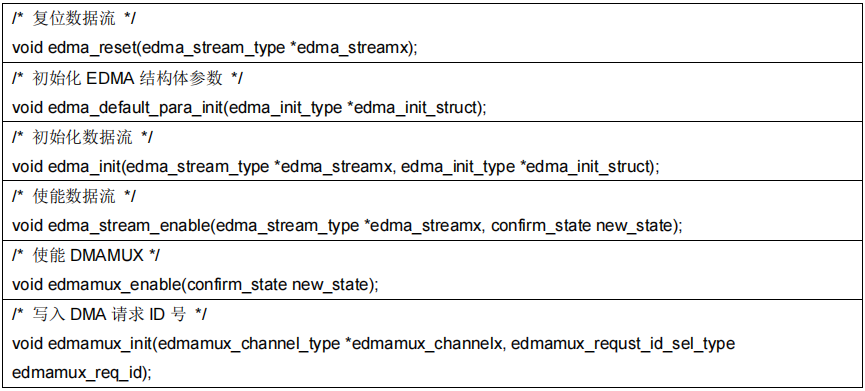

以下對EDMA的配置接口及流程進行說明。

函數接口

表5. 數據流配置函數列表

數據流配置

- 設置外設地址(SxPADDR寄存器)數據傳輸的初始外設地址,在傳輸過程中(SEN=1)不可被改變。

- 設置存儲器地址(SxM0ADDR寄存器)數據傳輸的初始內存地址,在傳輸過程中(SEN=1)不可被改變。

- 數據流配置(SxCTRL寄存器)包含優先級,數據傳輸方向、模式和寬度,地址增量模式、循環模式、雙緩沖模式和傳輸/半傳輸/傳輸錯誤中斷使能位。優先級(SPL)分為4個等級,最高優先級、高優先級、中等優先級和低優先級。若有2個流優先級設定相同,則較低編號的流有較高的優先權。舉例,流1優先于流2。數據傳輸方向(DTD)分為存儲器到外設(M2P),外設到存儲器(P2M)或存儲器到存儲器(M2M)傳輸。在存儲器到存儲器傳輸模式下不允許使用循環模式、雙緩沖模式和直接模式。數據傳輸寬度(PWIDTH/MWIDTH)根據實際使用情景,可配置寬度為byte、halfword、word;EDMA內部的打包、拆包機制允許PWIDTH與MWIDTH寬度不一致。地址增量模式(PINCM/MINCM)當流配置設定為增量模式時,下一筆傳輸的地址將是前一筆傳輸地址加上傳輸寬度(PWIDTH/MWIDTH)。數據傳輸模式(PBURST/MBURST)分為單次傳輸(SINGLE),或突發傳輸(BURST)。突發傳輸,在每個DMA請求到來后,根據配置傳輸4、8、16拍。在非增量模式下,設置突發傳輸會將4、8、16拍突發傳輸轉換為4、8或16個單次傳輸。在直接模式下,PBURST和MBURST位被硬件強制為0(單次傳輸)外設流控選擇(PFCTRL)若選擇外設做為流控制(PFCTRL=1),硬件會將DMA_SxDTCNT的值強制為0xFFFF,并由外設的dma_ch_lt信號指示數據傳輸結束。外設流控制不支持M2M模式和循環模式。循環模式(LM)當流配置設定為循環模式時,在最后一次傳輸后 SxDTCNT 寄存器的內容會恢復成初始值。雙緩存模式(DMM)當流配置設定為雙緩沖模式時,硬件會自動啟用循環模式。雙緩沖區流有兩個存儲器指針SxM0ADR/SxM1ADR,由CT位標示當前使用之存儲器指針,允許軟件在DMA填充/使用第二個存儲區的同時處理另一個存儲區。

- 直接模式與FIFO模式設定(SxFCTRL寄存器)包含FIFO閾值選擇,直接模式禁用和FIFO錯誤中斷使能位。FIFO閾值選擇(FTHSEL)分為1/4、2/4、3/4和全FIFO閾值;該設定僅在非直接模式下有效。FIFO模式使能(FEN)直接模式(FEN=0)僅可在P2M或M2P模式下使用,且外設/存儲器傳輸寬度需相等(MWIDTH=PWIDTH)并設定為單次傳輸(PBURST=MBURST=0)。如果選擇M2M模式,該位(FEN)被硬件強制為1。

- 使能DMAMUX(MUXSEL寄存器的TBL_SEL位)在非存儲器到存儲器(M2M)模式下時,需要使能 DMAMUX 功能,才能啟動數據流響應外設的DMA請求。

- 寫入外設ID號(MUXSxCTRL寄存器的REQSEL)在非存儲器到存儲器(M2M)模式下時,需要將外設的DMA請求ID號寫入,才能啟動數據流響應外設的DMA請求。

- 打開數據流(SxCTRL寄存器的SEN位)

配置流程

- 打開EDMA時鐘;

- 調用數據流復位函數復位數據流;

- 調用結構體初始化函數初始化數據流結構體;

- 調用初始化函數初始化數據流;

- 調用DMAMUX使能函數以及ID號寫入函數配置DMAMUX相關內容;

- 調用數據流使能函數開啟數據流。

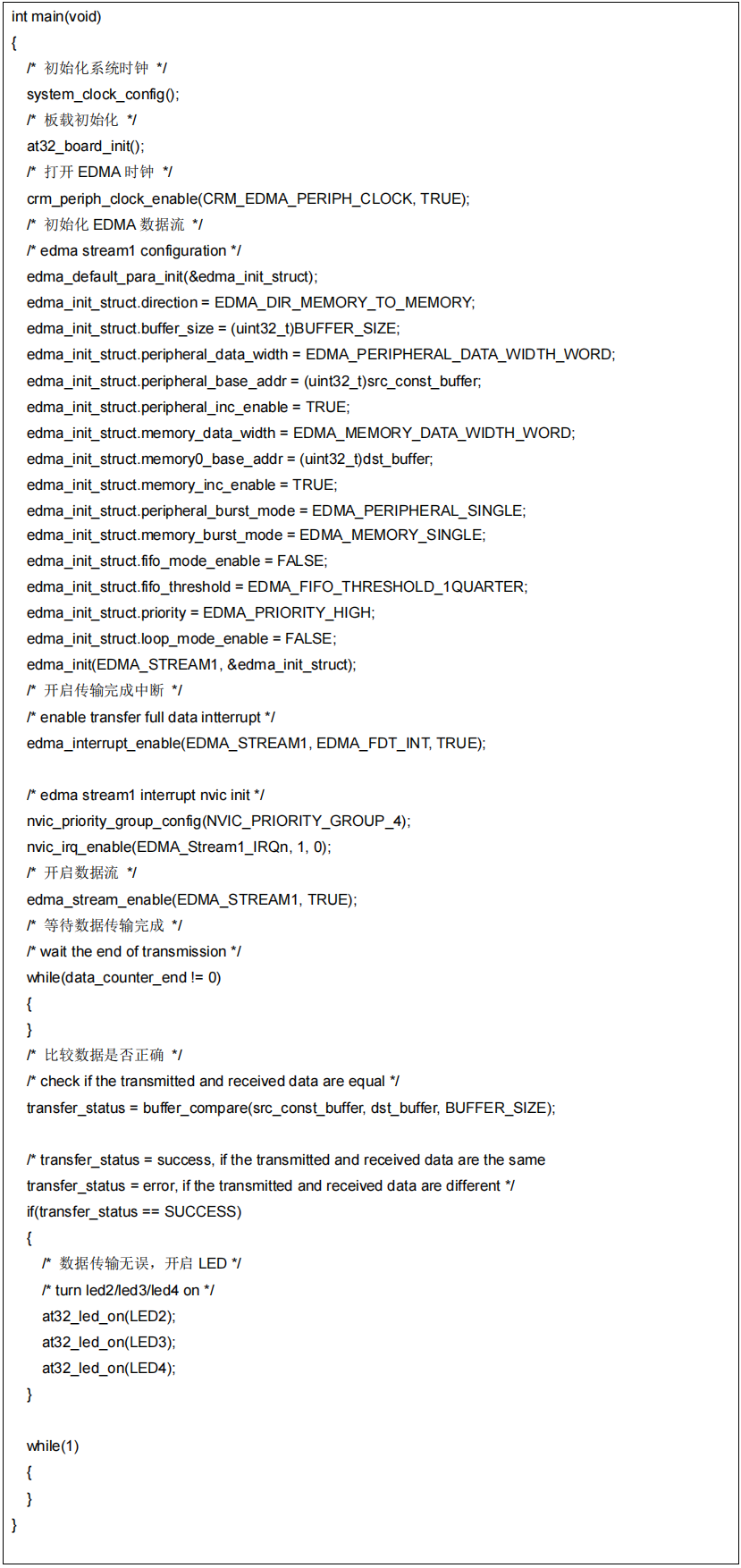

案例 數據從FLASH傳輸到SRAM

功能簡介

實現了使用EDMA將數據從片上FLASH搬運到內部SRAM中。

資源準備

1) 硬件環境:對應產品型號的AT-START BOARD2) 軟件環境project\at_start_f4xx\examples\edma\flash_to_sram

軟件設計

1) 配置流程

- 開啟EDMA外設時鐘

- 配置EDMA數據流

- 開啟傳輸完成中斷

- 開啟數據流

- 等待數據傳輸完成

- 比較數據傳輸是否正確

2)代碼介紹

- main函數代碼描述

- EDMA_Stream1_IRQHandler中斷函數代碼描述

實驗效果

- 如若數據傳輸無誤,LED2/3/4會點亮。

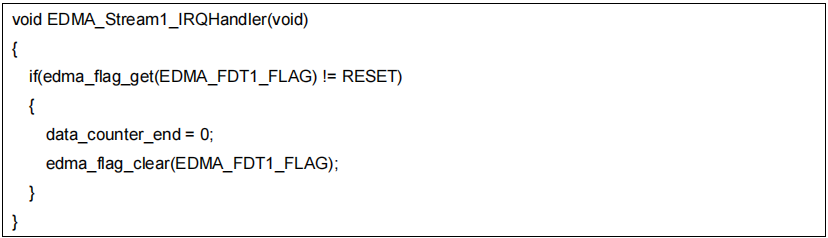

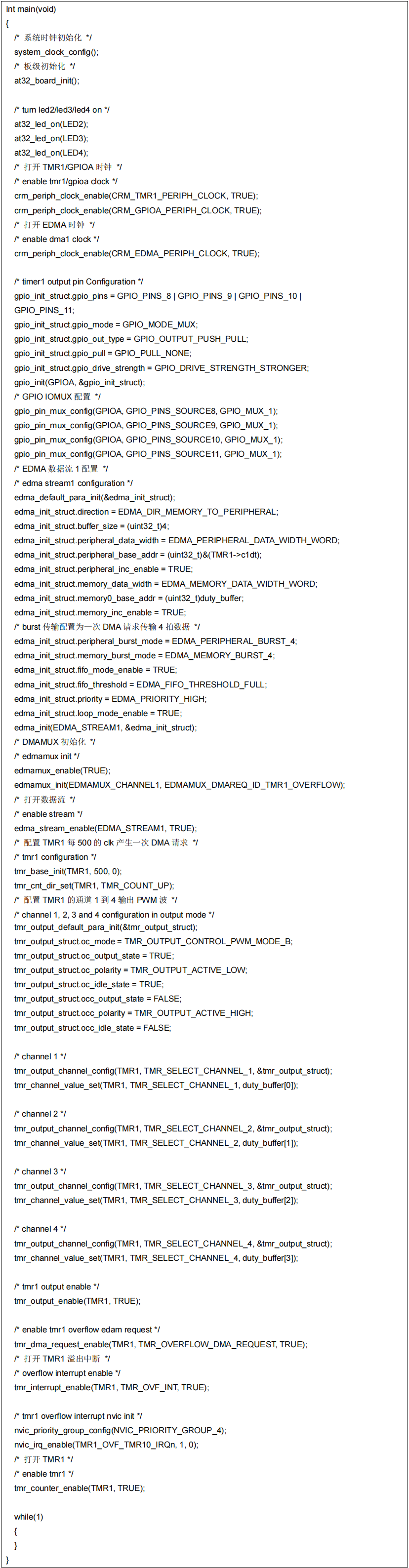

案例 EDMA突發傳輸

功能簡介

EDMA突發傳輸為EDMA控制器的特有功能。使用EDMA的突發傳輸將數據從SRAM傳輸到TMR1的c1dt至c4dt,實現同時改變TMR1四個通道占空比。

資源準備

1) 硬件環境:對應產品型號的AT-START BOARD2) 軟件環境project\at_start_f4xx\examples\edma\burst_mode

軟件設計

1) 配置流程

- 開啟EDMA/TMR1/GPIOA外設時鐘

- 配置EDMA數據流

- 配置TMR1的通道1到4輸出PWM波形

- 開啟傳輸完成中斷

- 開啟數據流

- 開啟TMR1,使其溢出中斷產生DMA請求

2) 代碼介紹

- main函數代碼描述

實驗效果

- TMR1的通道1到4每個周期會改變一次占空比。

如下為使用邏輯分析儀抓取的幾個通道的輸出波形,可以看到PWM波形的占空比每個周期都在改變。圖15. Burst傳輸實驗結果

案例 EDMA雙緩沖區

功能簡介

EDMA存儲器端雙緩存區為EDMA控制器的特有功能。本案例使用EDMA的雙緩存區功能將SRAM內部的兩塊數據通過IIS3傳輸給IIS2并存儲在SRAM內的另外兩個數據塊中。i2s3_buffer1_tx[32]和i2s3_buffer2_tx[32]為IIS3傳輸的兩塊數據,i2s2_buffer1_rx[32]和i2s2_buffer2_rx[32]為IIS2接收到的數據存儲區域。

資源準備

1) 硬件環境:對應產品型號的AT-START BOARD使用杜邦線將IIS3與IIS2連接起來,連接關系如下:PD0<------->PA4(ws)PD1<------->PC10(sck)PD4<------->PC12(sd)2) 軟件環境project\at_start_f4xx\examples\edma\i2s_halfduplex_edma_doublebuffer

軟件設計

1) 配置流程

- 開啟EDMA/IIS3/IIS2/GPIO外設時鐘

- 配置EDMA數據流,使能雙緩存區功能

- 配置IIS3/2

- 開啟傳輸完成中斷

- 開啟數據流

2) 代碼介紹

- 代碼描述

實驗效果

- LED2/3/4都點亮則表示數據傳輸正確。

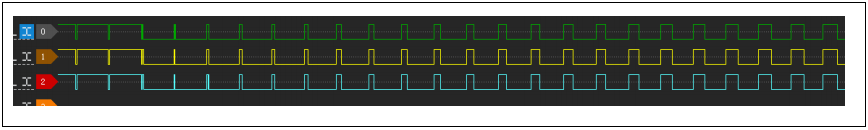

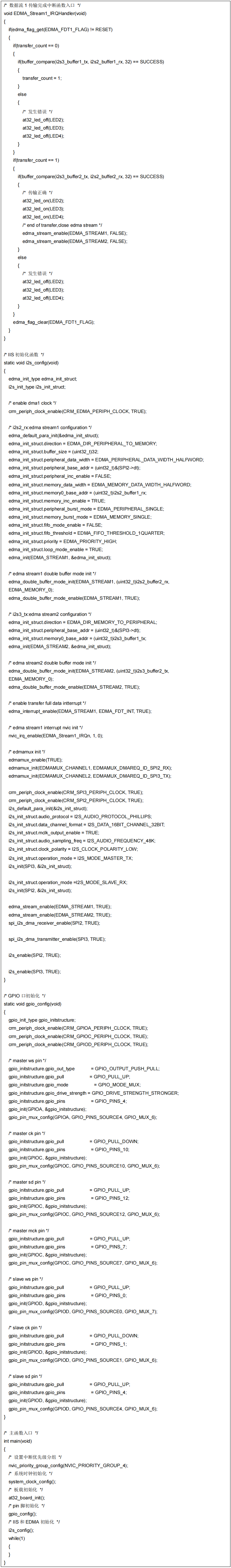

案例 EDMA鏈接列表傳輸

功能簡介

EDMA鏈接列表傳輸為EDMA控制器的特有功能。本案例使用EDMA的鏈接列表傳輸功能,將片上存儲器的3塊區域的數據通過EDMA發送給USART1,USART1在通過自身的TX引腳將數據發送出去。

資源準備

1) 硬件環境:對應產品型號的AT-START BOARD2) 軟件環境project\at_start_f4xx\examples\edma\link_list_mode

軟件設計

1) 配置流程

- 開啟EDMA/USART1/GPIO外設時鐘

- 配置EDMA數據流,使能鏈接列表傳輸功能

- 開啟傳輸完成中斷

- 開啟數據流

2) 代碼介紹

- 代碼描述

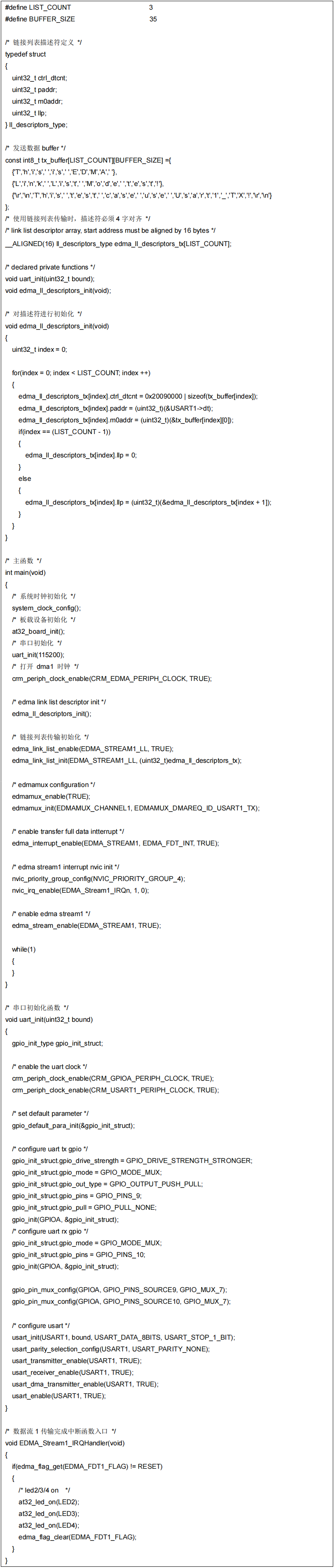

實驗效果

- LED2/3/4都點亮則表示數據傳輸完成,并可通過串口工具查看發送出來的數據。

串口工具接收的數據如下圖所示:圖16. 鏈接列表傳輸實驗結果

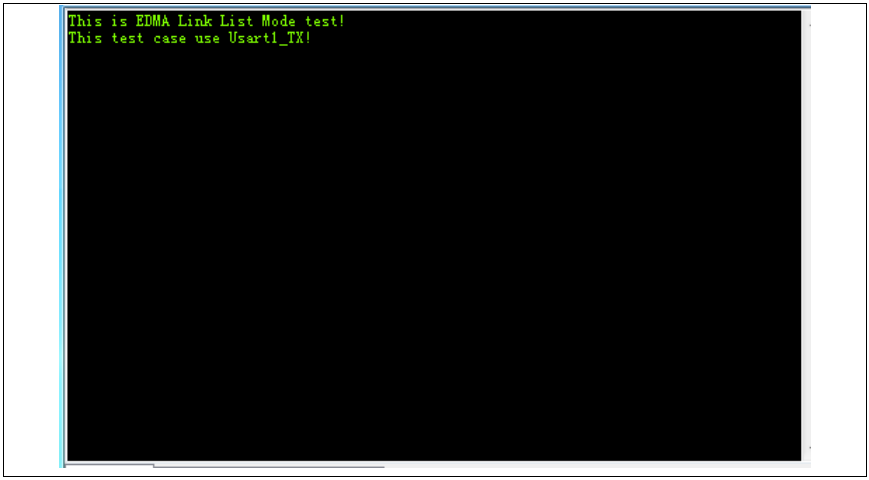

案例 EDMA二維傳輸

功能簡介

EDMA二維傳輸為EDMA控制器的特有功能。本案例使用EDMA的二維傳輸功能,將片上存儲器的1塊區域的數據通過EDMA二維傳輸功能剪裁出其左邊1/2,并通過串口打印出來。

資源準備

1) 硬件環境:對應產品型號的AT-START BOARD2) 軟件環境project\at_start_f4xx\examples\edma\two_dimension_mode

軟件設計

1) 配置流程

- 開啟EDMA/USART1/GPIO外設時鐘

- 配置EDMA數據流,使能二維傳輸功能

- 開啟傳輸完成中斷

- 開啟數據流

2) 代碼介紹

- 代碼描述

實驗效果

- 通過串口工具查看發送出來的數據。

串口工具接收的數據如下圖所示:圖17. 二維傳輸實驗結果

關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發與創新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業界最高主頻288MHz運算效能,并支持工業級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯網、消費、商務及工控等領域。

-

控制器

+關注

關注

112文章

16206瀏覽量

177436 -

EDMA

+關注

關注

0文章

19瀏覽量

9620

發布評論請先 登錄

相關推薦

TMS320C645X DSP從EDMA 2.0版遷移到EDMA 3.0版

從EDMA v2.0遷移到TMS320DM644X DMSoC的EDMA v3.0

自動發電控制系統具有三個基本功能

同步開關一對多功能講解及演示

CAN FD盒基本功能包括哪些

深度解析高速串行信號的誤碼測試|線上講堂

AT32講堂040 | AT32F435/437 EDMA基本功能講解和案列解析

AT32講堂040 | AT32F435/437 EDMA基本功能講解和案列解析

評論