防靜電和浪涌TVS layout設(shè)計要點

電子產(chǎn)品精密化

剛看過了CES2023,雷卯的外貿(mào)伙伴們看了最新的AR,VR,5G產(chǎn)品,新的電子產(chǎn)品更智能、更復(fù)雜,嵌入了脆弱和敏感的集成電路。這些設(shè)備的環(huán)境往往很惡劣,產(chǎn)生高水平靜電和快速瞬態(tài)浪涌。這些ESD事件可能會干擾設(shè)備,從故障到集成電路的破壞。

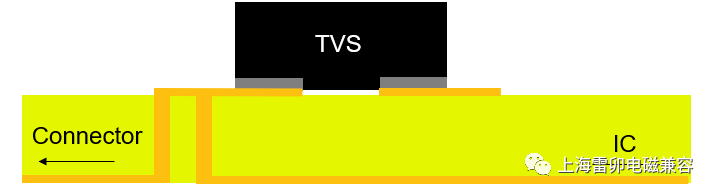

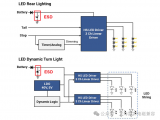

將這些問題最小化的最佳方法是從PCB入口放置瞬態(tài)電壓抑制器(TVS),放置在可能出現(xiàn)浪涌的地方;但在選擇這些組件PCB布局必須小心,以確保最好的保護。

電磁兼容可靠性要求

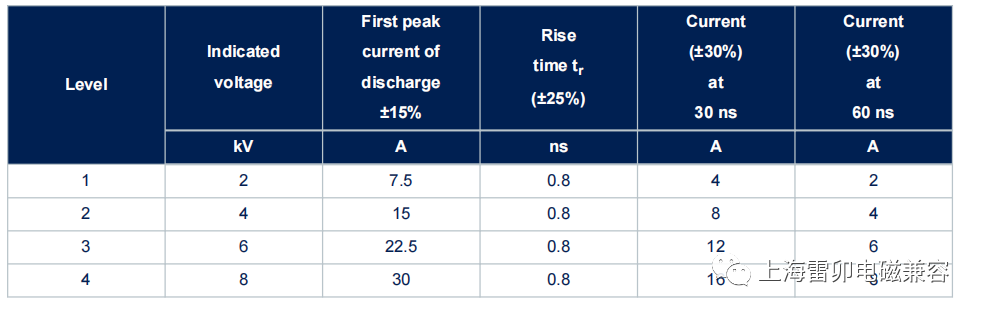

很明顯,敏感部件可能會出現(xiàn)靜電損壞風(fēng)險。國際電工委員會IEC委員會定義了標準,該標準定義了四種嚴重等級,對應(yīng)于四種電壓等級,有兩種放電、接觸和空氣類型。對接觸放電的類別與電壓水平和電流波形的定義顯示了對接觸放電的這些類別的定義以及與不同電壓水平的波形的定義。

下表是IEC61000-4-2規(guī)定最新定義的接觸靜電放電的波形4級測試要求,附帶測試標準波形的具體時間和電壓圖。

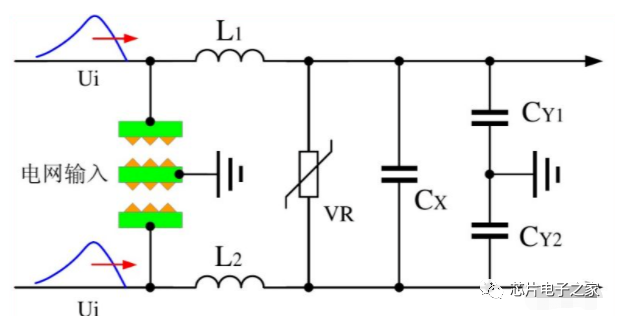

線路中TVS設(shè)置

大家都知道要在接口處設(shè)置TVS保護器件,但有時候達不到理想的測試效果,這里要分析一下原因:

1 TVS型號選型不當

2 PCB設(shè)計不合理,導(dǎo)致TVS保護效果不佳

這里主要討論在PCB上怎么合理設(shè)計讓TVS發(fā)揮最大的保護功效。

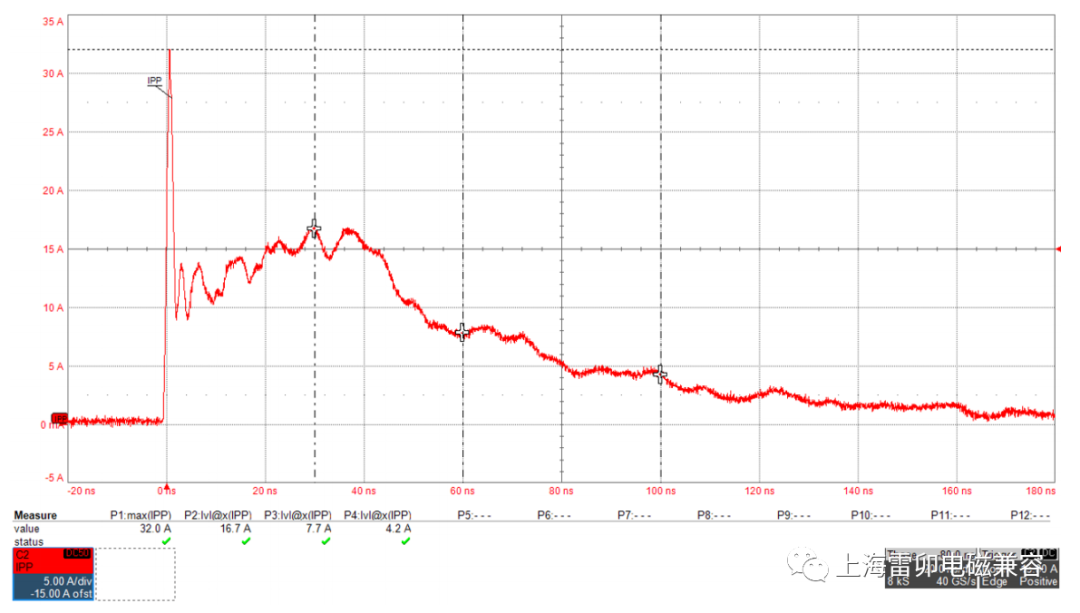

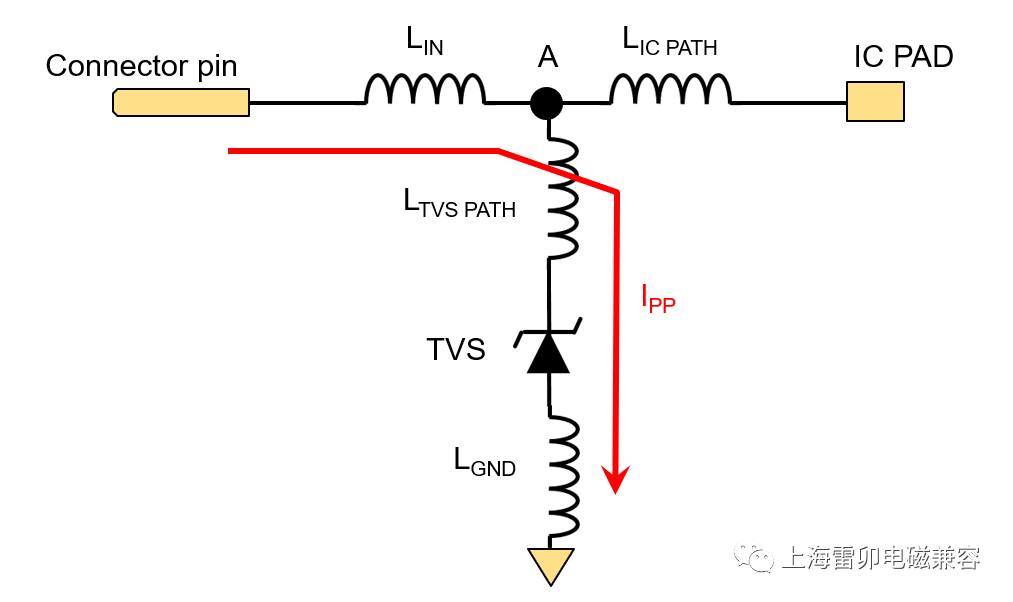

這里就要考慮線路上的各種寄生電感,包括TVS管腳自身的寄生感值。這會影響靜電或浪涌發(fā)生時后端IC處的箝位電壓Vc值。

TVS本身遵從以下公式

VCL = VBR + RD × IPP

R為TVS本身的寄生電容值,越小的產(chǎn)品他的箝位電壓會更好,更有效保護IC,IPP是測試瞬間通過TVS本身的電流值。

在測試圖中,A點的電壓并不是Vc值,Va電壓需要加上TVS 兩端的電壓。

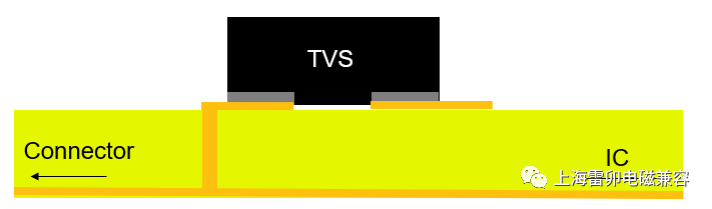

LIN和LIC由PATH通常由線路的控制阻抗(例如50Ω或100 Ω差分)驅(qū)動。為了迫使浪涌電流通過保護電路,我們必須確保LGND和LTVS路徑盡可能低。此外,為了減少PCB上的輻射,最好的方法是將保護電路盡可能靠近連接器針腳。

以下有三種TVS在板子上的接線方式,供大家選擇優(yōu)劣。

以上ABC的設(shè)置方式,大家可以評論哪種方式最好。答案是C

設(shè)計案例

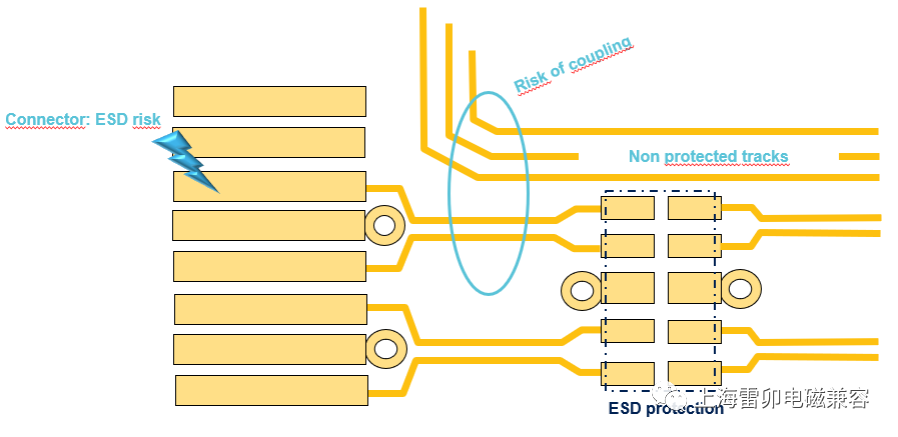

需要考慮未被保護的路徑遠離在保護路徑上,否則會有EMI干擾的風(fēng)險。

總結(jié)

以上我們看到,為了限制各種寄生電路的布局,必須注意產(chǎn)生的過電壓和電磁干擾。注意接地連接和將TVS放置在正確的方式上,保證一個成功的電路,以確保設(shè)備的高可靠性水平的關(guān)鍵。綜上所述,以下要點:確保保護裝置連接到地面盡可能短,盡量減少寄生電感路徑從靜電電源到保護組件,然后從保護組件到芯片保護(而不是從靜電電源到芯片保護,然后保護連接到該路徑)。這也是一種避免寄生電感,將保護組件盡可能接近ESD源:這將最小化PCB上的EMI,與其他路徑耦合化PCB上的EMI,與其他路徑耦合。

上海雷卯專注電子產(chǎn)品電磁兼容設(shè)計,電子產(chǎn)品的接口防護需用過壓保護器件,很多工程師意識到要用保護器件,但由于選型不當或沒按照ESD電路PCB設(shè)計原則,造成產(chǎn)品靜電測試或EMC測試不通過,產(chǎn)品多次驗證測試,浪費人力財力,造成產(chǎn)品延遲上市的事情總有發(fā)生,或過度設(shè)計,造成成本壓力。

雷卯電子專業(yè)為客戶提供電磁兼容EMC的設(shè)計服務(wù),提供實驗室做摸底免費測試,從客戶高效,控本方便完成設(shè)計,希望為更多的客戶能快速通過EMC的項目,提高產(chǎn)品可靠性盡力。

雷卯電子電磁兼容實驗室,提供免費測試,提供外圍靜電保護參考電路。

-

浪涌

+關(guān)注

關(guān)注

3文章

252瀏覽量

28499 -

防靜電

+關(guān)注

關(guān)注

3文章

149瀏覽量

12964

發(fā)布評論請先 登錄

相關(guān)推薦

防雷浪涌保護TVS管型號 選型輕松拿捏

汽車氛圍燈靜電浪涌保護設(shè)計方案

使用ST+W5500的電路,如何實現(xiàn)防靜電處理,是接TVS嗎?

3.7V鋰電池浪涌靜電保護用TVS/ESD二極管

TVS二極管如何選型?PROFIBUS總線端口靜電浪涌防護

我們常說的激光二極管的防靜電等級是什么?

帶著電池能防靜電?假的 那么冬天有靜電怎么消除?

TVS管應(yīng)用選型要點

防靜電離子風(fēng)扇的特點及應(yīng)用

防靜電電阻大好還是小好

使用絕緣表測量防靜電桌墊的電阻阻值

防靜電和浪涌TVS layout設(shè)計要點

防靜電和浪涌TVS layout設(shè)計要點

評論