本文要點(diǎn):

什么是垂直導(dǎo)電結(jié)構(gòu)(Vertical Conductive Structures,VeCS)及其工作原理。

利用 VeCS 進(jìn)行PCB設(shè)計(jì)的優(yōu)勢(shì)。

使用 VeCS 技術(shù)設(shè)計(jì)電路板的后續(xù)步驟。

長(zhǎng)久以來(lái),我們不斷努力改進(jìn)設(shè)計(jì)和構(gòu)建電路板的方式——已從通孔發(fā)展到表面貼裝元件,從雙層電路板發(fā)展到多層電路板,從普通導(dǎo)線走線發(fā)展到高密布線。似乎如今已沒(méi)有什么可以嘗試的新鮮技術(shù),然而這種想法是錯(cuò)誤的。

為了盡可能有效地利用可用的電路板空間,目前業(yè)內(nèi)正在引入一種新的走線布線方法。這種方法使用垂直導(dǎo)電結(jié)構(gòu) (Vertical Conductive Structures,VeCS),允許在板層堆疊中垂直布線,而不是使用傳統(tǒng)的過(guò)孔。顯然,這樣做可以節(jié)省不少空間,還額外帶來(lái)許多其他好處。下面我們來(lái)具體了解一下。

建議在 WIFI 環(huán)境下觀看,并注意調(diào)整音量

1

VeCS 及其工作原理

在擁有大量引腳、遍布細(xì)間距元件的高密電路板上進(jìn)行布線,挑戰(zhàn)之一是為所有的走線找到足夠的布線通道。即便使用微孔和 BGA 盤(pán)中孔 (via-in-pad) 技術(shù)進(jìn)行逃逸布線,用于布線的可用空間也會(huì)很快用完。另一個(gè)問(wèn)題是,為了在更多的層上打更深的孔,必須增加鉆孔直徑,這也占用了更多的空間。此時(shí),垂直導(dǎo)電結(jié)構(gòu) (VeCS) 就有了用武之地。

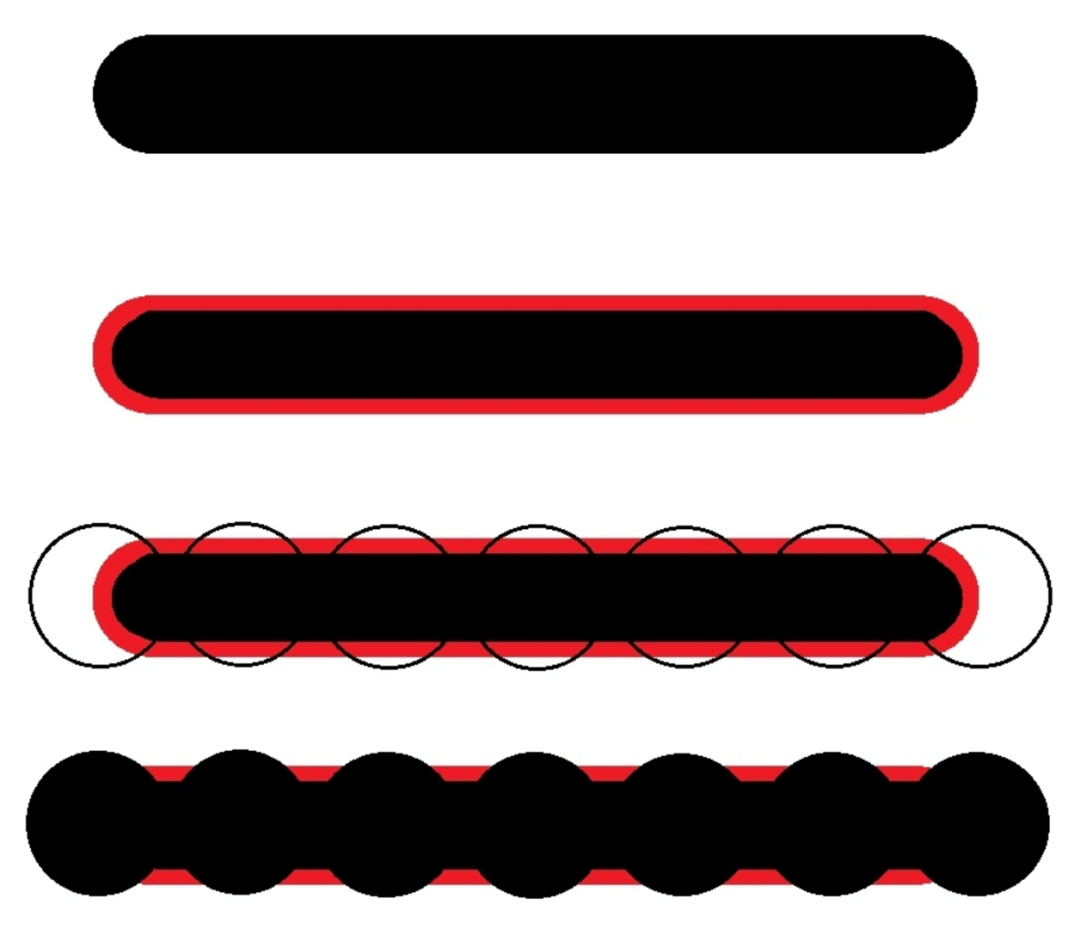

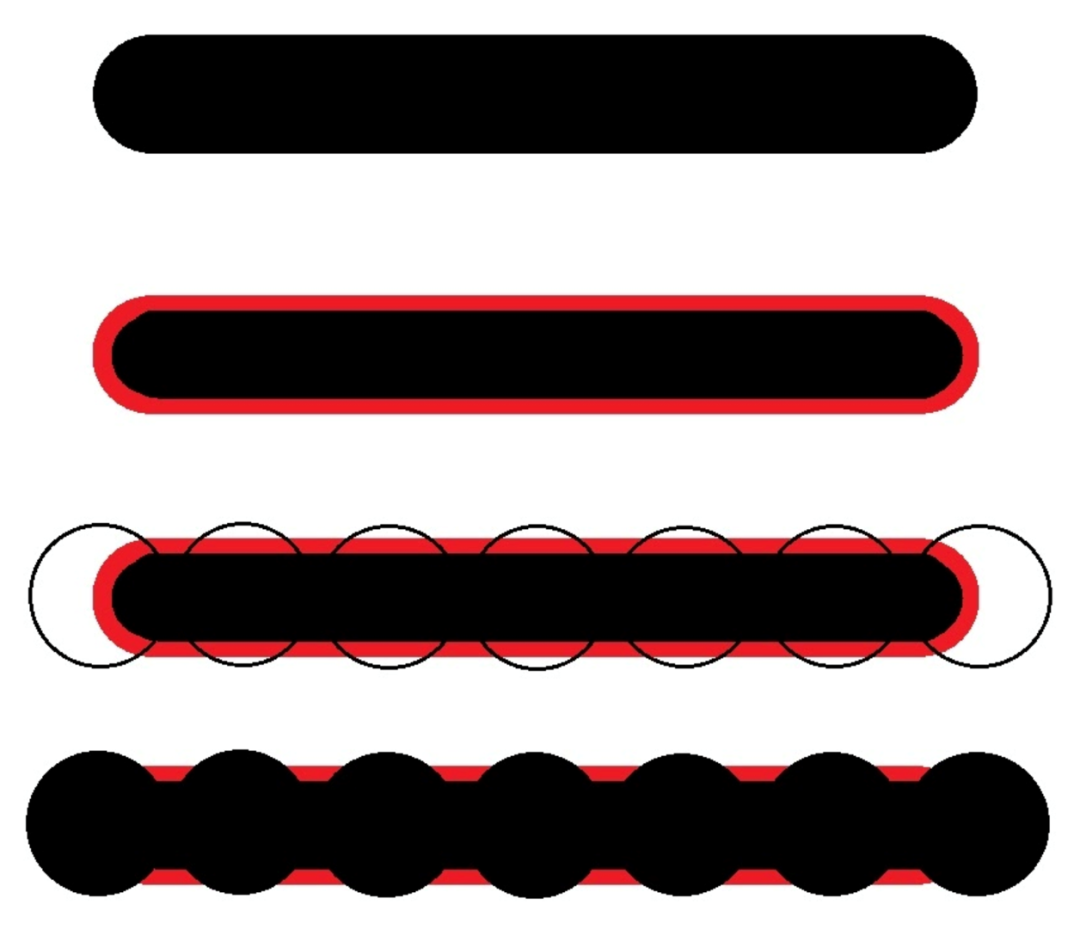

VeCS 技術(shù)允許走線垂直穿過(guò)電路板的堆疊,從而取代了鉆孔。除了傳統(tǒng)的制造通孔電路所需的設(shè)備外,該技術(shù)不需要使用任何專門(mén)的設(shè)備,但它會(huì)將 PCB 的布線密度提高到接近高密互連 (HDI) 的水平。以下是在電路板上制造 VeCS 的基本步驟,如下圖所示:

1

從頂部看,通過(guò)在電路板材料上鉆孔和/或布線來(lái)創(chuàng)建一個(gè)插槽。

2

根據(jù)標(biāo)準(zhǔn)的 PCB 制造技術(shù),對(duì)該插槽進(jìn)行金屬化和電鍍處理。

3

較大的鉆孔相鄰放置,以鉆出不需要的金屬。

4

較大的鉆孔相鄰放置,以鉆出不需要的金屬。

VeCS 的基本制造過(guò)程。

當(dāng)然,這只是一個(gè)非常基本的例子,實(shí)際制造過(guò)程取決于每個(gè)應(yīng)用的具體要求。如上圖底部所示,紅色的小區(qū)域是垂直穿過(guò)電路板的金屬。然后,這些垂直的導(dǎo)體可以觸及電路板內(nèi)層的普通水平走線。

可以在垂直導(dǎo)電結(jié)構(gòu)中使用兩種插槽技術(shù):VeCS-1 和 VeCS-2。第一種類型的插槽穿過(guò)整個(gè)電路板堆疊,而第二種類型則用于多級(jí)盲孔連接。由于 VeCS 是使用標(biāo)準(zhǔn)工藝制造的,它們也可以與通孔、盲孔和埋孔以及微孔技術(shù)結(jié)合使用。這提供了諸多優(yōu)勢(shì),詳見(jiàn)下文討論。

2

利用 VeCS 進(jìn)行 PCB 設(shè)計(jì)的優(yōu)勢(shì)

從上圖可以看到,垂直導(dǎo)體的橫截面更小,比鉆孔的橫截面更接近于標(biāo)準(zhǔn)走線。與通孔相比,這種導(dǎo)體輪廓最終導(dǎo)致網(wǎng)絡(luò)的電感量更小。同時(shí),更有利于垂直走線將信號(hào)傳遞到參考平面,所有這些都有助于改善電路板的整體信號(hào)完整性。

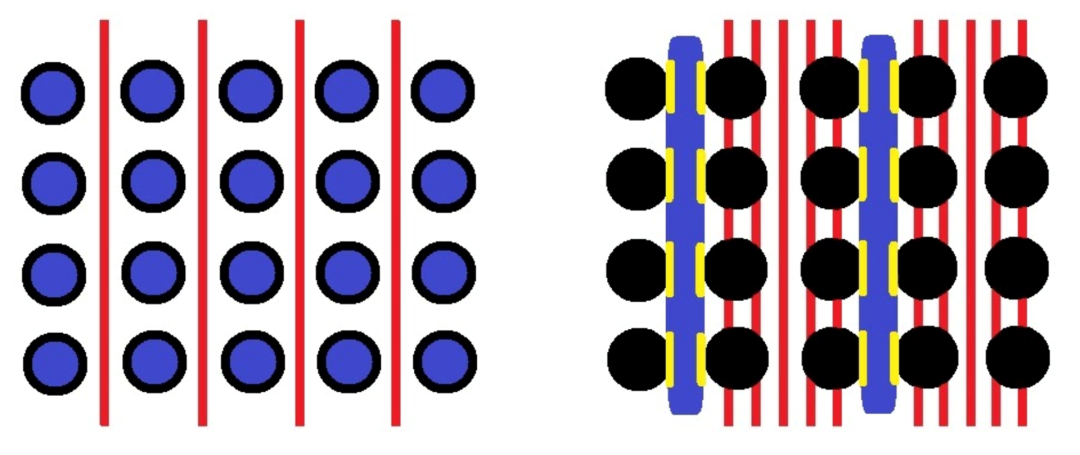

不過(guò),最主要的優(yōu)勢(shì)可能是 VeCS 為走線布線增加了布線通道。對(duì)于一個(gè)具有 0.5 毫米間距引腳的 BGA 元件,使用盤(pán)中孔進(jìn)行逃逸布線時(shí),在內(nèi)層布線通道上的孔之間的空間僅夠布設(shè)一條走線。然而,通過(guò)使用 VeCS,布線通道的數(shù)量增加到了五個(gè)。在下圖中,可以看到兩者之間的區(qū)別,左邊是標(biāo)準(zhǔn)的盤(pán)中孔逃逸布線模式,右邊是 VeCS。

藍(lán)色代表鉆孔或布線的區(qū)域,而紅色是可以通過(guò)內(nèi)層的通道進(jìn)行布線的走線。可以看到,黃色的垂直走線連接到黑色的 BGA 焊盤(pán),然后向下延伸通過(guò)電路板層堆疊。同樣,這只是一個(gè)基本的例子,但它可以讓我們了解 VeCS 所能提供的一些空間優(yōu)勢(shì)。

盤(pán)中孔和 VeCS 布線比較。

有了增加布線密度的能力,電路板的尺寸和/或?qū)訑?shù)就可以減少;這也會(huì)降低制造成本。那么下一個(gè)問(wèn)題是,如何才能在 PCB 上設(shè)計(jì) VeCS?

3

使用 VeCS 技術(shù)設(shè)計(jì)電路板的步驟

制造和設(shè)計(jì)垂直導(dǎo)電結(jié)構(gòu) (VeCS) 的技術(shù)早已問(wèn)世。PCB 設(shè)計(jì) CAD 工具經(jīng)過(guò)恰當(dāng)設(shè)置后可以與這種技術(shù)配合使用;此外,一些先進(jìn)的設(shè)計(jì)系統(tǒng),如 Cadence Allegro PCB Designer,無(wú)需額外配置即可設(shè)計(jì) VeCS。同時(shí),也要確保合作的 PCB 制造廠經(jīng)過(guò)許可,能夠生產(chǎn)這種技術(shù)。一旦確認(rèn)了這一點(diǎn),就可以開(kāi)始探索這項(xiàng)新技術(shù)了。

在我們的行業(yè)中,還會(huì)出現(xiàn)更多新的電路板設(shè)計(jì)和制造技術(shù),為了保持領(lǐng)先,我們應(yīng)該做好準(zhǔn)備,在這些新的技術(shù)出現(xiàn)時(shí)進(jìn)行大膽探索。要實(shí)現(xiàn)這一點(diǎn),需要擁有一個(gè)能夠支持這些新技術(shù)的 PCB 設(shè)計(jì)系統(tǒng)作為設(shè)計(jì)過(guò)程的基礎(chǔ)。事實(shí)證明,Allegro PCB Designer 經(jīng)過(guò)妥當(dāng)設(shè)置,可以很好地支持 VeCS 和許多其他新興技術(shù)。

-

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396294 -

布線

+關(guān)注

關(guān)注

9文章

766瀏覽量

84294

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

技術(shù)資訊 I 如何使用 Allegro X PCB Editor 優(yōu)化RF布線和阻抗

蛇形走線設(shè)計(jì)在電路板布線中的秘密

探索電路板pcb螺旋走線的特點(diǎn)

Xilinx 7系列FPGA PCB設(shè)計(jì)指導(dǎo)

pcb螺旋走線的優(yōu)劣勢(shì)對(duì)比

pcb走線厚度:打造更穩(wěn)定、精準(zhǔn)的PCB設(shè)計(jì)

PCB走線寬度定義與計(jì)算方法詳解

高速PCB信號(hào)走線的九大規(guī)則

技術(shù)資訊 I 詳解高密 PCB走線布線的垂直導(dǎo)電結(jié)構(gòu) (VeCS)

技術(shù)資訊 I 詳解高密 PCB走線布線的垂直導(dǎo)電結(jié)構(gòu) (VeCS)

評(píng)論