PCB工程師layout一款產(chǎn)品,不僅僅是布局布線,內(nèi)層的電源平面、地平面的設(shè)計也非常重要。處理內(nèi)層不僅要考慮電源完整性、信號完整性、電磁兼容性,還需要考慮DFM可制造性。

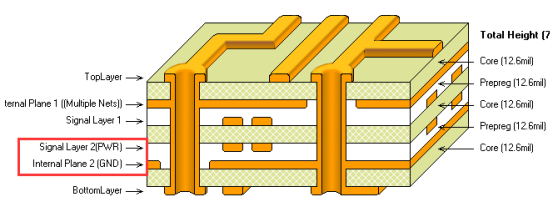

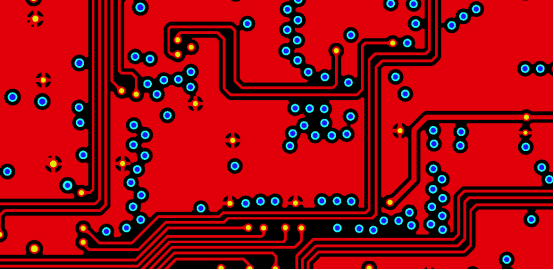

PCB表層是用來走線焊接元器件的,內(nèi)層則是規(guī)劃電源/接地層,該層僅用于多層板,主要用于布置電源線和接地線。我們稱之為雙層板、四層板和六層板,通常指信號層和內(nèi)部電源/接地層的數(shù)量。

4個重要的內(nèi)層設(shè)計問題

在高速信號,時鐘信號,高頻信號等關(guān)鍵信號的下面設(shè)計地線層,這樣信號環(huán)路的路徑最短,輻射最小。

高速電路設(shè)計過程中,必須考慮如何處理電源的輻射和對整個系統(tǒng)的干擾問題,一般情況電源層平面的面積小于地平面的面積,縮進(jìn)2倍的介質(zhì)厚度為最佳,可以對電源起屏蔽作用。

層疊規(guī)劃

電源層平面與相應(yīng)的地平面相鄰,目的是形成耦合電容,并與PCB板上的去耦電容共同作用,降低電源平面阻抗,同時獲得較寬的濾波效果。

選擇參考平面

參考層的選擇非常重要,理論上電源層和地平面層都能作為參考層,但是地平面層一般可以接地,屏蔽效果要比電源層好很多,所以一般優(yōu)先選擇地平面作為參考平面。

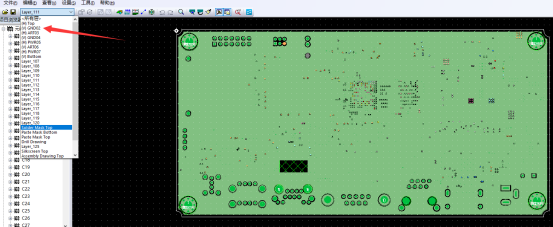

信號線不能跨區(qū)域走線

相鄰兩層的關(guān)鍵信號不能跨分割區(qū),否則會形成較大的信號環(huán)路,產(chǎn)生較強的輻射和耦合。

電源、地走線規(guī)劃

要保持地平面的完整性,不能在地平面走線,如果信號線密度太大,可以考慮在電源層的邊緣走線。

影響內(nèi)層制造的多種情況

由于PCB制造復(fù)雜的工藝流程,內(nèi)層制造的工藝只是其中一部分,在生產(chǎn)內(nèi)層板時還需考慮其他工序的工藝影響內(nèi)層的制造能力,比如壓合公差、鉆孔公差都會影響內(nèi)層的品質(zhì)良率。

PCB的層數(shù)可分為單面板、雙面板、多層板,這三種板子工藝流程也大不相同,尤其是多層板,生產(chǎn)工藝比單雙面板復(fù)雜許多,因此在設(shè)計多層板時,需考慮多層板復(fù)雜的工藝流程及DFM可制造性設(shè)計。

刪除獨立焊盤

獨立焊盤就是非功能性的PAD,在內(nèi)層不與任何網(wǎng)絡(luò)相連,在PCB制造過程中會取消獨立焊盤,因為此獨立焊盤取消對產(chǎn)品的設(shè)計功能無影響,反而在制造時會影響品質(zhì)及生產(chǎn)效率。

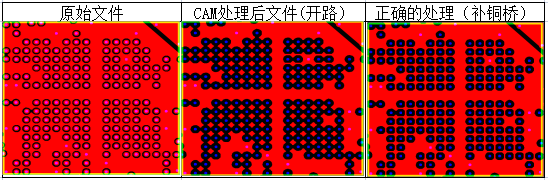

內(nèi)層BGA區(qū)域

BGA器件比較小,引腳非常多,因此設(shè)計出的過孔非常密集,在制造過程中鉆孔到走線、銅皮需要保留一定的間距,否則在壓合及鉆孔工序可能會短路,在保證鉆孔距銅皮、走線留一定的距離時,孔與孔中間的銅無法保留,會導(dǎo)致網(wǎng)絡(luò)開路,因此在CAM工程師處理BGA區(qū)域時需注意孔與孔中間的銅開路了需補銅橋,保證生產(chǎn)后網(wǎng)絡(luò)連接不斷開。

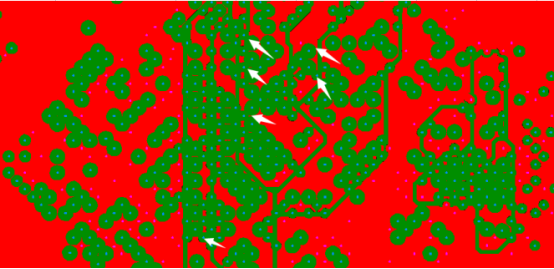

內(nèi)層設(shè)計異常

內(nèi)層負(fù)片的孔全部有孔環(huán),轉(zhuǎn)成正片圖形就是所有孔與銅皮不相連完全隔離,完全隔離就等于內(nèi)層沒有任何作用,不做內(nèi)層都可以,生產(chǎn)制造遇到此問題會跟設(shè)計工程師確認(rèn),是否設(shè)計異常,內(nèi)層銅皮沒有添加網(wǎng)絡(luò)導(dǎo)致完全隔離。

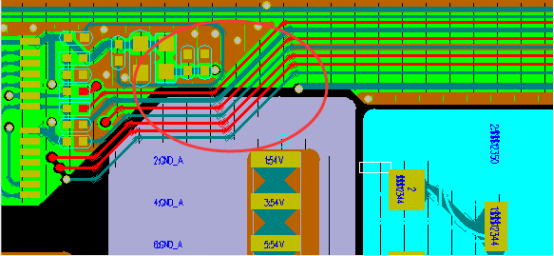

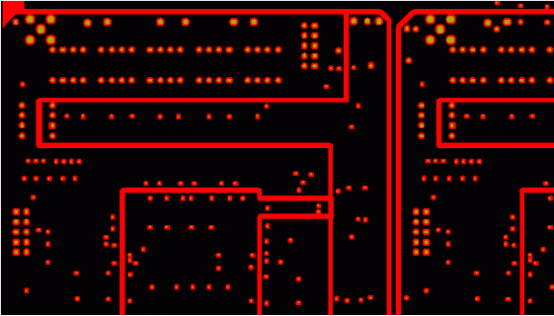

內(nèi)層負(fù)片瓶頸

在內(nèi)層設(shè)計電源層、地層分割時,由于過孔密集會出現(xiàn)網(wǎng)絡(luò)導(dǎo)通的瓶頸,電源網(wǎng)絡(luò)導(dǎo)通的銅橋?qū)挾炔粔颍瑫?dǎo)致過不了相匹配的電流,從而導(dǎo)致燒板,甚至有些瓶頸位置直接開路,導(dǎo)致產(chǎn)品設(shè)計失敗。

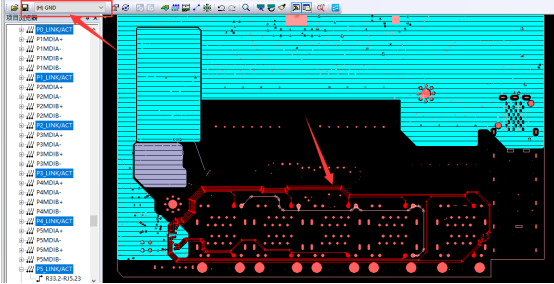

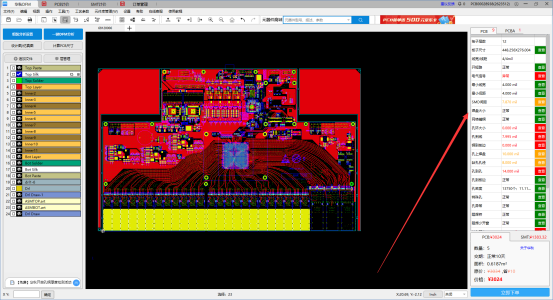

一鍵DFM檢測內(nèi)層設(shè)計

內(nèi)層設(shè)計隱患繁多,很難提前規(guī)避所有風(fēng)險,這里推薦一款華秋DFM可制造性分析軟件,對于上文提到的可制造性問題都能夠檢測出來,并提示存在的制造風(fēng)險,讓設(shè)計工程師在制造前發(fā)現(xiàn)設(shè)計存在的缺陷,并修改檢測的問題點,避免設(shè)計的產(chǎn)品在制造過程中出現(xiàn)問題,從而提升產(chǎn)品的成功率,減少多次試樣的成本。

華秋DFM軟件是國內(nèi)首款免費PCB可制造性和裝配分析軟件,擁有300萬+元件庫,可輕松高效完成裝配分析。其PCB裸板的分析功能,開發(fā)了19大項,52細(xì)項檢查規(guī)則,PCBA組裝的分析功能,開發(fā)了10大項,234細(xì)項檢查規(guī)則。

基本可涵蓋所有可能發(fā)生的制造性問題,能幫助設(shè)計工程師在生產(chǎn)前檢查出可制造性問題,且能夠滿足工程師需要的多種場景,將產(chǎn)品研制的迭代次數(shù)降到最低,減少成本。

軟件下載地址(復(fù)制到瀏覽器下載) ↓

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqsc.zip

關(guān)注我,獲取更多電子干貨!

關(guān)注我,獲取更多電子干貨!

-

pcb

+關(guān)注

關(guān)注

4317文章

23013瀏覽量

396376 -

制造

+關(guān)注

關(guān)注

2文章

503瀏覽量

23970

發(fā)布評論請先 登錄

相關(guān)推薦

PCB可制造性設(shè)計:開啟高效生產(chǎn)的鑰匙

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區(qū)別?

原來手機(jī)SIM卡的PCB設(shè)計是這樣的!

嵌入式軟件工程師和硬件工程師的區(qū)別?

學(xué)起來!做PCB設(shè)計師中最靚的崽

CPCI設(shè)計與制造:提高可制造性的關(guān)鍵要素

構(gòu)建系統(tǒng)思維:信號完整性,看這一篇就夠了!

PCB內(nèi)層的可制造性設(shè)計

【工程師進(jìn)階】搞懂PCB內(nèi)層的可制造性設(shè)計是關(guān)鍵

【工程師進(jìn)階】搞懂PCB內(nèi)層的可制造性設(shè)計是關(guān)鍵

評論