SPI接口概述

AT32的SPI接口提供軟件編程配置選項,根據軟件編程配置方式不同,可以分別作為SPI和I2S使用。本文將分SPI和I2S分別介紹SPI接口作SPI或I2S的功能特性以及配置流程。AT32 SPI特點:

可編程配置的全雙工或半雙工通信

--全雙工同步通信--半雙工同步通信(可以根據軟件編程配置選擇傳輸方向:發送或接收)

可編程配置主/從模式

可編程配置的CS模式:硬件/軟件CS模式

可編程配置的時鐘極性和相位

可編程配置的數據傳輸順序(MSB/LSB)

可編程配置的錯誤中斷標志(CS脈沖異常,接收溢出錯誤,主模式錯誤,CRC校驗錯誤)

數據接收/發送均支持DMA

兼容TI的SSP協議(即TI模式)

AT32 I2S特點:

可編程配置的操作模式

--從設備發送--從設備接收--主設備發送--主設備接收

可編程配置的時鐘極性

可編程配置的時鐘頻率(8KHz到192KHz)

可編程配置的數據位數(16位,24位,32位)

可編程配置的聲道位數(16位,32位)

可編程配置的音頻協議

--I2S飛利浦標準--高字節對齊標準(左對齊)--低字節對齊標準(右對齊)--PCM標準(長幀/短幀)

支持I2S全雙工

支持DMA傳輸

在通訊期間可提供頻率固定為256倍Fs(音頻采樣頻率)的外設主時鐘

SPI功能介紹

本章主要介紹SPI基本功能,以及AT32 SPI的各種附加可配置選項。

SPI硬件接口

SPI接口定義如下:

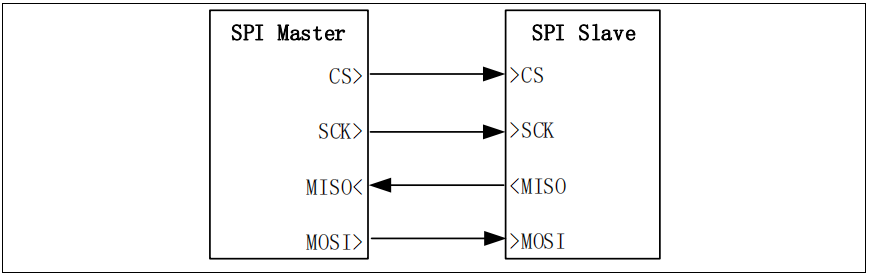

CS:片選引腳(可選)。通常由主機輸出,從機輸入。后續CS管理章節作詳細介紹。

SCK:時鐘引腳。由主機輸出,從機輸入。

MISO:主收從發引腳。主機則作為接收數據引腳,從機則做為發送數據引腳。

MOSI:主發從收引腳。主機則作為發送數據引腳,從機則作為接收數據引腳。

以下介紹幾種常見的SPI通信接線方式。1)如下圖1,是單主單從、全雙工、CS硬件模式的應用接線示意圖。圖1 SPI單主單從、全雙工、硬件CS管理接線示意 2)如下圖2,是單主單從、全雙工、CS軟件模式的應用接線示意圖。在CS軟件管理模式下,無需使用CS引腳,主/從機的CS引腳都可以釋放給其他應用使用。此時,從機對SWCSIL位清0或置1等效于“硬件CS模式”下的CS引腳輸入低電平和高電平。主機則必須將SWCSIL位置1,以保證正確的處于主機模式。圖2 SPI單主單從、全雙工、軟件CS管理接線示意

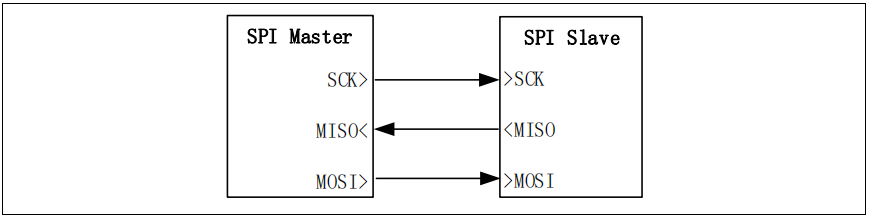

2)如下圖2,是單主單從、全雙工、CS軟件模式的應用接線示意圖。在CS軟件管理模式下,無需使用CS引腳,主/從機的CS引腳都可以釋放給其他應用使用。此時,從機對SWCSIL位清0或置1等效于“硬件CS模式”下的CS引腳輸入低電平和高電平。主機則必須將SWCSIL位置1,以保證正確的處于主機模式。圖2 SPI單主單從、全雙工、軟件CS管理接線示意

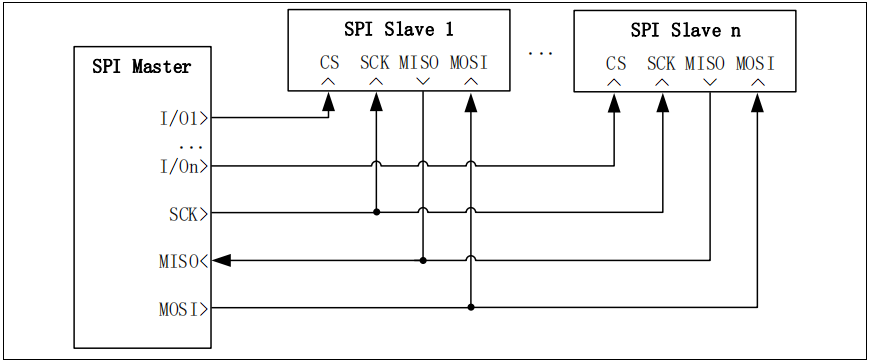

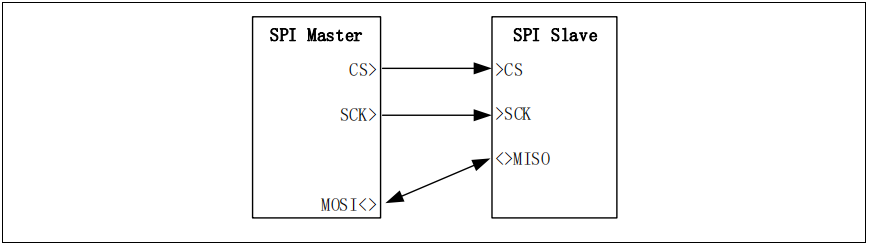

3)如下圖3,是單主多從全雙工接線示意。主機使用普通I/O口1~n輸出以驅動從機1~n的片選CS,主機的SCK,MISO,MOSI和從機的SCK,MISO,MOSI引腳一對多連接。此時SPI主機可以通過I/O1~n的選擇與多個從機進行分時通信。此時從機必須使用硬件CS模式。主機可以使用軟件CS模式,主機CS對應的引腳可以釋放給其他應用使用。圖3 SPI單主多從、全雙工接線示意 4)如下圖4,AT32的SPI增加了SPI半雙工模式,此模式下只需要使用3線即可通信。主機使用MOSI進行數據收/發。當主機配置為半雙工發送模式(SLBEN=1,SLBTD=1)時,主機MOSI為輸出引腳,用于發送數據;當主機配置為半雙工接收模式(SLBEN=1,SLBTD=0)時,主機MOSI為輸入引腳,用于接收數據。從機使用MISO進行數據收/發。當從機配置為半雙工發送模式(SLBEN=1,SLBTD=1)時,從機MISO為輸出引腳,用于發送數據;當從機配置為半雙工接收模式(SLBEN=1,SLBTD=0)時,從機MISO為輸入引腳,用于接收數據。圖4 SPI單主單從、半雙工接線示意

4)如下圖4,AT32的SPI增加了SPI半雙工模式,此模式下只需要使用3線即可通信。主機使用MOSI進行數據收/發。當主機配置為半雙工發送模式(SLBEN=1,SLBTD=1)時,主機MOSI為輸出引腳,用于發送數據;當主機配置為半雙工接收模式(SLBEN=1,SLBTD=0)時,主機MOSI為輸入引腳,用于接收數據。從機使用MISO進行數據收/發。當從機配置為半雙工發送模式(SLBEN=1,SLBTD=1)時,從機MISO為輸出引腳,用于發送數據;當從機配置為半雙工接收模式(SLBEN=1,SLBTD=0)時,從機MISO為輸入引腳,用于接收數據。圖4 SPI單主單從、半雙工接線示意

SPI數據接收和發送

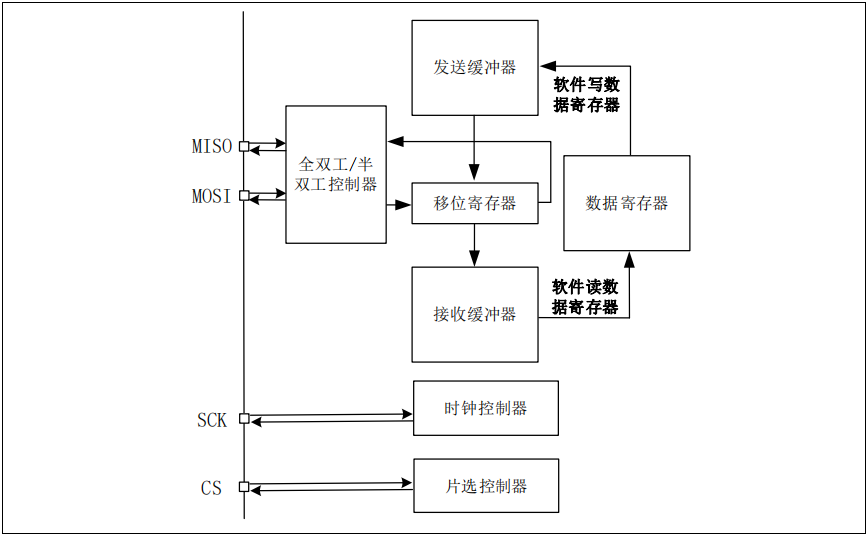

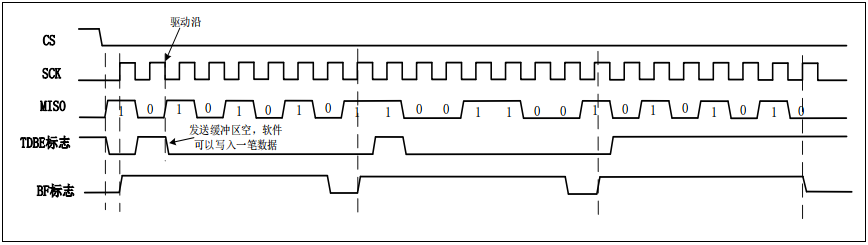

如下圖5,用戶軟件程序可以讀和寫數據寄存器,其他部分全由硬件自動完成。以全雙工,硬件CS管理,8bit數據格式為例。收發一筆數據的流程如下:作為SPI主機時:軟件使能SPI(SPIEN=1)后,硬件控制CS引腳輸出低電平,以片選從機。之后軟件往數據寄存器寫入數據,如下圖5的“軟件寫數據寄存器”處,相當于往發送緩沖器寫入待發送數據,之后硬件會自動將發送緩沖器的待發送數據搬運到移位寄存器。同時將發送緩沖器空標志置1(TDBE=1),以提醒軟件又可以往數據寄存器寫入下一筆待發送的數據。之后硬件立即開始在SCK引腳上輸出時鐘信號,并在MOSI引腳上發出待發送數據的第一bit數據。之后硬件從MISO引腳上讀取待接收數據的第一bit數據并放入移位寄存器中(移位寄存器由于之前發送了1bit數據,此時正好有一bit位置可以存放收到的數據)。之后硬件會通過移位寄存器自動發送和接收剩下的7bit數據。之后硬件會將移位寄存器中接收到的8bit數據搬運到接收緩沖器中,并將接收緩沖器滿標志置1(RDBF=1),以提醒軟件可以通過讀取數據寄存器來讀取剛剛接收到的這筆數據。作為SPI從機時:軟件使能SPI(SPIEN=1)后,軟件往數據寄存器寫入數據,相當于往發送緩沖器寫入待發送數據,然后硬件會將發送緩沖器空標志清0(TDBE=0),以提醒軟件此時發送緩沖器已有待發送數據了。之后硬件檢測CS引腳和SCK引腳,等待來自主機的片選和時鐘信號。檢測到片選和時鐘信號之后,硬件自動將發送緩沖器的待發送數據搬運到移位寄存器并在MISO引腳上發出待發送數據的第一bit。同時將發送緩沖器空標志置1(TDBE=1),以提醒軟件又可以往數據寄存器寫入下一筆待發送的數據。之后硬件從MOSI引腳上讀取待接收數據的第一bit數據并放入移位寄存器中(移位寄存器由于之前發送了1bit數據,此時正好有一bit位置可以存放收到的數據)。之后硬件根據在SCK上的時鐘信號,會在MISO和MOSI引腳上發送和接收剩下的7bit數據。之后硬件會將移位寄存器中接收到的8bit數據搬運到接收緩沖器中,并將接收緩沖器滿標志置1(RDBF=1),以提醒軟件可以通過讀取數據寄存器來讀取剛剛接收到的這筆數據。也可以參考下一小節“SPI時序”來理解SPI收發邏輯。

圖5 SPI數據接收/發送框圖

SPI時序

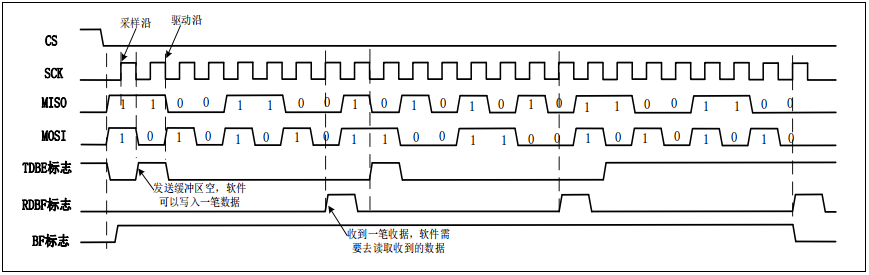

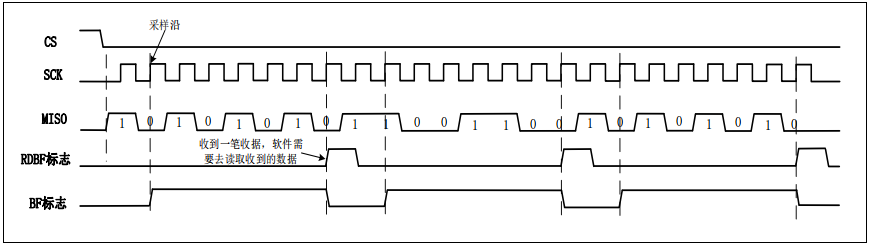

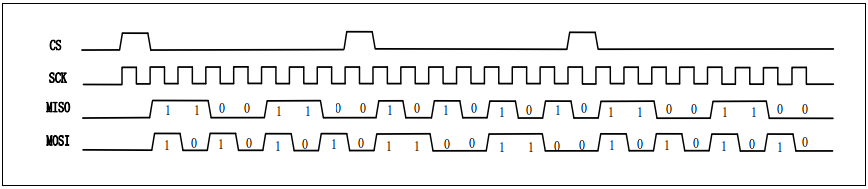

本節介紹SPI通信時序。包括全雙工和半雙工的主/從通信時序。1、SPI全雙工時序以全雙工、硬件CS管理、單主單從通信為例。其中主機端相關配置如下:MSTEN=1:設備為主機;SLBEN=0:全雙工模式;CLKPOL=0:SCK空閑輸出低電平;CLKPHA=0:SCK第一個邊沿開始進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0,HWCSOE=1:使用硬件CS管理;主機發送數據(MOSI):0xAA,0xCC,0xAA;從機發送數據(MISO):0xCC,0xAA,0xCC。

主機端時序見下圖6:圖6 硬件CS管理-全雙工-主機通信時序

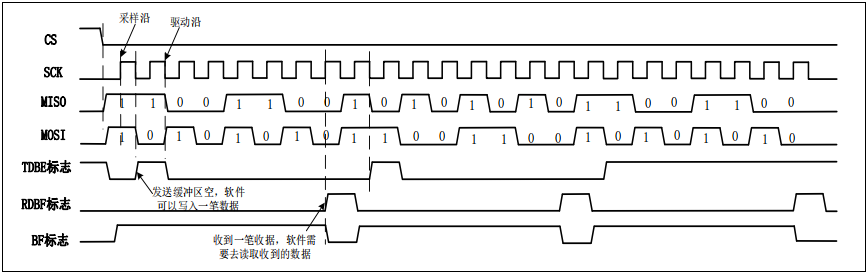

其中從機端相關配置如下:MSTEN=0:設備為從機SLBEN=0:全雙工模式;CLKPOL=0:SCK空閑低電平CLKPHA=0:SCK第一個邊沿進行數據捕獲FBN=0:幀位個數為8bitSWCSEN=0:使用硬件CS管理主機發送數據(MOSI):0xAA,0xCC,0xAA從機發送數據(MISO):0xCC,0xAA,0xCC從機端時序見下圖7:圖7 硬件CS管理-半雙工-從機通信時序

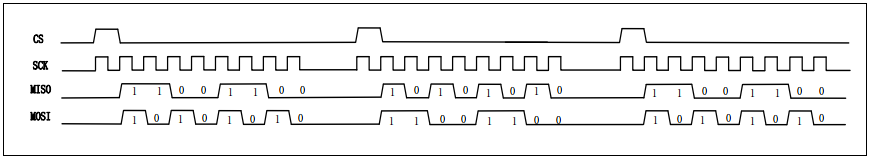

2、SPI半雙工時序半雙工時序下,有主機發送、從機接收、主機接收、從機發送4種模式。1)以半雙工、硬件CS管理、主機發送-從機接收通信為例。其中主機端相關配置如下:MSTEN=1:設備為主機;SLBEN=1:使能單線雙向半雙工模式;SLBTD=1:發送模式;CLKPOL=0:SCK空閑輸出低電平;CLKPHA=0:SCK第一個邊沿開始進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0,HWCSOE=1:使用硬件CS管理;主機發送數據:0xAA,0xCC,0xAA;

主機端時序見下圖8:圖8 硬件CS管理-半雙工-主發時序

其中從機端相關配置如下:MSTEN=0:設備為從機;SLBEN=1:使能單線雙向半雙工模式;SLBTD=0:接收模式;CLKPOL=0:SCK空閑低電平;CLKPHA=0:SCK第一個邊沿進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0:使用硬件CS管理;從機接收數據:0xAA,0xCC,0xAA;從機端時序見下圖9:圖9 硬件CS管理-半雙工-從收時序

其中從機端相關配置如下:MSTEN=0:設備為從機;SLBEN=1:使能單線雙向半雙工模式;SLBTD=0:接收模式;CLKPOL=0:SCK空閑低電平;CLKPHA=0:SCK第一個邊沿進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0:使用硬件CS管理;從機接收數據:0xAA,0xCC,0xAA;從機端時序見下圖9:圖9 硬件CS管理-半雙工-從收時序

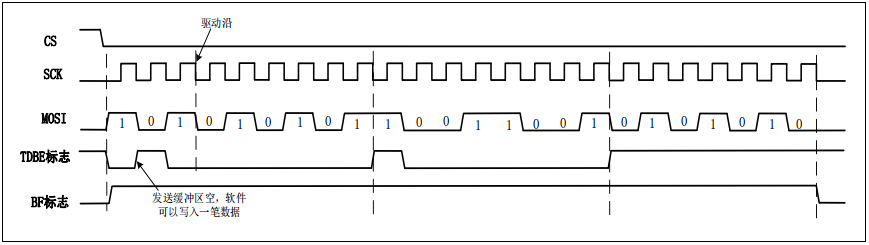

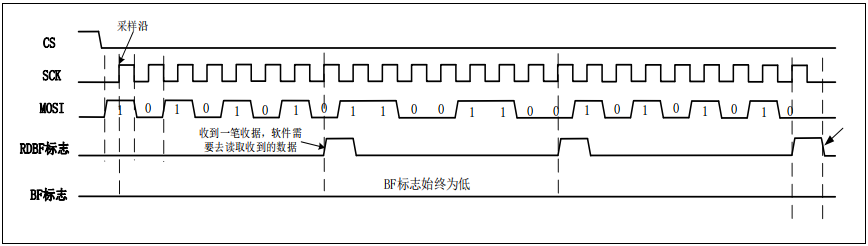

2)以半雙工、硬件CS管理、主機接收-從機發送通信為例。其中主機端相關配置如下:MSTEN=1:設備為主機;SLBEN=1:使能單線雙向半雙工模式;SLBTD=0:接收模式;CLKPOL=0:SCK空閑輸出低電平;CLKPHA=0:SCK第一個邊沿開始進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0,HWCSOE=1:使用硬件CS管理;主機接收數據:0xAA,0xCC,0xAA;主機端時序見下圖10:此模式下,較為特別的是,SPI主機一旦使能(SPIEN=1),就會連續不斷的輸出時鐘。因此,主機在接收完需要接收的數據后,需要關閉SPI。在本例中,接收完連續的3筆數據后,也就是下圖10的箭頭處,需要關閉SPI,輸出多余的時鐘。另外,如下圖10,此模式下,BF標志始終為低。圖10 硬件CS管理-半雙工-主收時序 其中從機端相關配置如下:MSTEN=0:設備為從機;SLBEN=1:使能單線雙向半雙工模式;SLBTD=1:發送模式;CLKPOL=0:SCK空閑低電平;CLKPHA=0:SCK第一個邊沿進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0:使用硬件CS管理;從機發送數據:0xAA,0xCC,0xAA;從機端時序見下圖11:圖11 硬件CS管理-半雙工-從發時序

其中從機端相關配置如下:MSTEN=0:設備為從機;SLBEN=1:使能單線雙向半雙工模式;SLBTD=1:發送模式;CLKPOL=0:SCK空閑低電平;CLKPHA=0:SCK第一個邊沿進行數據捕獲;FBN=0:幀位個數為8bit;SWCSEN=0:使用硬件CS管理;從機發送數據:0xAA,0xCC,0xAA;從機端時序見下圖11:圖11 硬件CS管理-半雙工-從發時序

SPI數據收發方式

SPI的接收和發送如前文所述,是通過操作數據寄存器來完成的。而根據操作數據寄存器的方法,SPI有以下3種數據接收發送方式。輪詢方式輪詢方式不需要使能SPI中斷和DMA。只需要在main函數中不斷讀取STS寄存器,并判斷TDBE和RDBF標志是否置起,以確定何時向數據寄存器寫入待發送數據,何時從數據寄存器讀取接收到的數據。比較耗費CPU資源,不建議使用此方式。具體請參考“案例1--SPI全雙工輪詢方式通信”一節。中斷方式中斷方式需要開啟“發送數據緩沖器空中斷使能”和“接收數據緩沖器滿中斷使能”,即設置TDBEIE=1,RDBFIE=1。并配置和使能SPI中斷。之后在SPI中斷里進行數據的發送和接收,避免了輪詢方式的等待耗時,占用CPU資源相對較少。具體請參考“案例4--SPI半雙工中斷方式通信”或“案例5--SPI半雙工中斷方式通信--加收發切換”一節。DMA方式DMA方式需要開啟SPI的DMA接收/發送功能(DMAREN=1,DMATEN=1)。并配置DMA通道映射到SPI和使能DMA。之后的接收和發送均由DMA完成,收/發過程不再需要軟件參與,不占用CPU資源。具體請參考“案例2--SPI全雙工DMA方式通信”一節。

時鐘控制器

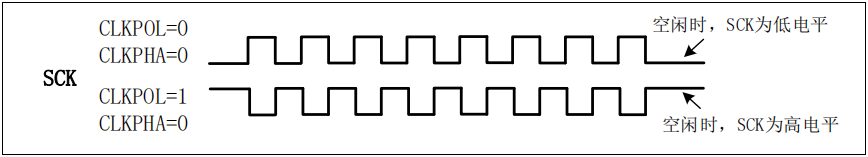

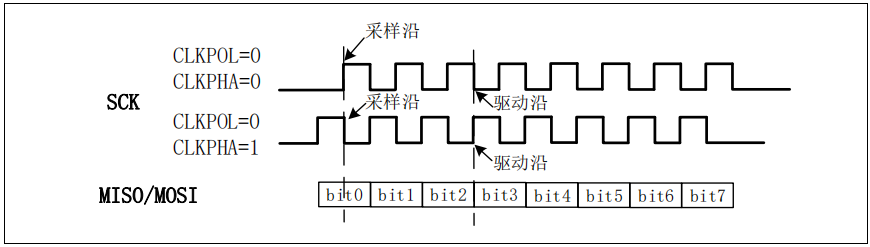

SPI協議采用同步傳輸。作主機時,需要時鐘控制器產生通信時鐘用于SPI接口的數據收發,并且需要將該通信時鐘通過SCK引腳輸出給從機,用于從機的數據收發;作從機時,需要外部提供通信時鐘,從SCK引腳輸入到SPI接口內部作為通信時鐘使用。對用戶而言,可軟件配置的主要有極性、相位、分頻系數三個參數。極性SPI時鐘極性,即空閑時SCK引腳輸出的電平。通過配置CLKPOL位來選擇SPI時鐘極性。如下圖12:CLKPOL=0時,SCK空閑為低電平;CLKPOL=1時,SCK空閑為高電平。圖12 時鐘極性對比 相位SPI時鐘相位,即SPI數據捕獲邊緣。通過配置CLKPHA位來選擇SPI時鐘極性。如下圖13:CLKPHA=0時,第一個邊沿為捕獲采樣邊沿。在本例中(CLKPOL=0),也就是上升沿為采樣沿;相對的,本例中下降沿為驅動沿。CLKPHA=1時,第二個邊沿為捕獲采樣邊沿。在本例中(CLKPOL=0),也就是下降沿為采樣沿;相對的,本例中上升沿為驅動沿。圖13 時鐘相位對比

相位SPI時鐘相位,即SPI數據捕獲邊緣。通過配置CLKPHA位來選擇SPI時鐘極性。如下圖13:CLKPHA=0時,第一個邊沿為捕獲采樣邊沿。在本例中(CLKPOL=0),也就是上升沿為采樣沿;相對的,本例中下降沿為驅動沿。CLKPHA=1時,第二個邊沿為捕獲采樣邊沿。在本例中(CLKPOL=0),也就是下降沿為采樣沿;相對的,本例中上升沿為驅動沿。圖13 時鐘相位對比

分頻系數SPI時鐘是從APB時鐘分頻得到的,通過配置MDIV[3:0]和MDIV3EN來選擇需要的分頻系數,以確定SPI時鐘。分頻系數僅主機配置有效。從機需要外部提供時鐘,因此此項配置無效。

CS管理

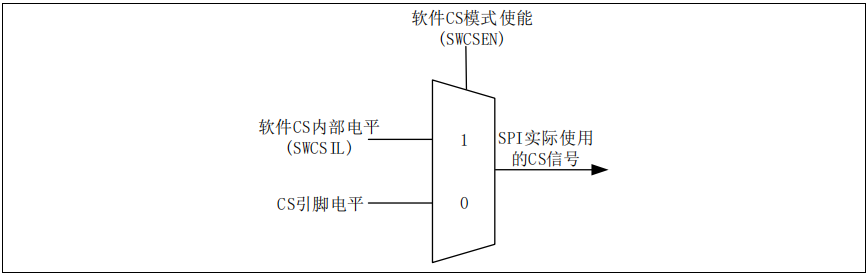

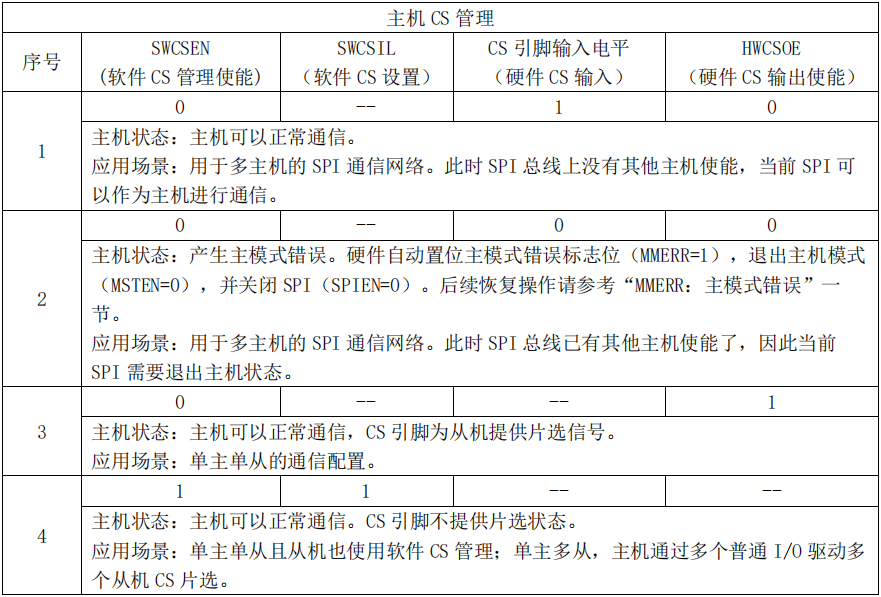

SPI CS包含硬件和軟件管理兩種模式,又根據主機/從機的不同,有不同的配置和應用場景。在CS為輸入模式時(HWCSOE=0),如下圖14,主機和從機均通過SWCSEN位來選擇SPI實際使用的CS信號來自軟件設置(SWCSIL)還是外部CS引腳電平。在CS為輸出模式時(HWCSOE=1),軟件CS模式相關配置無效。圖14 SPI數據接收/發送框圖 以下分別列出了主機和從機在不同的CS管理模式下的狀態和應用場景。主機CS管理:下表1列出了幾種主機CS管理的配置及應用場景。表1 SPI主機CS管理配置

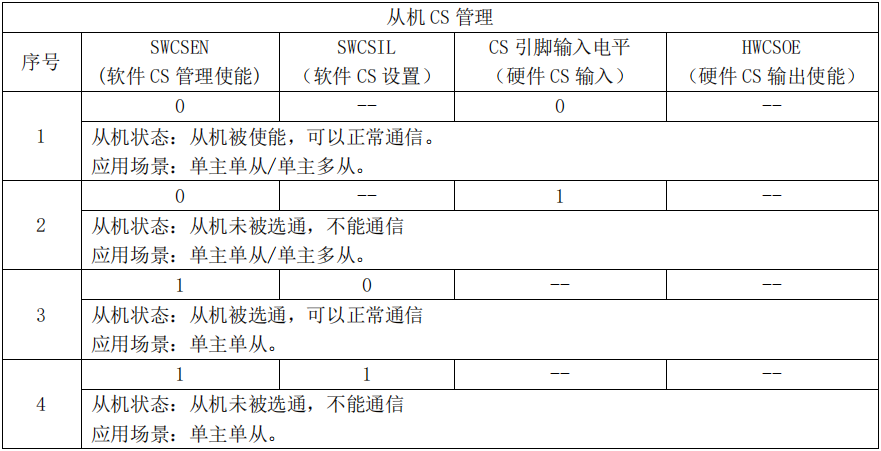

以下分別列出了主機和從機在不同的CS管理模式下的狀態和應用場景。主機CS管理:下表1列出了幾種主機CS管理的配置及應用場景。表1 SPI主機CS管理配置 注:“--”表示此項配置無效,建議保持默認配置。從機CS管理:下表2列出了從機CS管理的幾種配置和應用場景。其中,從模式下HWCSOE配置無效,該位只在主模式下有效。表2 SPI從機CS管理配置

注:“--”表示此項配置無效,建議保持默認配置。從機CS管理:下表2列出了從機CS管理的幾種配置和應用場景。其中,從模式下HWCSOE配置無效,該位只在主模式下有效。表2 SPI從機CS管理配置 注:“--”表示此項配置無效,建議保持默認配置。

注:“--”表示此項配置無效,建議保持默認配置。

CRC校驗

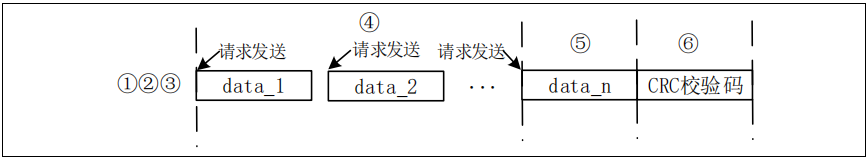

AT32 SPI具有獨立的發送和接收CRC計算單元,用戶可通過軟件配置使能此功能。使能CRC校驗之后:硬件會對發送的數據進行CRC計算,并將計算得到的CRC校驗碼放在SPI_TCRC寄存器中,CRC校驗碼緊接在數據之后發送;且硬件會在接收一筆數據時對接收到的數據進行CRC計算,并將計算得到的CRC校驗碼放在SPI_RCRC寄存器中,硬件會在一筆連續的數據接收完成后將最后接收到的CRC校驗碼與SPI_RCRC寄存器中的校驗碼進行比較,如果不符,CRC校驗錯誤位(CCERR)會置起,若使能了錯誤中斷(ERRIE=1),將會產生中斷。另外,SPI通信方式使用DMA和使用輪詢/中斷方式時,CRC功能的軟件操作步驟有區別,如下:輪詢/中斷方式:①配置CRC多項式:配置SPI_CPOLY寄存器和需要通信的SPI一致(默認值為0x0007);②使能CRC功能:CCEN=1;③使能SPI:SPIEN=1;④發送待發送的數據data_1~data_n;⑤請求發送CRC校驗碼:NTC=1。注:NTC置1的時間參考下圖15的⑤段,需要在最后一筆數據(data_n)寫入數據寄存器到發送完成之間。實際編寫軟件代碼時,建議在data_n寫入數據寄存器之后立即將NTC置1。⑥硬件自動在data_n發送完成后立即發送CRC校驗碼(此時無需軟件參與)。輪詢方式使用CRC功能可參考“案例6--SPI CRC功能使用”。圖15 CRC使用流程(輪詢/中斷方式)

DMA方式:

SPI在使用DMA方式通信時,不需要軟件代碼去設置請求發送CRC校驗碼,即不需要去置位NTC位。具體步驟如下:①配置DMA:請參考“案例2--SPI全雙工DMA方式通信”的DMA配置部分;②配置CRC多項式:配置SPI_CPOLY寄存器和需要通信的SPI一致(默認值為0x0007);③使能CRC功能:CCEN=1;④使能SPI:SPIEN=1;⑤數據及CRC接收完成后需關閉SPI和DMA,之后再開啟,準備下一次通信。

TI模式(TI SSP協議)

AT32 SPI接口支持TI SSP協議,即TI模式。用戶可以通過將TIEN位置1來使能TI模式。使能TI模式后,SPI接口將按照TI協議要求產生時鐘SCK,和片選信號CS。也就是CS軟/硬件管理相關控制位、時鐘極性/相位相關控制位配置無效,請保持默認設置。使能TI模式后,幀格式(8/16bit)配置、CRC校驗、DMA等功能仍然可以使用。TI模式下,連續和不連續通信稍有區別。連續通信時,只有第一筆數據發送時有一個dummy CLK;不連續通信時,每筆數據都有一個dummy CLK。參考下圖16和圖17。TI模式連續通信時序圖見下圖16。主機發送數據(MOSI):0xAA,0xCC,0xAA;從機發送數據(MISO):0xCC,0xAA,0xCC。圖16 TI模式連續通信時序圖 TI模式不連續通信時序圖見下圖17。主機發送數據(MOSI):0xAA,0xCC,0xAA;從機發送數據(MISO):0xCC,0xAA,0xCC。圖17 TI模式不連續通信時序圖

TI模式不連續通信時序圖見下圖17。主機發送數據(MOSI):0xAA,0xCC,0xAA;從機發送數據(MISO):0xCC,0xAA,0xCC。圖17 TI模式不連續通信時序圖 注:AT32只有部分型號支持TI模式。AT32F425/F435/F437等型號支持TI模式,AT32F403/F403A/F407/F413/F415等型號不支持TI模式。具體請參考各型號的RM。

注:AT32只有部分型號支持TI模式。AT32F425/F435/F437等型號支持TI模式,AT32F403/F403A/F407/F413/F415等型號不支持TI模式。具體請參考各型號的RM。

SPI錯誤

AT32的SPI有4種錯誤標志。這4種錯誤標志共用一個錯誤中斷使能位(ERRIE)。也就是當ERRIE=1時,產生以下4種錯誤的任一錯誤就會進入SPI錯誤中斷。CSPAS--CS脈沖異常置位標志在TI模式下,當SPI作從機使用時,SPI會在數據傳輸期間偵測非預期的CS脈沖,當發生CS脈沖異常置位錯誤,CSPAS被硬件置1,如果開啟了錯誤中斷使能(ERRIE=1),則會產生錯誤中斷。之后可以通過軟件讀SPI_STS清除該位。當偵測到CS脈沖異常時,為避免數據錯誤,軟件應當關閉SPI從機,重新配置SPI主機,再打開SPI從機以重新開始通信。注:僅在TI模式下,CSPAS錯誤標志才有效。ROERR--接收器溢出錯誤標志當SPI數據寄存器已暫存一筆待讀數據時,又收到一筆新數據,則會發生接收器溢出錯誤,ROERR被硬件置1,如果開啟了錯誤中斷使能(ERRIE=1),則會產生錯誤中斷。發生溢出錯誤之后,SPI_DT寄存器存放的是最早收到的那筆數據,發生溢出錯誤之后收到的數據都被丟棄。之后依次讀取SPI_DT寄存器和SPI_STS寄存器可清除該標志位。MMERR--主模式錯誤標志參考“CS管理”一節,當SPI主機為CS輸入模式且CS引腳輸入低電平時,會產生主模式錯誤,MMERR位會被硬件置1,且硬件會強制SPI進入從機模式(MSTEN清0)并關閉SPI(SPIEN清0)。如果開啟了錯誤中斷使能(ERRIE=1),則會產生錯誤中斷。清除MMERR標志位并從錯誤狀態恢復請嚴格按照以下步驟執行:①拉高CS引腳電平;②執行一次對SPI_STS寄存器的讀或寫操作;③執行一次對SPI_CTRL1寄存器的寫操作;(不需要改變SPI_CTRL1的值,只需要寫這個動作)④之后硬件會自動清除MMERR標志(此步驟不需要軟件代碼參與);⑤之后軟件可根據需要重新配置主/從模式和使能SPI。CCERR--CRC校驗錯誤標志當使能了CRC功能后,如果接收到的CRC校驗碼(發送方發送的校驗碼)和SPI_RCRC的校驗碼(接收方根據接收到的數據計算的校驗碼)不符,則硬件將CCERR位置1,如果開啟了錯誤中斷使能(ERRIE=1),則會產生錯誤中斷。由于發生了CRC校驗錯誤,軟件程序應當丟棄之前接收到的一筆數據,并重新通信。軟件對CCERR位寫0可清除該標志位。

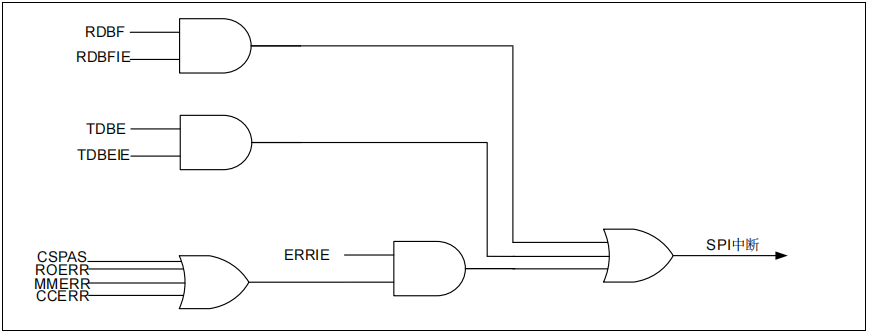

SPI中斷

如下圖18,SPI有一個全局中斷向量。SPI中斷有三個中斷源:接收緩沖器滿、發送緩沖器空、通信錯誤(詳見上一節“SPI錯誤”)。這三個中斷源分別有對應的使能位。下圖中,3個中斷使能位定義如下:

RDBFIE:接收數據緩沖器滿中斷使能

TDBEIE:發送數據緩沖器空中斷使能

ERRIE:錯誤中斷使能

下圖中,5個標志位定義如下:

ROERR:接收器溢出錯誤

MMERR:主模式錯誤

CCERR:CRC校驗錯誤

RDBF:接收數據緩沖器滿

TDBE:發送數據緩沖器空

圖18 SPI中斷示意

I2S功能介紹

I2S硬件接口

I2S接口定義如下:

WS:聲道選擇。由主機輸出,從機輸入。

CK:時鐘。由主機輸出,從機輸入。

MCK:主時鐘輸出(可選)。在通訊期間可提供頻率固定為256倍Fs的外設主時鐘,僅在作為主機時有效。

SD:數據。主機/從機接收或發送數據均通過這個引腳。

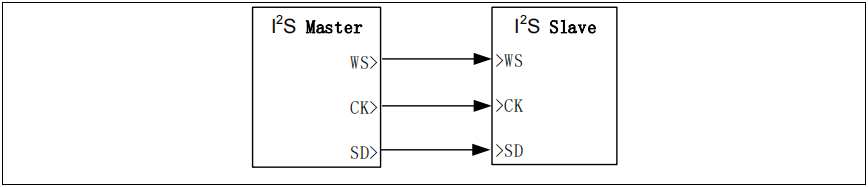

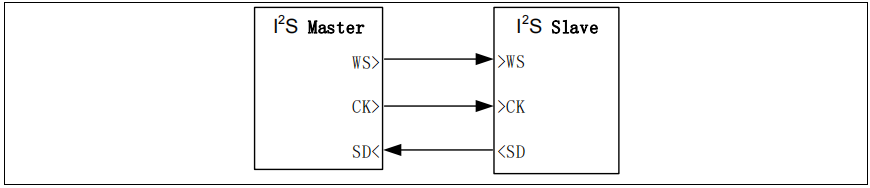

以下是常見的I2S通信接線方式。如下圖19,是I2S主發從收的接線示意圖。圖19 I2S主發從收通信接線示意 如下圖20,是I2S主收從發的接線示意圖。圖20 I2S主收從發通信接線示意

如下圖20,是I2S主收從發的接線示意圖。圖20 I2S主收從發通信接線示意

I2S數據接收和發送

I2S數據收發模塊和上文的SPI共用數據寄存器和DMA映射,如上圖5中的接收/發送緩沖器、移位寄存器也都是共用的,因此軟件代碼操作類似,請參考下文的I2S案例一節。不過SPI默認是全雙工,而I2S默認是半雙工。AT32也為用戶提供I2S全雙工功能,后文I2S全雙工一節詳細介紹。

I2S音頻協議

AT32的I2S支持以下4種標準協議:

飛利浦標準:STDSLE=0b00;

高字節對齊標準(左對齊):STDSLE=0b01;

低字節對齊標準(右對齊):STDSLE=0b10;

PCM標準:STDSLE=0b11。

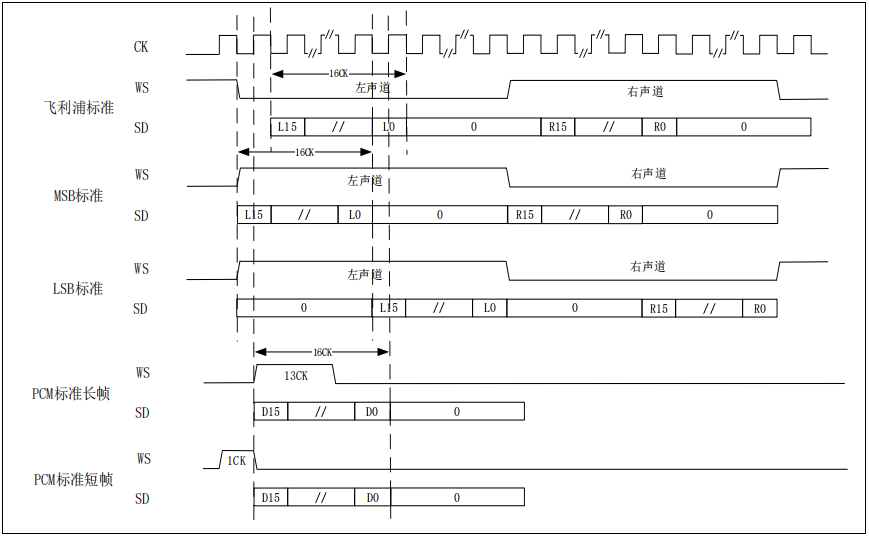

其中PCM標準又分為:1、PCM長幀同步:PCMFSSEL=1;2、PCM短幀同步:PCMFSSEL=0。下圖21在“16位數據-32位聲道格式”,I2S時鐘極性為低(I2SCLKPOL=0)條件下對比了幾種音頻標準一幀數據的通信時序。飛利浦模式下:WS為低電平表示正在傳輸的聲道為左聲道,WS為高電平表示正在傳輸的聲道為右聲道。數據左對齊,即高位對齊,低位的16個bit被硬件填充為0。MSB標準下:WS為高電平表示正在傳輸的聲道為左聲道,WS為低電平表示正在傳輸的聲道為右聲道。數據左對齊,即高位對齊,低位的16個bit被硬件填充為0。LSB標準下:WS為高電平表示正在傳輸的聲道為左聲道,WS為低電平表示正在傳輸的聲道為右聲道。數據右對齊,即低位對齊,高位的16個bit被硬件填充為0。注:LSB標準下,數據發送順序還是高位在前。PCM標準長幀下:沒有左右聲道之分,WS的脈沖代表同步信號而不是左右聲道。WS脈沖長度為13個CK長度。PCM標準短幀下:沒有左右聲道之分,WS的脈沖代表同步信號而不是左右聲道。WS脈沖長度為1個CK長度。圖21 I2S各音頻標準時序對比

I2S幀格式

AT32的I2S支持3種數據位個數選擇:

16位:I2SDBN=0b00

24位:I2SDBN=0b01

32位:I2SDBN=0b10

AT32的I2S支持2種聲道位個數選擇:

16位:I2SDBN=0

32位:I2SDBN=1

數據位個數和聲道位個數組合有以下4種幀格式:①16位數據-16位聲道格式:I2SDBN=0b00,I2SDBN=0;②16位數據-32位聲道格式:I2SDBN=0b00,I2SDBN=1;③24位數據-32位聲道格式:I2SDBN=0b01,I2SDBN=1;④32位數據-32位聲道格式:I2SDBN=0b10,I2SDBN=1;上述的第②、③幀格式中,由于聲道位個數>數據位個數。此時硬件會自動將多余的聲道位填充為0。可參考上圖21中,“16位數據-32位聲道格式”的時序。上述的①、②幀格式,在接收/發送數據時,僅需要讀取/寫入一次16bit的DT寄存器;而③、④幀格式,在接收/發送數據時,需要讀取/寫入兩次16bit的DT寄存器。

I2S時鐘控制器

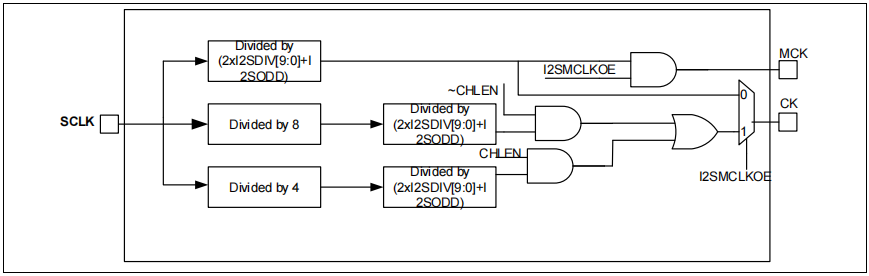

I2S采樣率(Fs)常見的音頻的采樣頻率有:192KHz、96kHz、48kHz、44.1kHz、32kHz、22.05kHz、16kHz、11.025kHz、8kHz等。而實際上AT32的I2S可以產生以上范圍內的任何采樣率。例如采樣率為192K,則表示每秒可傳輸192K幀音頻數據。對于飛利浦/MSB/LSB標準而言,一幀音頻數據包含左、右通道兩筆16/32bit的數據;對于PCM標準而言,一幀數據僅包含一筆16/32bit的數據。I2S時鐘(CK)和主時鐘(MCK)如下圖22,I2S的時鐘從系統時鐘SCLK分頻得來。不過使用I2S時仍然需要使能掛載在APB時鐘總線上的SPI接口時鐘(SPIxEN=1),以用于I2S邏輯控制器等。

當需要輸出主時鐘(I2SMCLKOE=1),聲道位個數為16bit(I2SDBN=0)時:

Fs=SCLK/[(16*2)*((2*I2SDIV)+I2SODD)*8];

當需要輸出主時鐘(I2SMCLKOE=1),聲道位個數為32bit(I2SDBN=1)時:

Fs=SCLK/[(32*2)*((2*I2SDIV)+I2SODD)*4];

當不需要輸出主時鐘(I2SMCLKOE=0),聲道位個數為16bit(I2SDBN=0)時:

Fs=SCLK/[(16*2)*((2*I2SDIV)+I2SODD)];

當不需要輸出主時鐘(I2SMCLKOE=0),聲道位個數為32bit(I2SDBN=1)時:

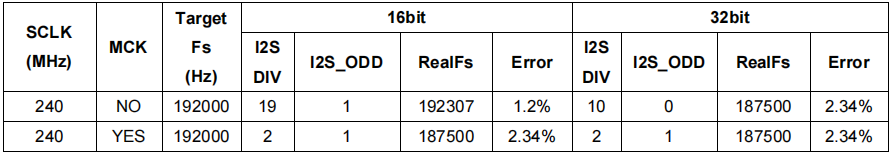

Fs=SCLK/[(32*2)*((2*I2SDIV)+I2SODD)];圖22 I2S時鐘 如下表3,示例了系統時鐘為240MHz時,配置192K的采樣率推薦的I2S時鐘配置方案。表3 I2S時鐘配置方案示例

如下表3,示例了系統時鐘為240MHz時,配置192K的采樣率推薦的I2S時鐘配置方案。表3 I2S時鐘配置方案示例

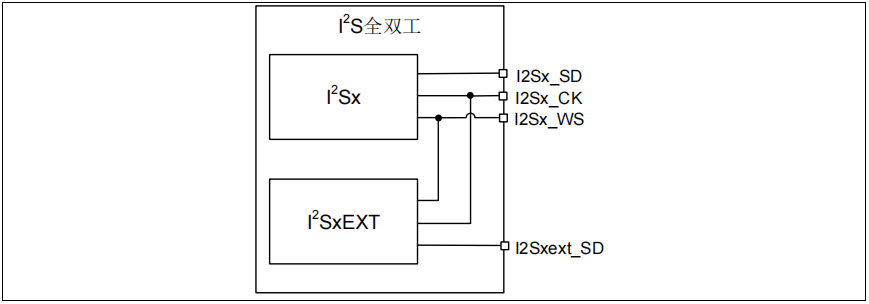

I2S全雙工

AT32F403A/F407/F435/F437/F425等型號支持I2S全雙工,AT32F403/F413/F415/F421等型號不支持I2S全雙工,具體請參考對應型號RM文檔。不同型號MCU的I2S全雙工實現方式也有所區別,本文會分別介紹AT32F403A/F407/F435/F437和AT32F425的I2S全雙工功能。AT32F403A/F407/F435/F437的I2S全雙工AT32F403A/F407/F435/F437為了支持I2S全雙工模式,額外例化了兩個I2S模塊(I2S2EXT,I2S3EXT)。I2S2可與I2S2EXT組合在一起支持全雙工模式,I2S3可與I2S3EXT組合在一起支持全雙工模式。代碼可參考“案例3—AT32F403A/F407/F435/F437I2S全雙工DMA方式通信”。在I2Sx可與I2SxEXT組成全雙工模塊時,I2Sx可配置為主或從模式,I2SxEXT只能配置為從模式。I2SxEXT共享I2Sx的CK和WS,對應的有以下幾種配置方式:

I2Sx主發(OPERSEL=0b10);I2SxEXT從收(OPERSEL=0b01);

I2Sx主收(OPERSEL=0b11);I2SxEXT從發(OPERSEL=0b00)。

I2Sx從發(OPERSEL=0b00);I2SxEXT從收(OPERSEL=0b01);

I2Sx從收(OPERSEL=0b01);I2SxEXT從發(OPERSEL=0b00)。

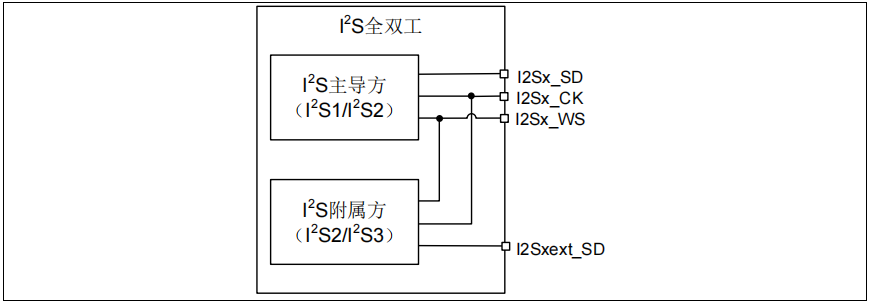

注:I2S2EXT和I2S3EXT只用于I2S全雙工模式,而不能單獨使用。圖23 I2S全雙工結構圖 AT32F425的I2S全雙工AT32F425的I2S全雙工實現方式和AT32F403A/F407/F435/F437不同。AT32F425可以通過設置SCFG_CFG2寄存器中的I2S_FD將兩個SPI組合在一起實現I2S全雙工。代碼可參考“案例4—AT32F425I2S全雙工DMA方式通信”。CK和WS由I2S主導方提供,附屬方的CK和WS對應引腳可以釋放給其他功能使用。根據I2S_FD配置,有以下幾種組合方式:

AT32F425的I2S全雙工AT32F425的I2S全雙工實現方式和AT32F403A/F407/F435/F437不同。AT32F425可以通過設置SCFG_CFG2寄存器中的I2S_FD將兩個SPI組合在一起實現I2S全雙工。代碼可參考“案例4—AT32F425I2S全雙工DMA方式通信”。CK和WS由I2S主導方提供,附屬方的CK和WS對應引腳可以釋放給其他功能使用。根據I2S_FD配置,有以下幾種組合方式:

I2S_FD=0b00:I2S1~3各自獨立半雙工工作;

I2S_FD=0b01:I2S1和I2S3組成全雙工模式,其中I2S1為主導方,I2S3為附屬方。

I2S_FD=0b10:I2S2和I2S3組成全雙工模式,其中I2S2為主導方,I2S3為附屬方。

I2S_FD=0b11:I2S1和I2S2組成全雙工模式,其中I2S1為主導方,I2S2為附屬方。

圖24 I2S全雙工結構圖

I2S錯誤

ROERR--接收器溢出錯誤標志此錯誤標志和SPI一樣,請參考前文“2.9.2 ROERR--接收器溢出錯誤標志”。TUERR--發送器欠載錯誤標志位在I2S從發模式下,如果在CK上檢測到了數據驅動沿,但新的發送數據并沒有被寫入數據寄存器,則會產生發送器欠載錯誤,此時硬件會將TUERR位置1。軟件讀SPI_STS寄存器可清除該標志位。此錯誤標志僅使用I2S時有效。

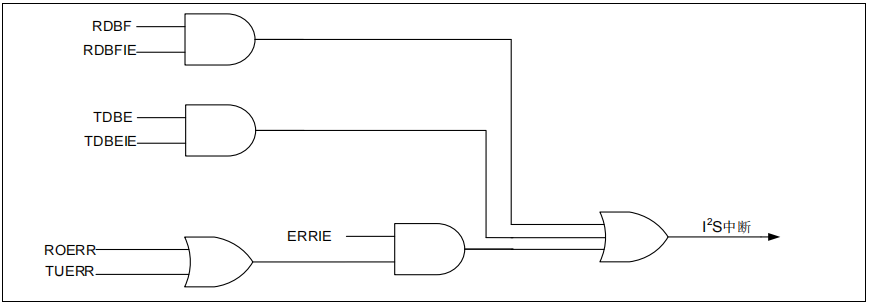

I2S中斷

I2S和SPI共用一個全局中斷向量,即下圖25的“I2S中斷”和上圖18中的“SPI中斷”共用同一個中斷向量。I2S中斷有三個中斷源:接收緩沖器滿、發送緩沖器空、通信錯誤(詳見上一節“I2S錯誤”)。這三個中斷源分別有對應的使能位。下圖中,3個中斷使能位定義如下:

RDBFIE:接收數據緩沖器滿中斷使能(和SPI一樣)

TDBEIE:發送數據緩沖器空中斷使能(和SPI一樣)

ERRIE: 錯誤中斷使能(和SPI一樣)

下圖中,4個標志位定義如下:

ROERR:接收器溢出錯誤(和SPI一樣)

TUERR:發送器欠載錯誤(僅I2S有這個錯誤標志)

RDBF:接收數據緩沖器滿(和SPI一樣)

TDBE:發送數據緩沖器空(和SPI一樣)

圖25 I2S中斷示意

SPI案例

注:所有project都是基于keil5而建立,若用戶需要在其他編譯環境上使用,請參考AT32xxx_Firmware_Library_V2.x.x\project\at_start_xxx\templates中各種編譯環境(例如IAR6/7,keil4/5)進行簡單修改即可。

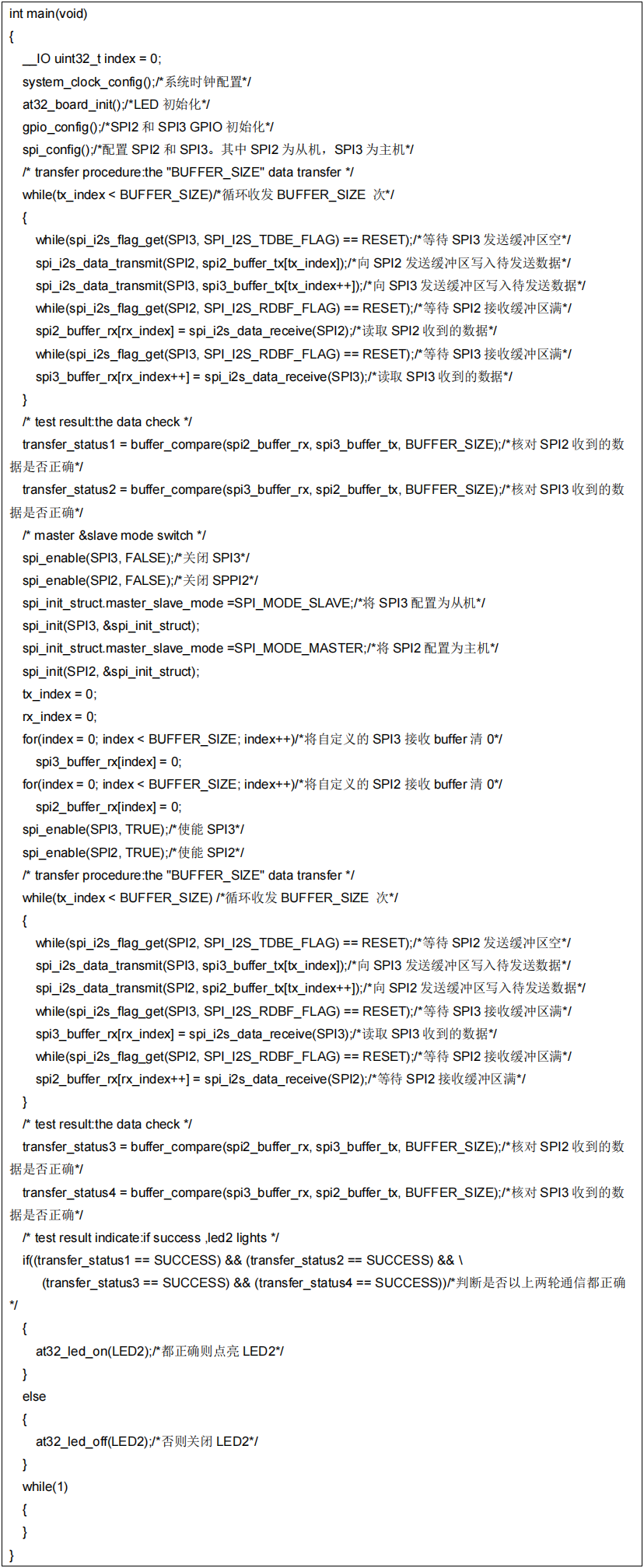

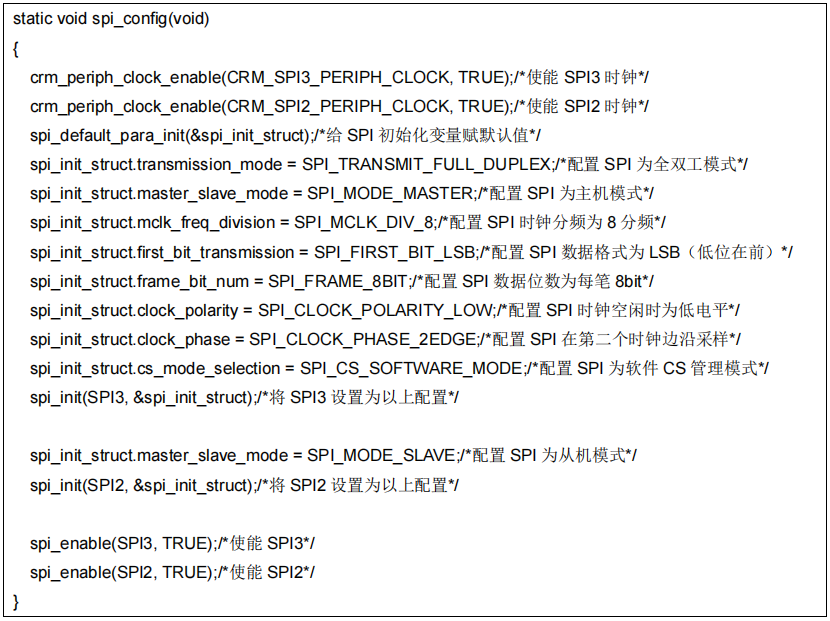

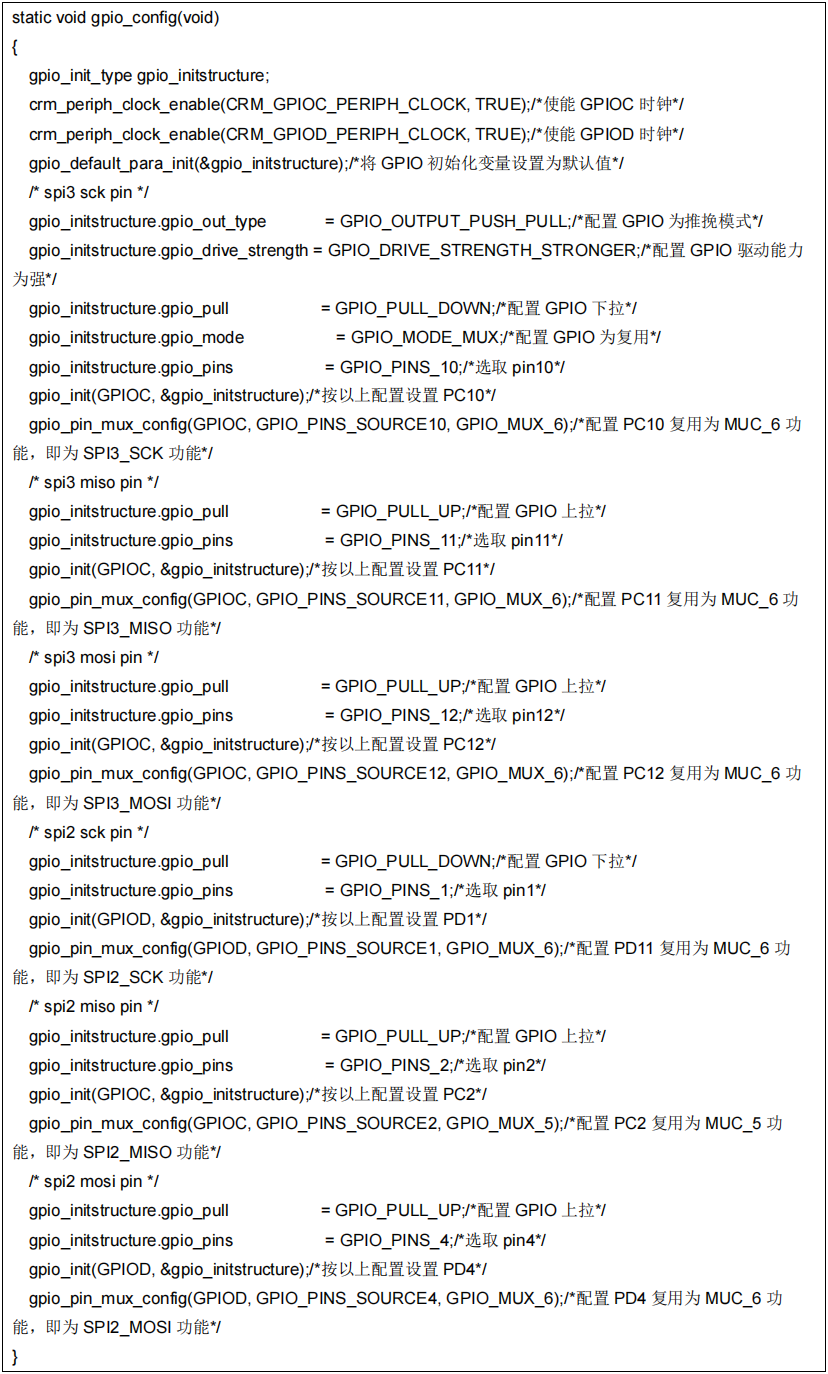

案例1-SPI全雙工輪詢方式通信

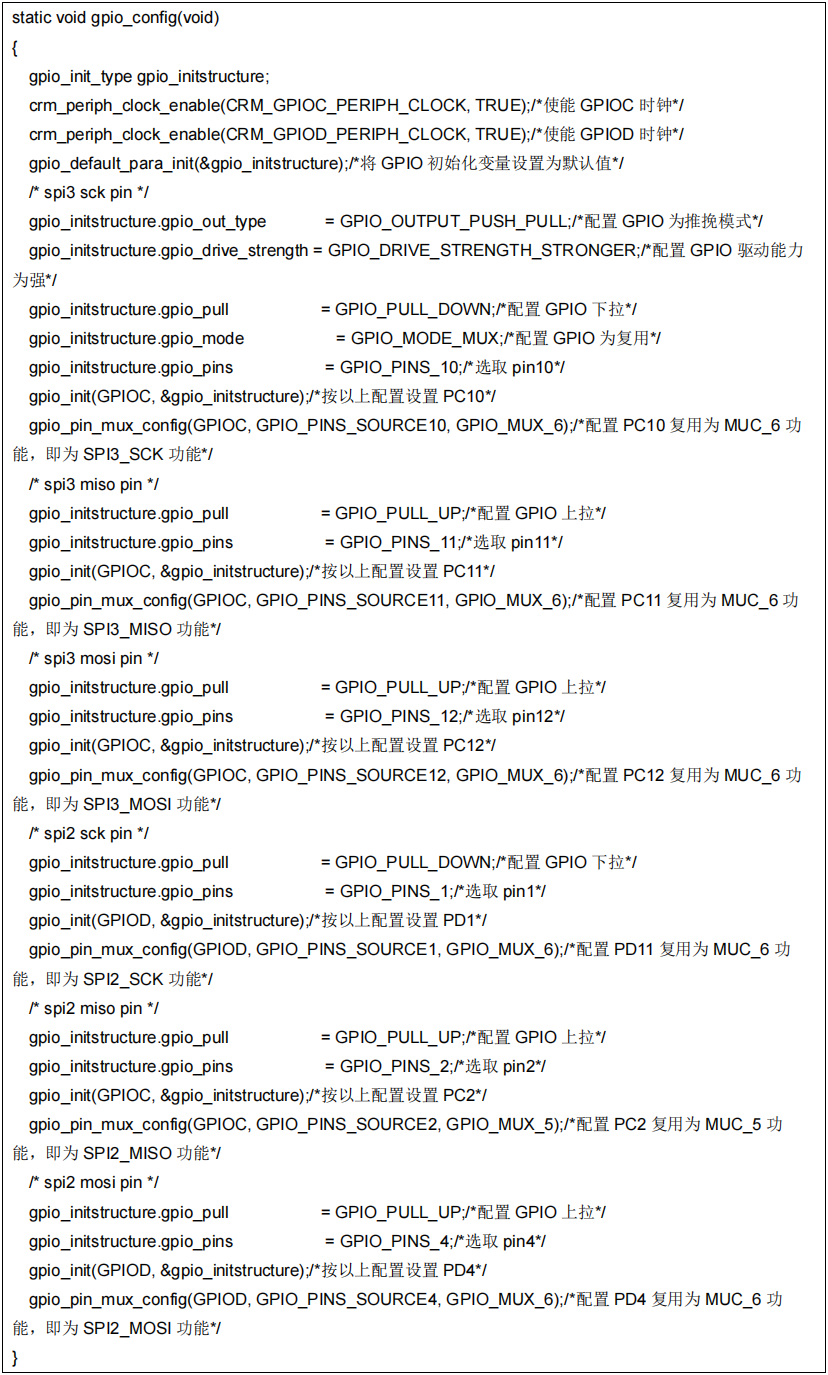

功能簡介實現SPI2和SPI3之間的全雙工輪詢通信。接線如下:spi2 spi3pd1(sck)<--->pc10(sck)pc2(miso)<--->pc11(miso)pd4(mosi)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\spi\fullduplex_polling軟件設計1)配置流程

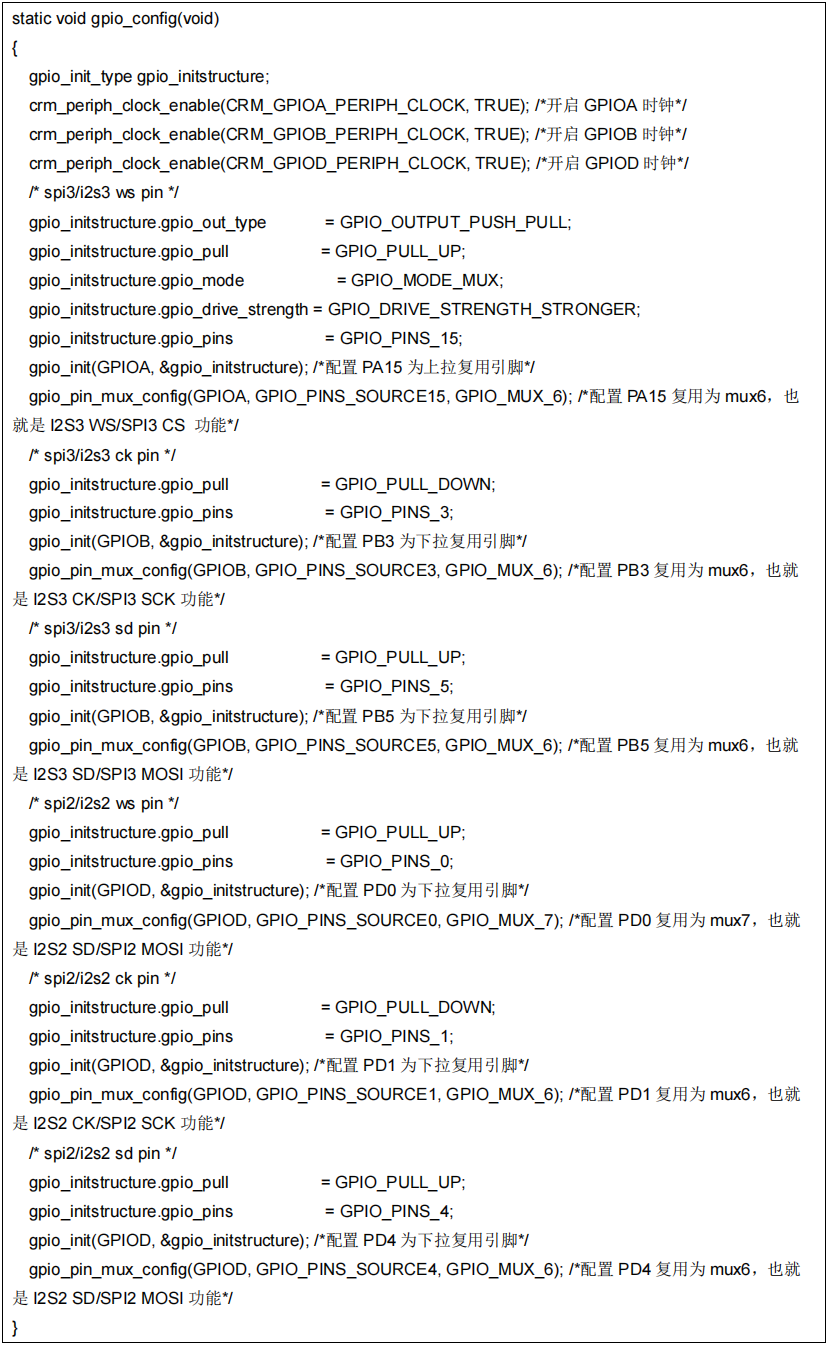

配置SPI2和SPI3對應的GPIO;

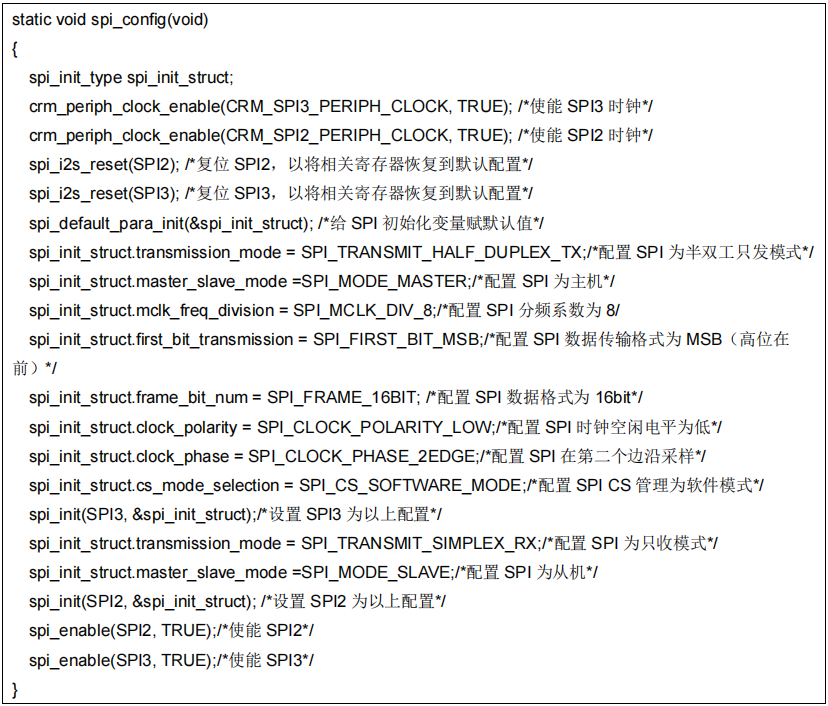

配置SPI2和SPI3通信配置;

開始輪詢通信。

2)代碼介紹

main函數代碼描述

- SPI通信配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

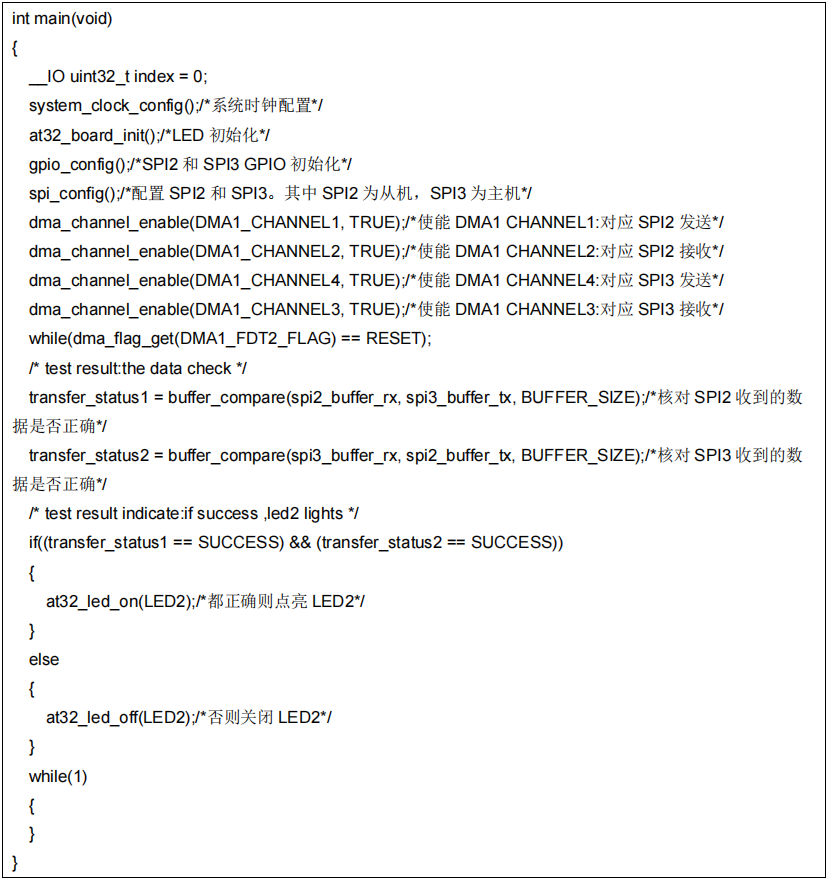

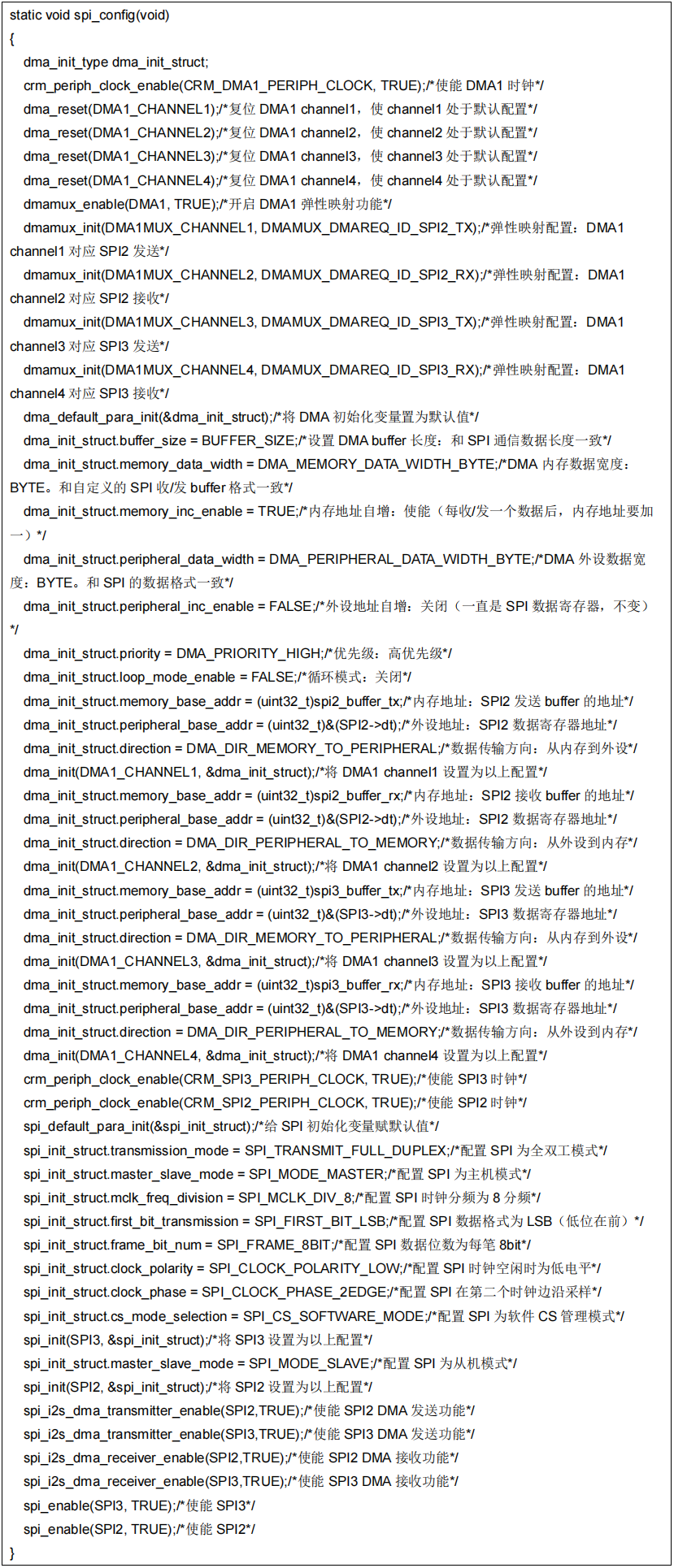

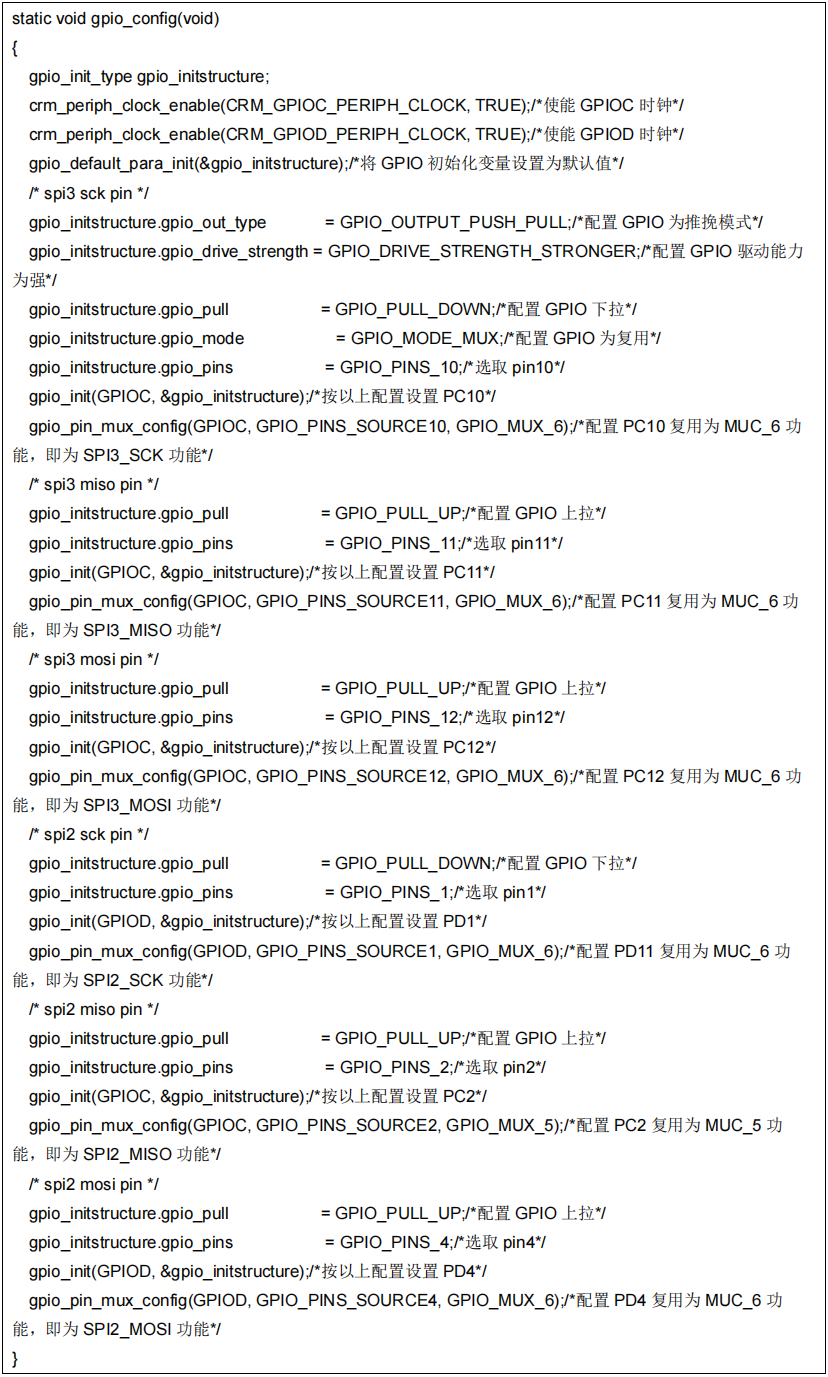

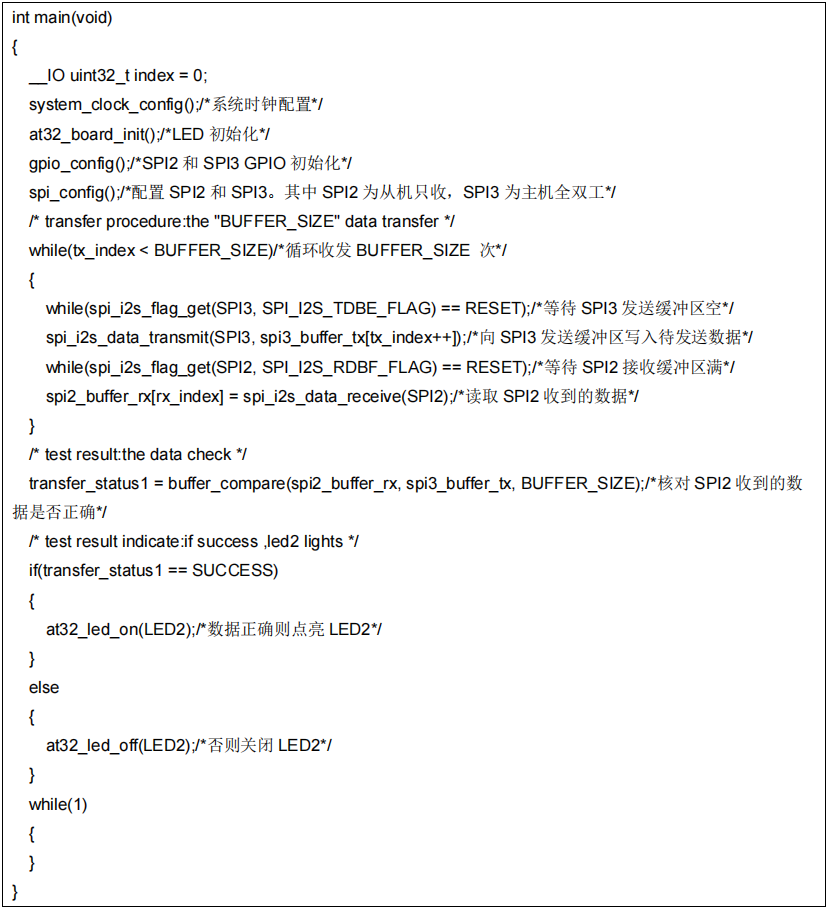

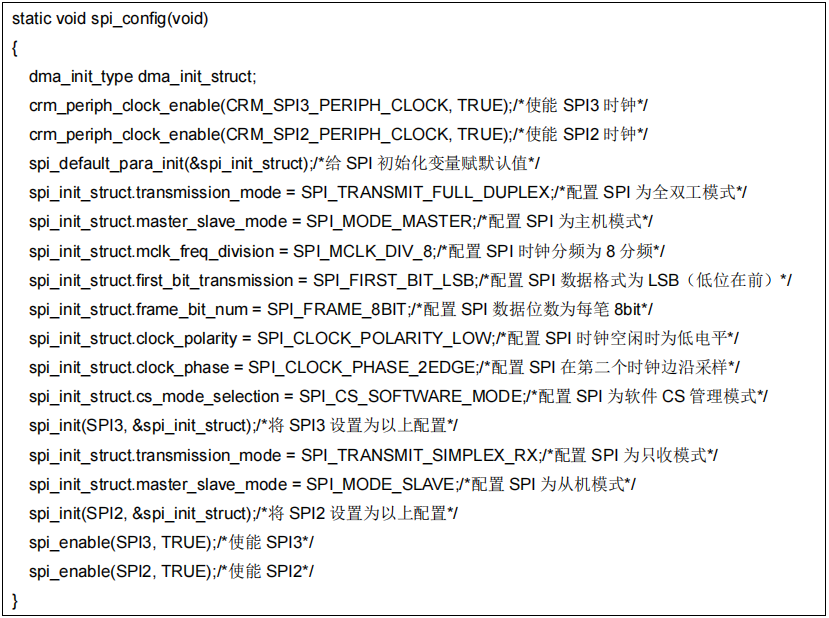

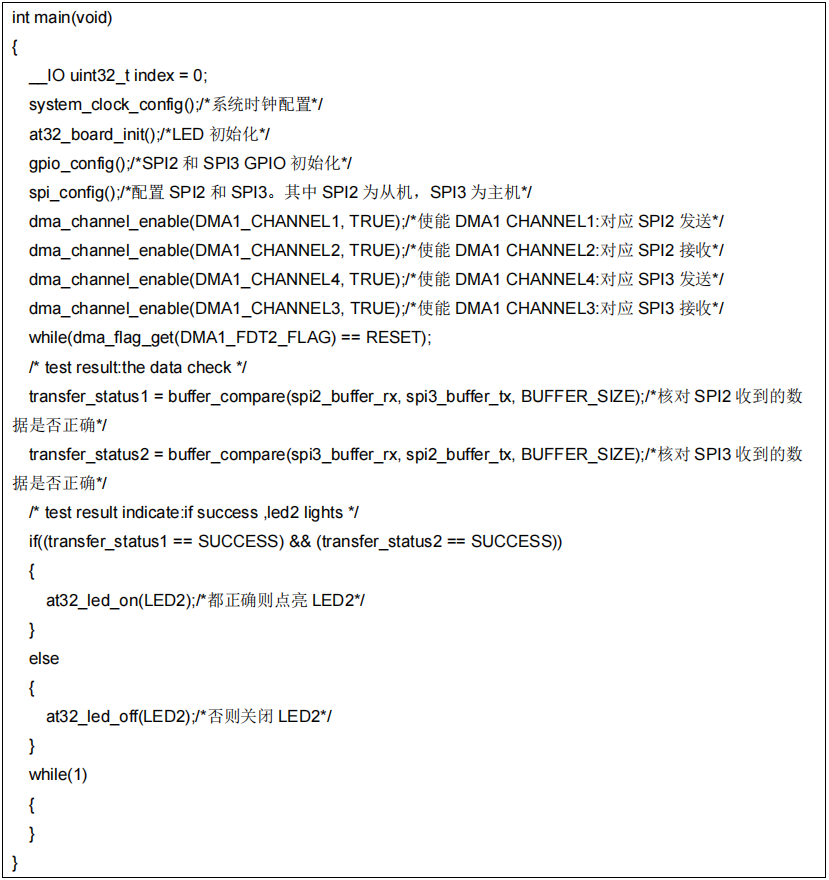

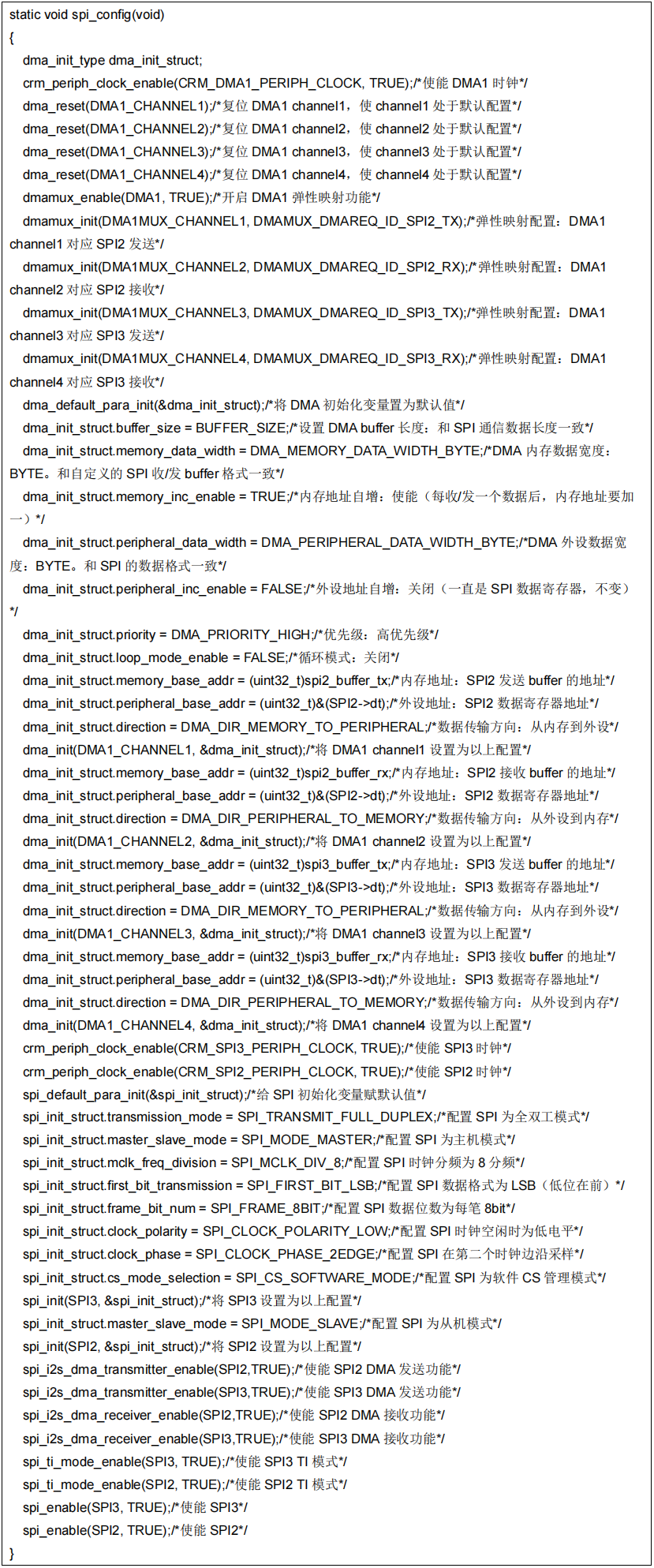

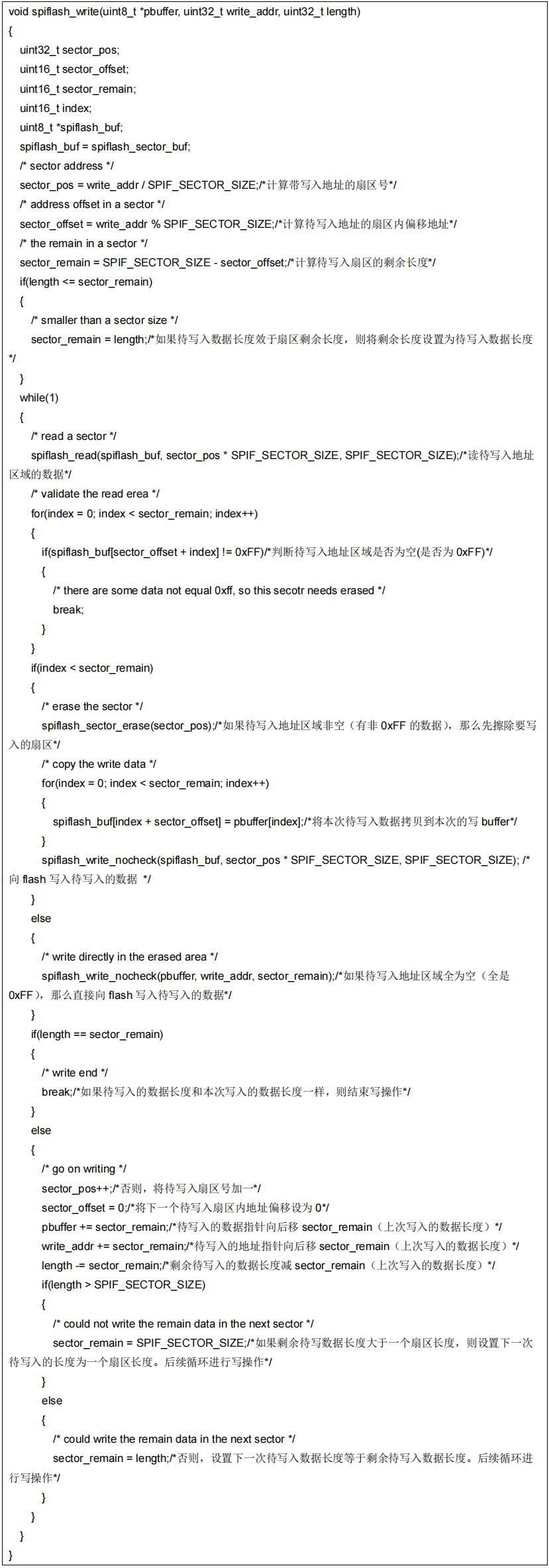

案例2-SPI全雙工DMA方式通信

功能簡介實現SPI2和SPI3之間的全雙工DMA通信。接線如下:spi2 spi3pd1(sck)<--->pc10(sck)pc2(miso)<--->pc11(miso)pd4(mosi)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\spi\motorola_fullduplex_dma軟件設計1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 配置SPI2和SPI3的通信配置和DMA配置;

- 開始DMA通信。

2)代碼介紹

- main函數代碼描述

- SPI通信配置及DMA配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

案例3-SPI只收通信

功能簡介實現SPI2和SPI3之間的單向只收通信。接線如下:spi2 spi3pd1(sck)<--->pc10(sck)pd4(mosi)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\spi\only_receive_mode_polling軟件設計1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 配置SPI2和SPI3的通信配置;

- 開始輪詢通信。

2)代碼介紹

- main函數代碼描述

- SPI通信配置代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

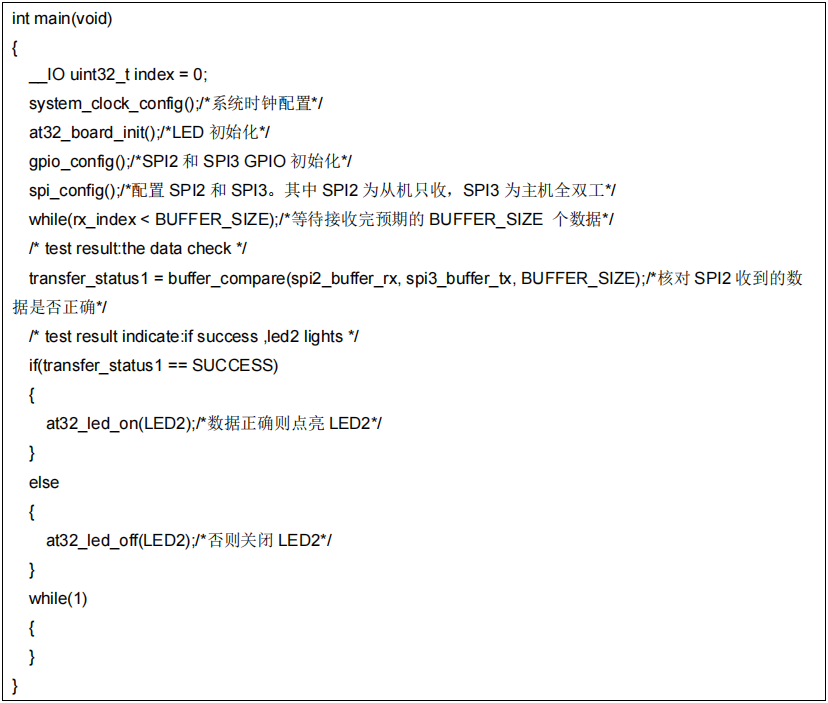

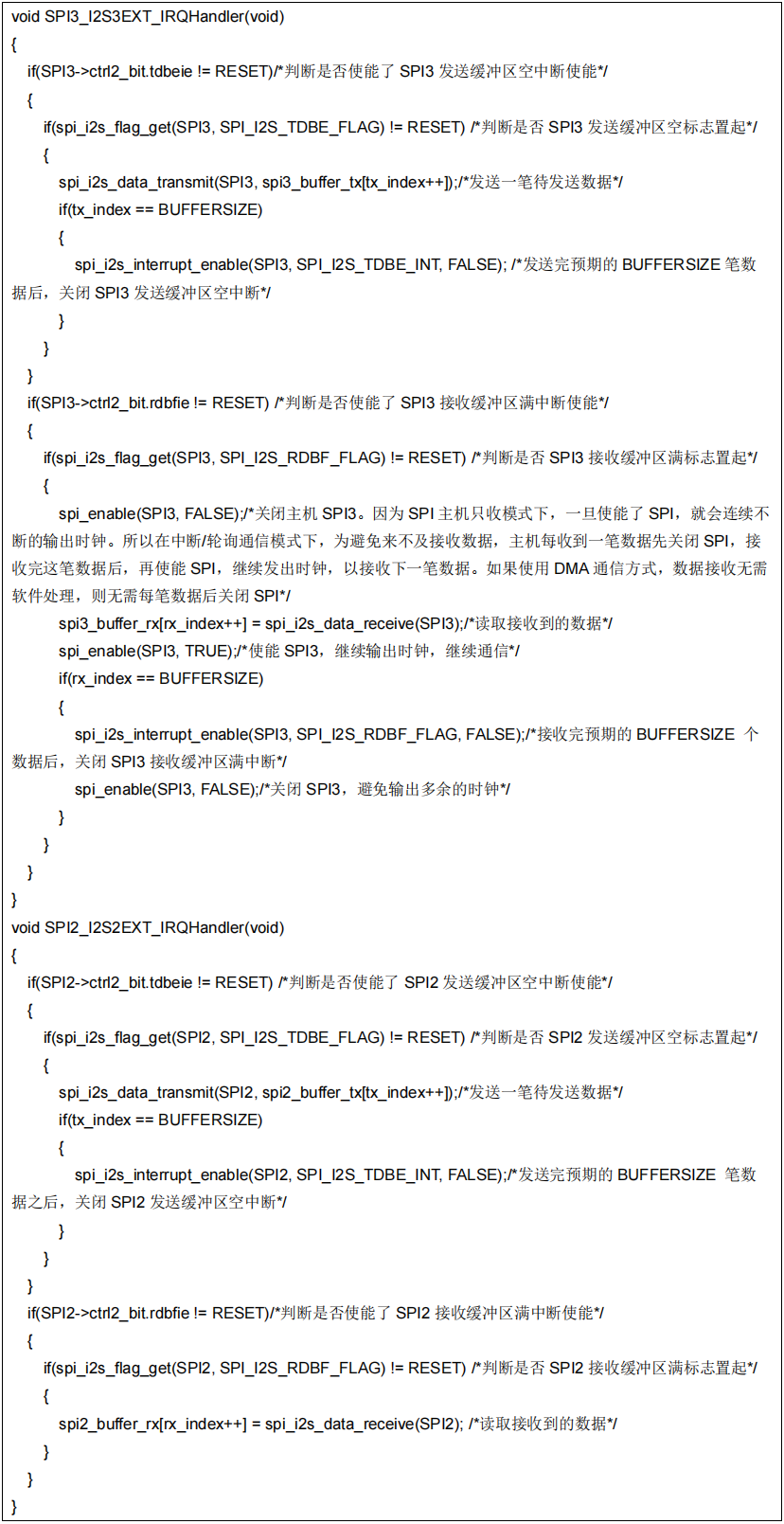

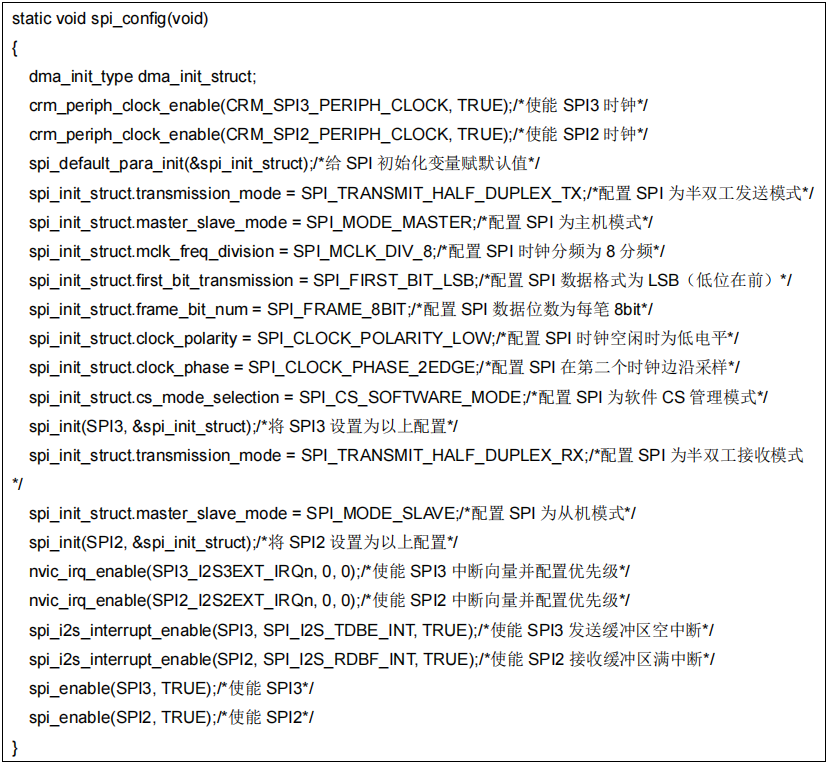

案例4-SPI半雙工中斷方式通信

功能簡介

實現SPI2和SPI3之間的半雙工通信。接線如下:spi2 spi3pd1(sck)<--->pc10(sck)pc2(miso)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_xxxx\examples\spi\halfduplex_interrupt軟件設計1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 設置SPI2和SPI3的中斷處理函數;

- 配置SPI2和SPI3的通信配置;

- 開始中斷通信。

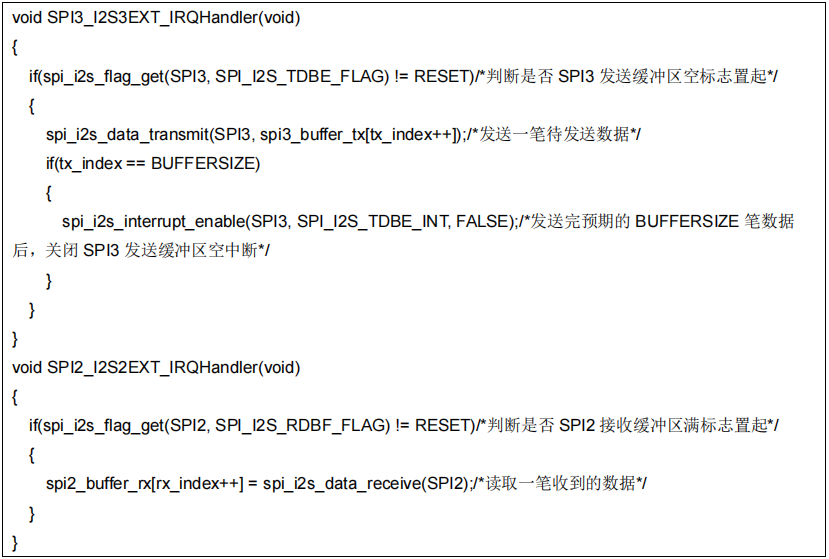

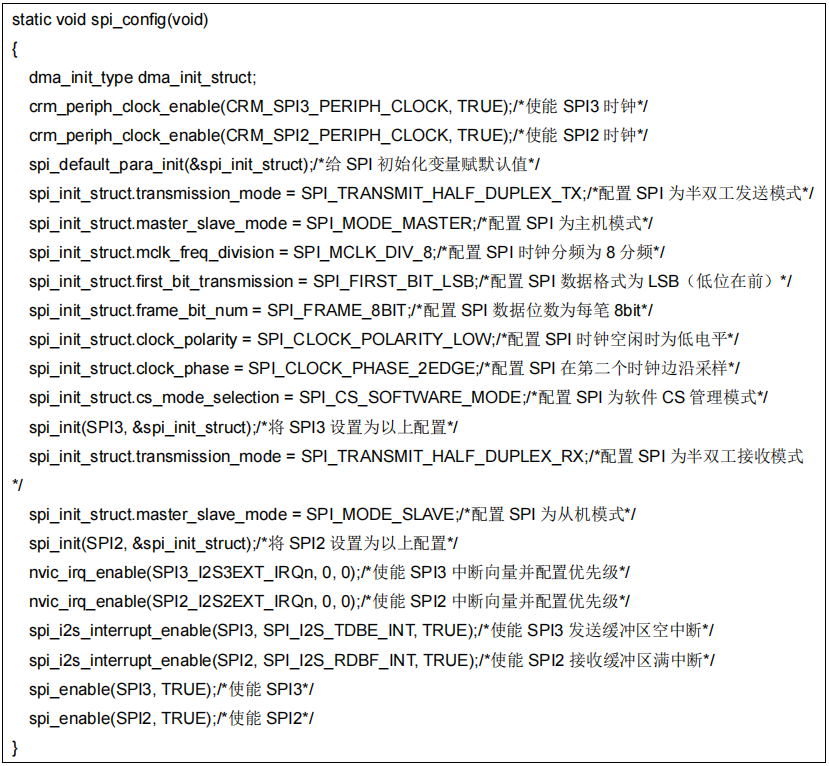

2)代碼介紹

- main函數代碼描述

- 中斷處理函數代碼描述

- SPI通信配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

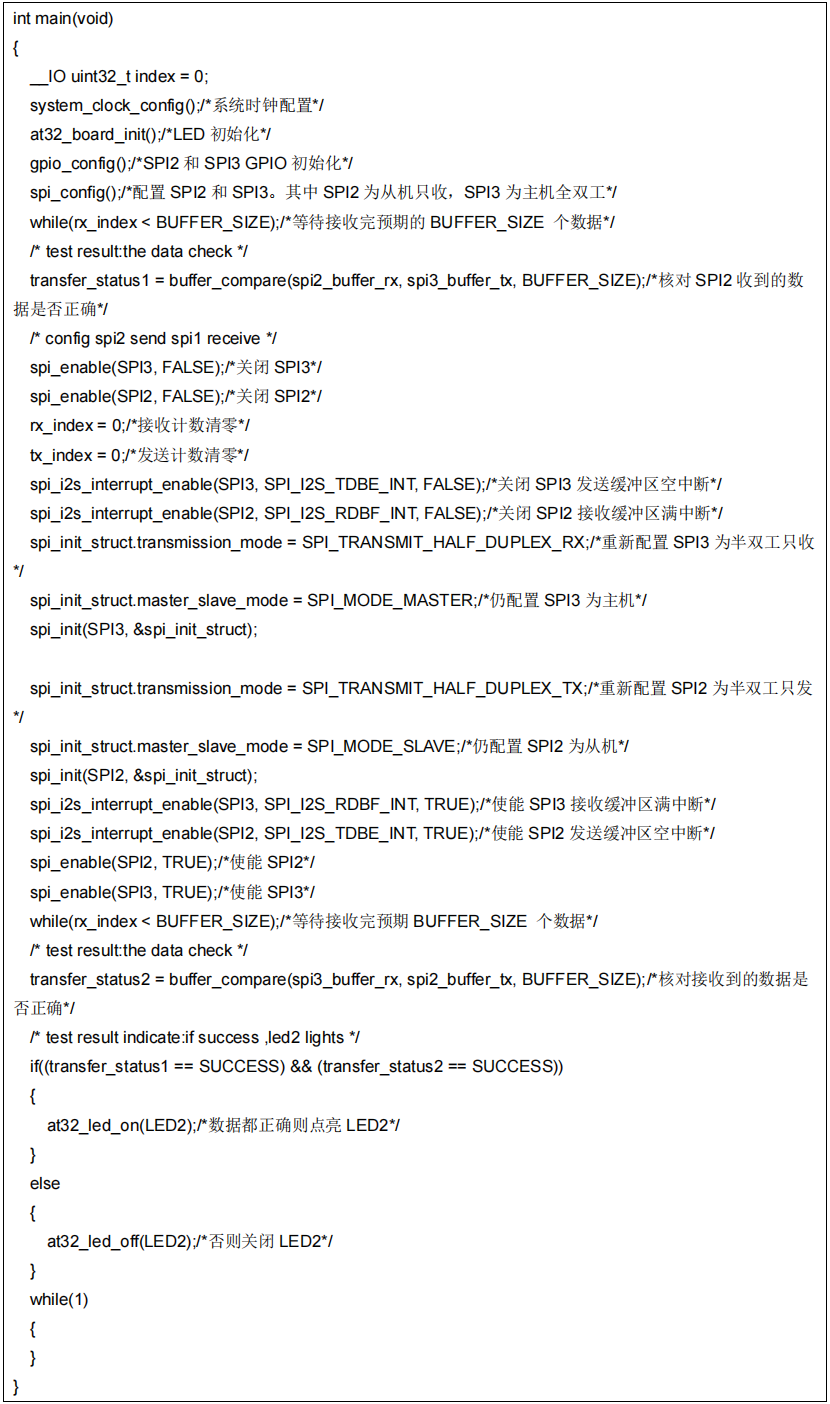

案例5-SPI半雙工中斷方式通信-加收發切換

功能簡介實現SPI2和SPI3之間的半雙工收發切換通信。接線如下:spi2spi3pd1(sck)<--->pc10(sck)pc2(miso)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\spi\halfduplex_transceiver_switch軟件設計

1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 設置SPI2和SPI3的中斷處理函數;

- 配置SPI2和SPI3的通信配置;

- 開始中斷通信。

2)代碼介紹

- main函數代碼描述

- 中斷處理函數代碼描述

- SPI通信配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

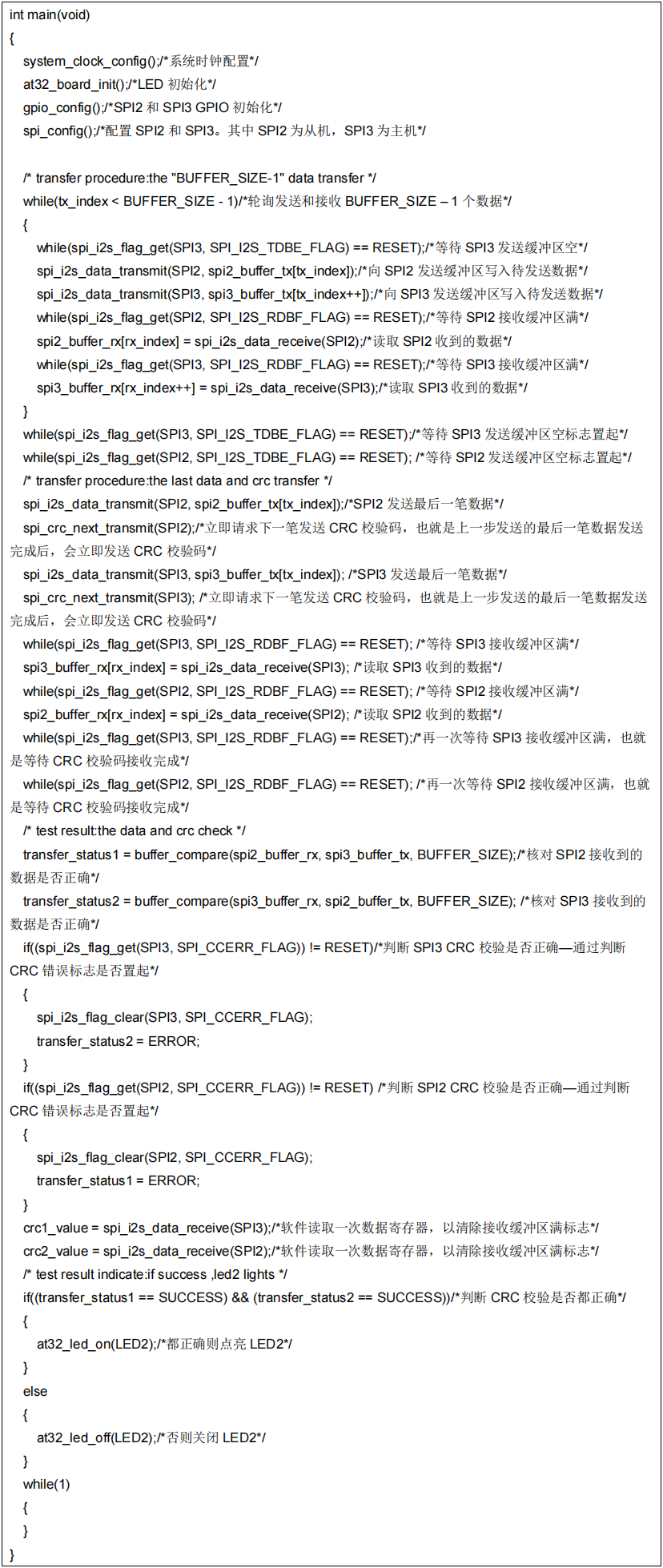

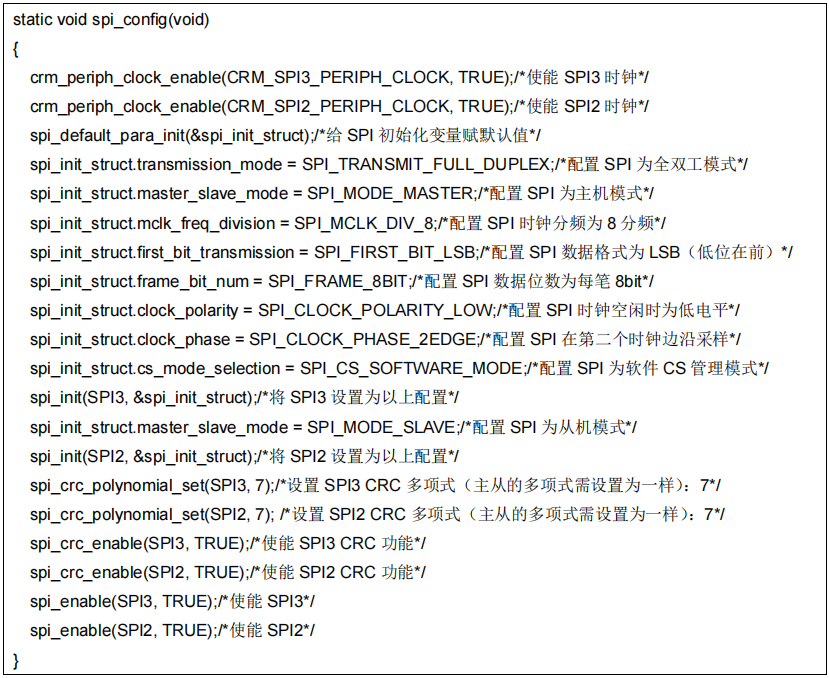

案例6-SPI CRC功能使用

功能簡介實現SPI2和SPI3之間的全雙工通信和CRC校驗。接線如下:spi2 spi3pd1(sck)<--->pc10(sck)pc2(miso)<--->pc11(miso)pd4(mosi)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\spi\crc_transfer_polling軟件設計1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 配置SPI2和SPI3通信配置;

- 開始輪詢通信和CRC校驗。

2)代碼介紹

- main函數代碼描述

- SPI通信配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

案例7-SPI TI模式使用(TI SSP協議)

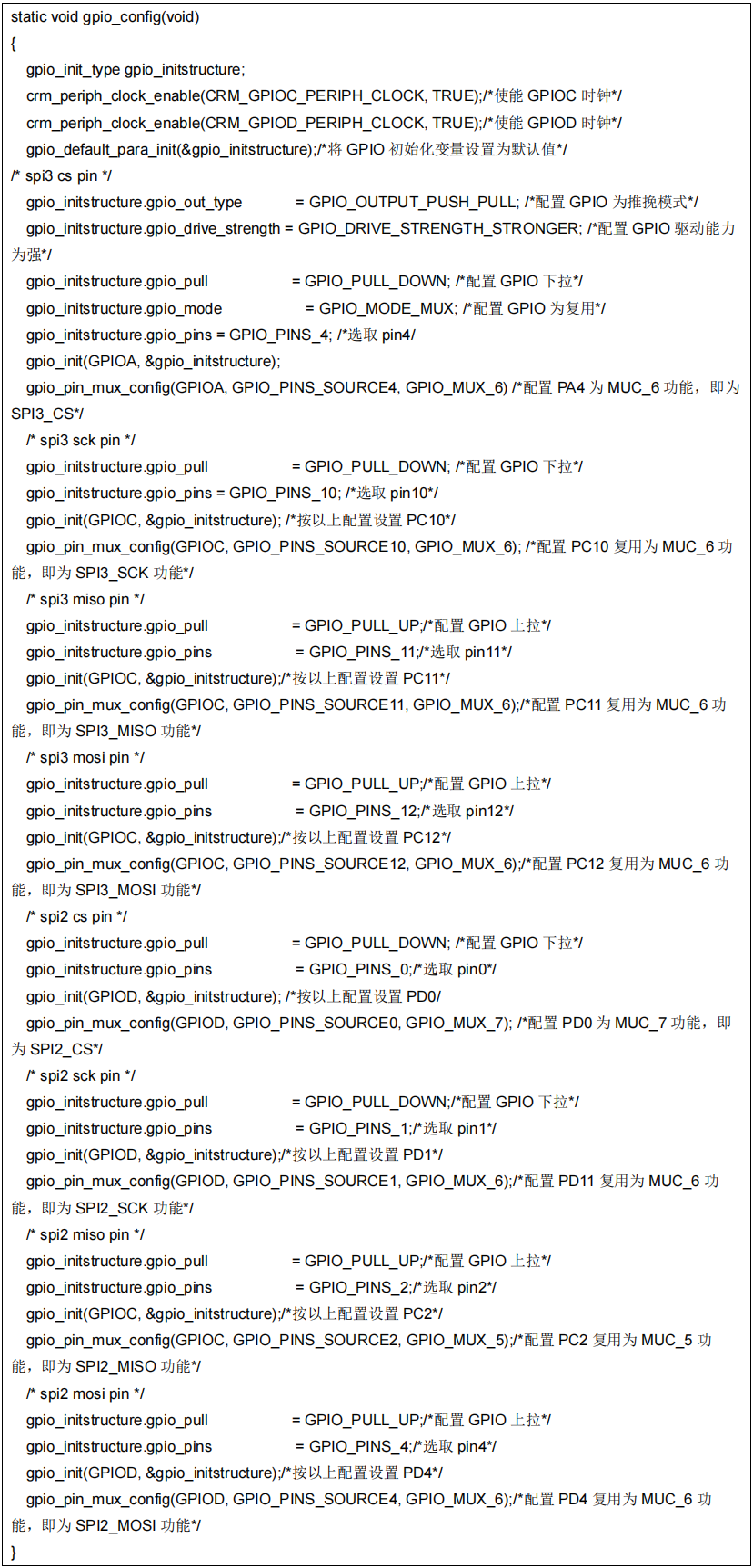

功能簡介實現SPI2和SPI3之間的TI模式DMA通信。接線如下:spi2 spi3pd0(cs)<--->pa4(cs)pd1(sck)<--->pc10(sck)pc2(miso)<--->pc11(miso)pd4(mosi)<--->pc12(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\spi\ti_fullduplex_dma軟件設計1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 配置SPI2和SPI3的通信配置和DMA配置;

- 開始DMA通信。

2)代碼介紹

- main函數代碼描述

- SPI通信配置及DMA配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

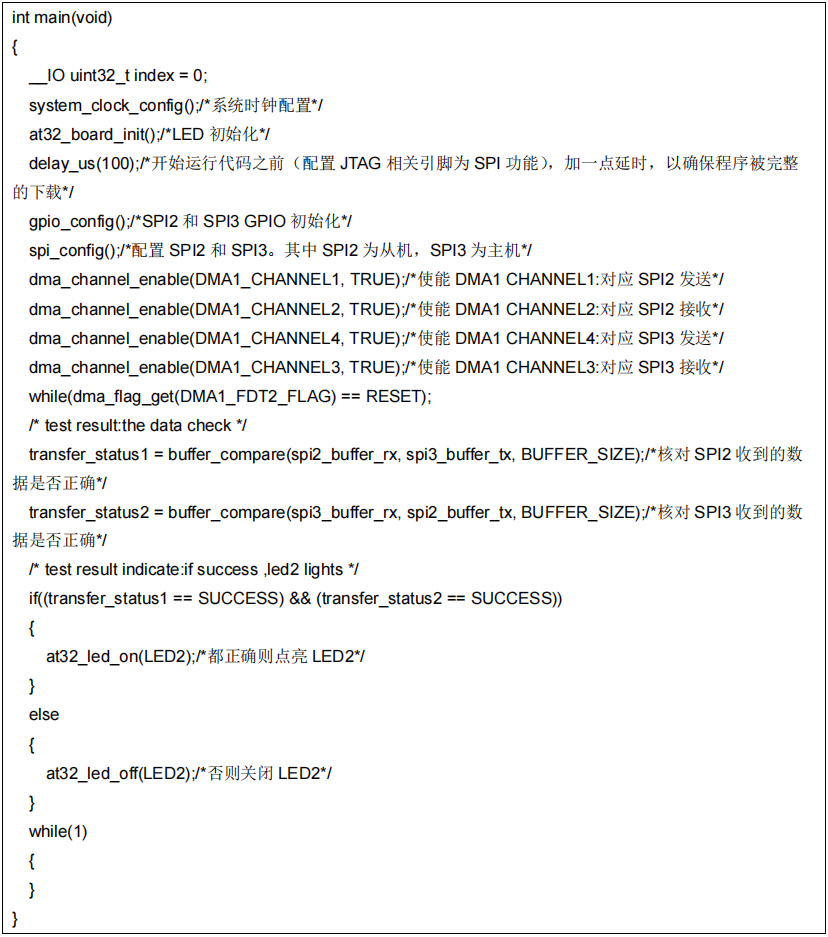

案例8-SPI讀寫FLASH(W25Q128)

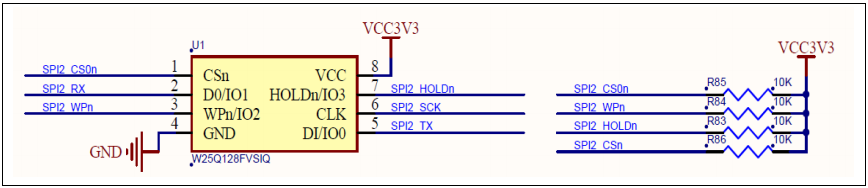

功能簡介實現SPI2讀/寫flash(w25q128)。接線如下:spi2 w25q128pd0(cs)<--->cspinpd1(sck)<--->clk pinpc2(miso)<--->di pinpd4(mosi)<--->do pin資源準備1)硬件環境:一塊AT32F437的AT-START BOARD和w25q128電路板w25q128建議電路如下圖26:圖26 w25q128建議電路 2)軟件環境:project\at_start_f437\examples\spi\w25q_flash軟件設計1)配置流程

2)軟件環境:project\at_start_f437\examples\spi\w25q_flash軟件設計1)配置流程

- 配置SPI2和對應GPIO;

- 讀取flash ID;

- 擦除flash扇區;

- 向flash寫入數據;

- 讀取上一步flash寫入數據的區域。

2)代碼介紹

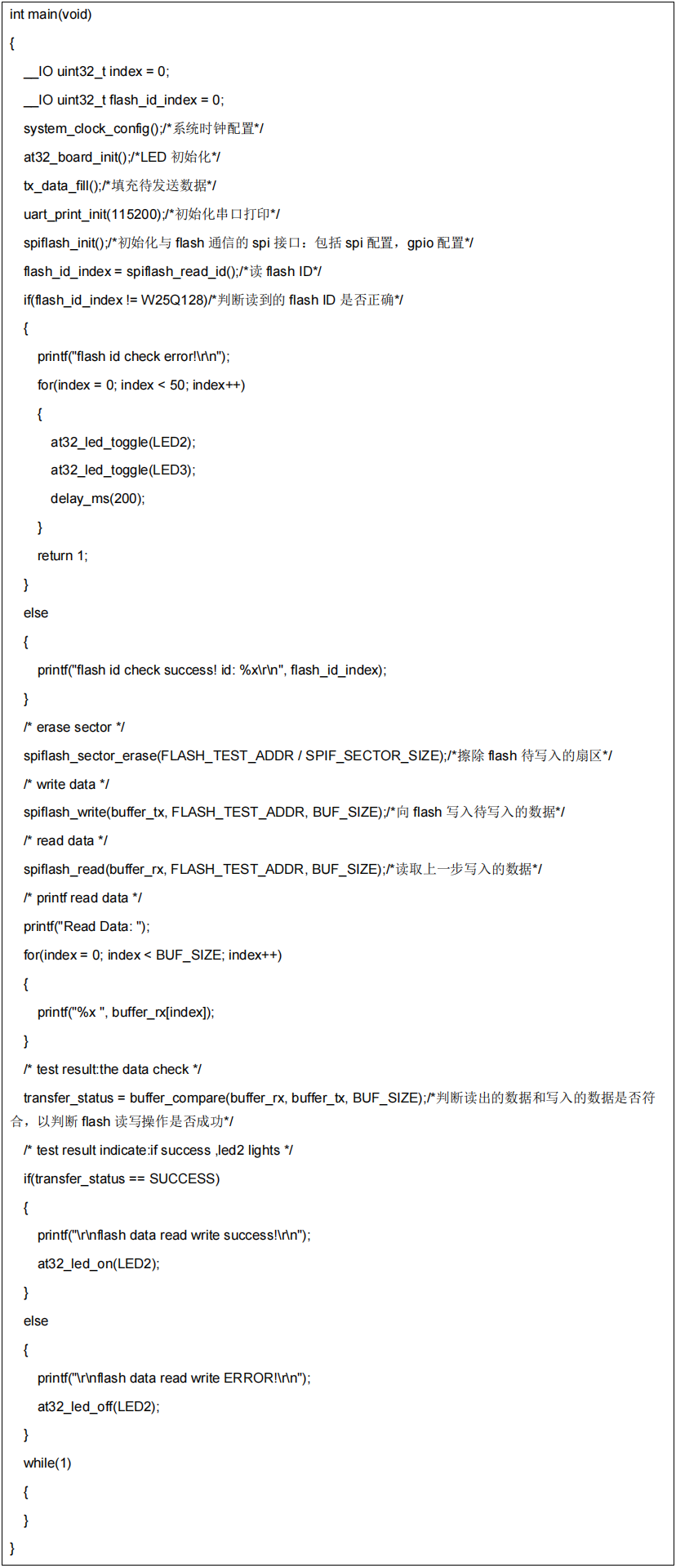

- main函數代碼描述

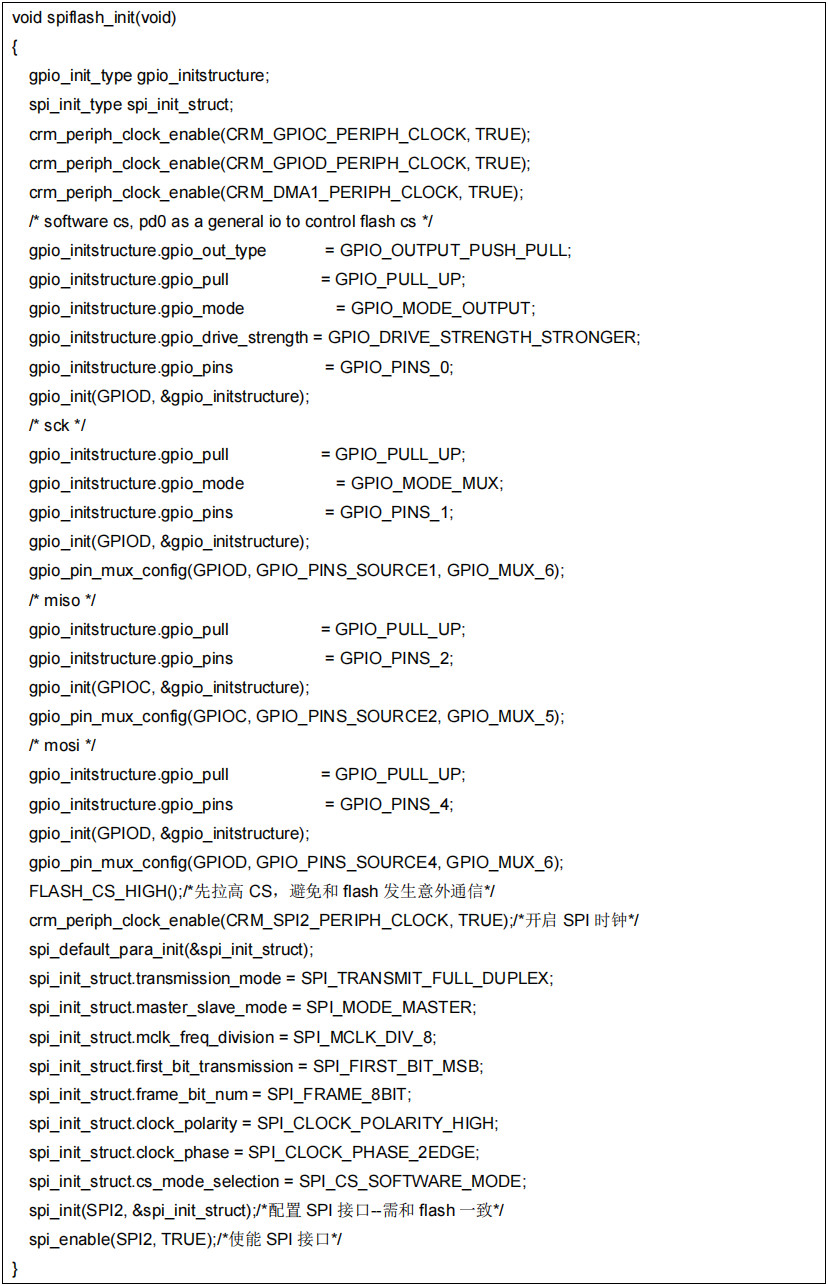

- spi接口配置函數和gpio配置函數代碼描述

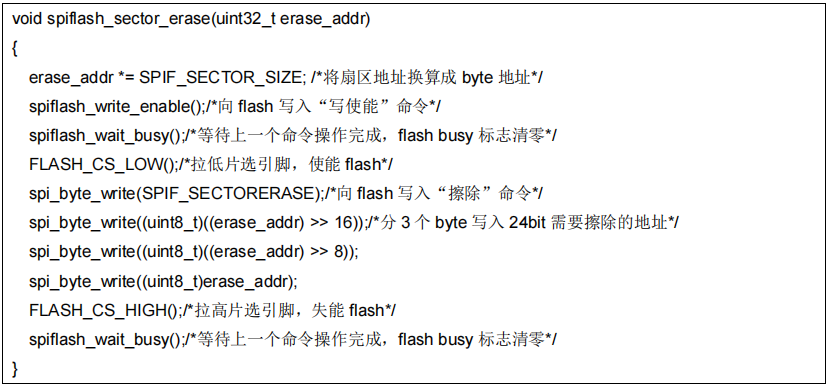

- flash擦除函數代碼描述

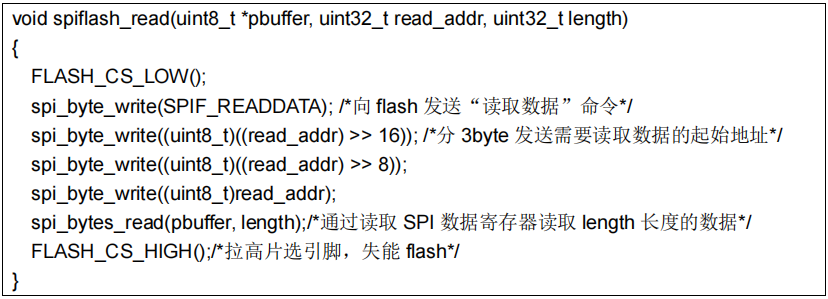

- flash讀數據函數代碼描述

- flash讀ID函數代碼描述

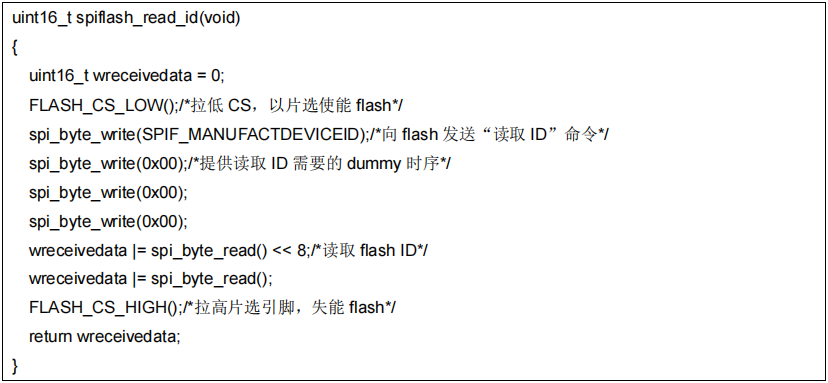

- flash寫函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和FLASH通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和FLASH通信正常。

案例9-SPI使用jtag引腳的配置

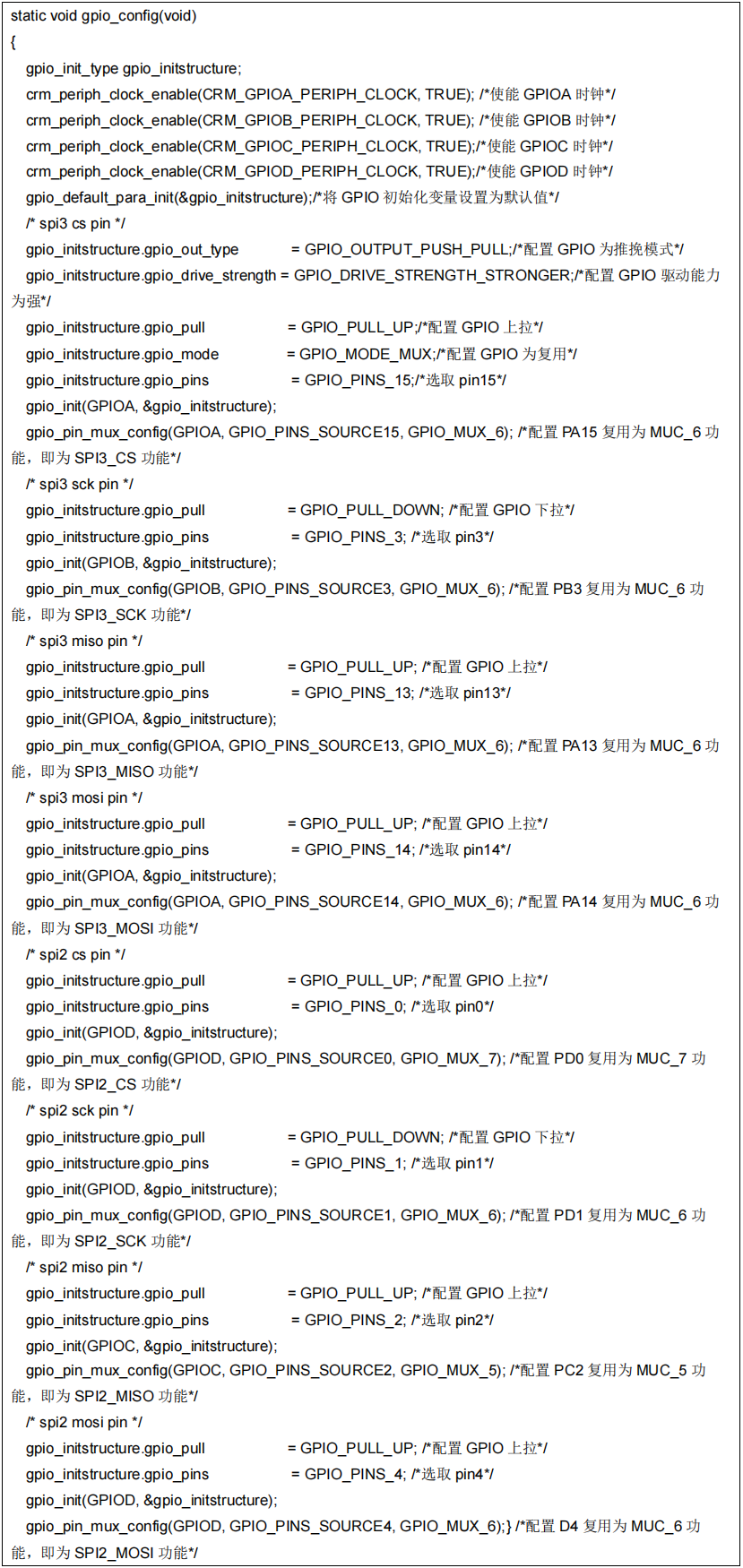

功能簡介實現SPI2和SPI3之間,使用特殊的jtag引腳的全雙工輪詢通信。接線如下:spi2 spi3pd0(cs)<--->pa15(cs)pd1(sck)<--->pb3(sck)pc2(miso)<--->pa13(miso)pd4(mosi)<--->pa14(mosi)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\use_jtagpin_hardwarecs_dma軟件設計注意:本文僅介紹了AT32F435/F437的SPI使用jtag引腳的配置,其他型號的使用配置稍有不同,請參照對應型號的BSP使用。1)配置流程

- 配置SPI2和SPI3對應的GPIO;

- 配置SPI2和SPI3通信配置;

- 開始輪詢通信。

2)代碼介紹

- main函數代碼描述

- SPI通信配置函數代碼描述

- SPI GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明SPI2和SPI3通信正常。

I2S案例

案例1-I2S半雙工DMA方式通信

功能簡介實現I2S2和I2S3之間的半雙工DMA通信。接線如下:I2S2 I2S3pd0(ws)<--->pa4(ws)pd1(ck)<--->pc10(ck)pd4(sd)<--->pc12(sd)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\i2s\halfduplex_dma軟件設計1)配置流程

- 配置I2S2和I2S3對應的GPIO;

- 配置I2S2和I2S3的通信配置和DMA配置;

- 開始DMA通信。

2)代碼介紹

- main函數代碼描述

- I2S配置及DMA配置函數代碼描述

- GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明I2S2和I2S3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明I2S2和I2S3通信正常。

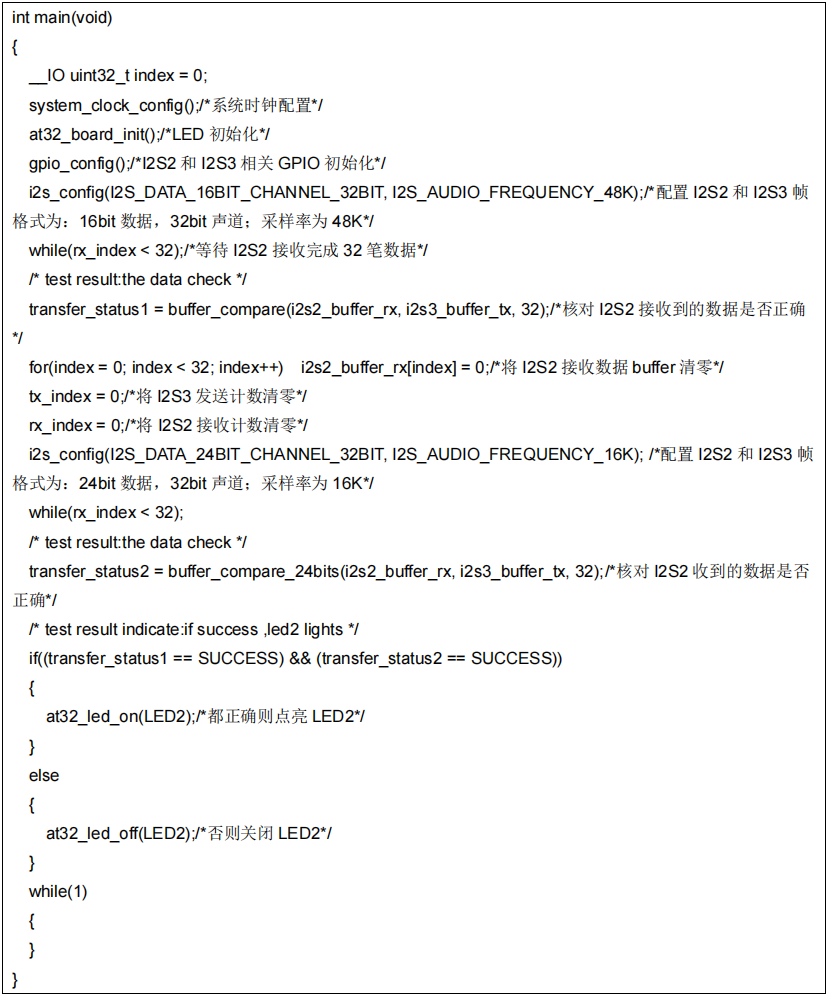

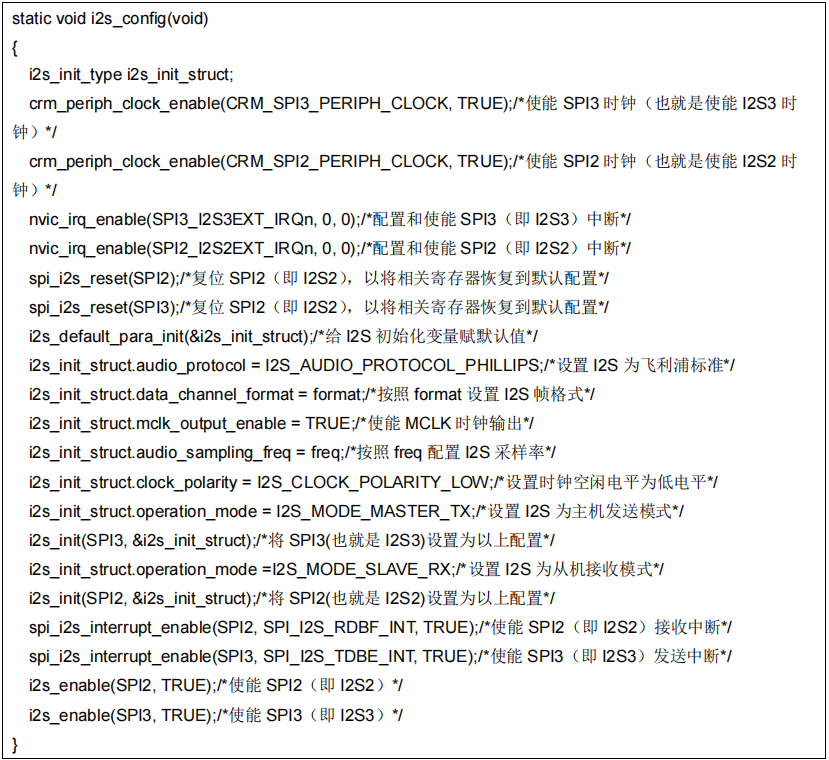

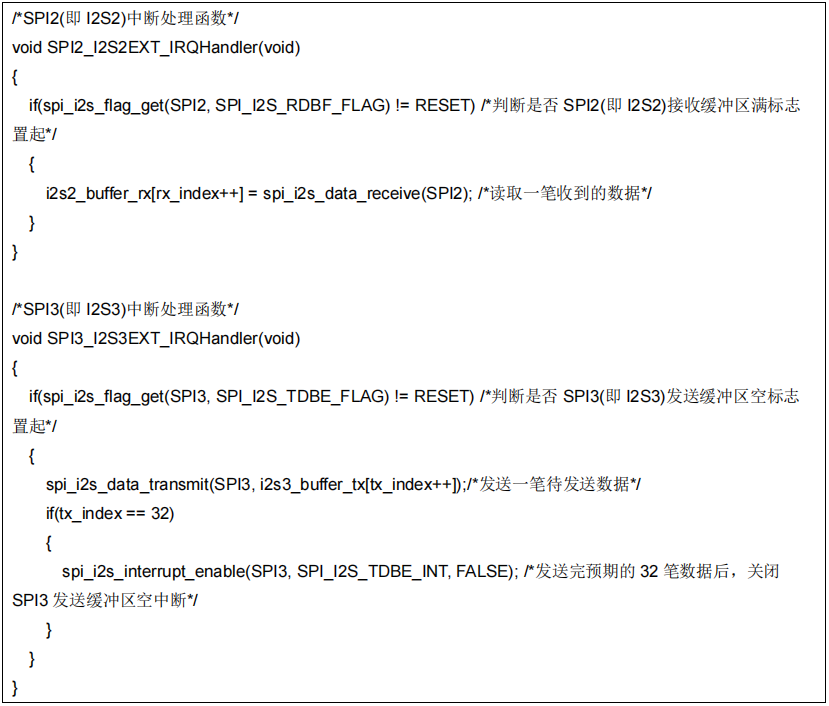

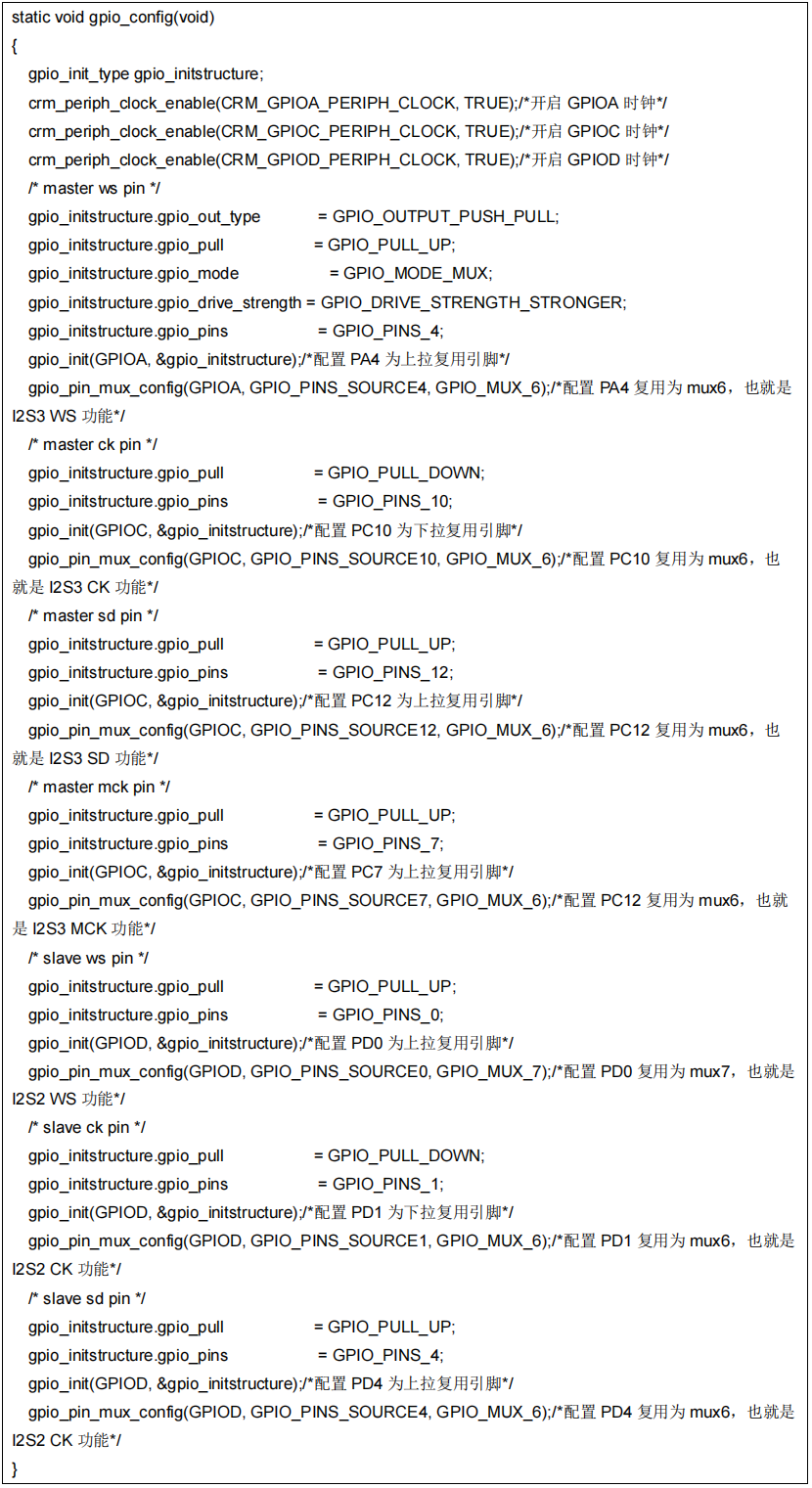

案例2-I2S半雙工中斷方式通信

功能簡介實現I2S2和I2S3之間的半雙工中斷方式通信。接線如下:I2S2 I2S3pd0(ws)<--->pa4(ws)pd1(ck)<--->pc10(ck)pd4(sd)<--->pc12(sd)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\i2s\halfduplex_interrupt軟件設計1)配置流程

- 配置I2S2和I2S3對應的GPIO;

- 配置I2S2和I2S3的通信配置;

- 配置中斷函數;

- 開始中斷通信。

2)代碼介紹

- main函數代碼描述

- I2S配置函數代碼描述

- I2S中斷配置函數代碼描述

- GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明I2S2和I2S3通信正常。

實驗效果AT-START BOARD的LED2亮起,說明I2S2和I2S3通信正常。

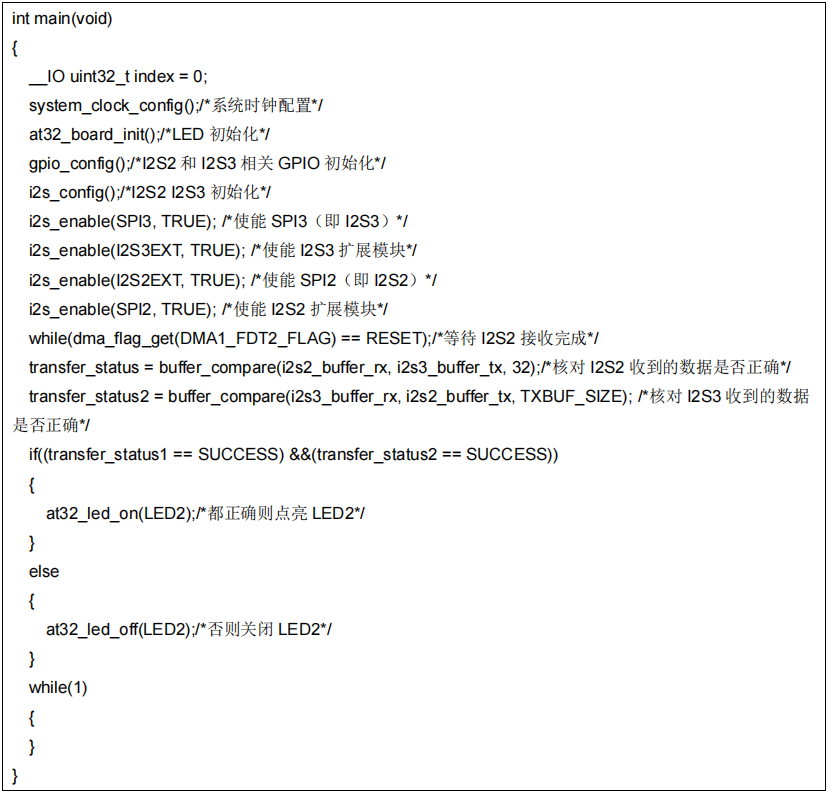

案例3-AT32F403A/F407/F435/F437 I2S全雙工DMA方式通信

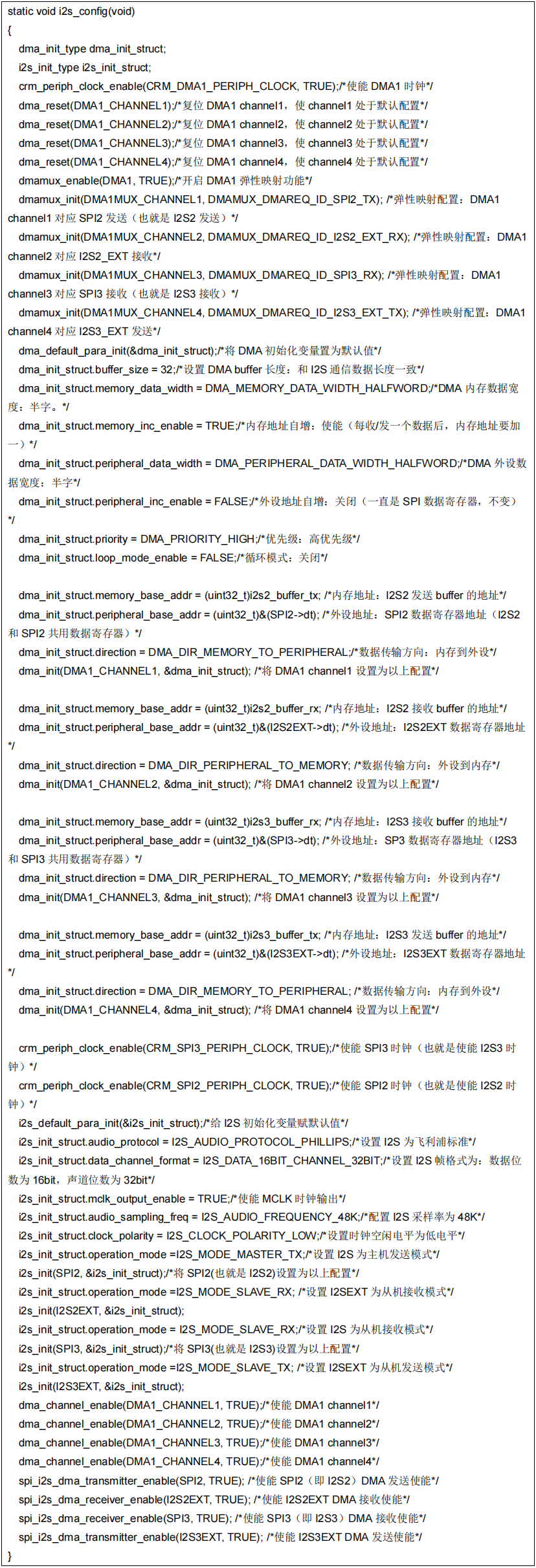

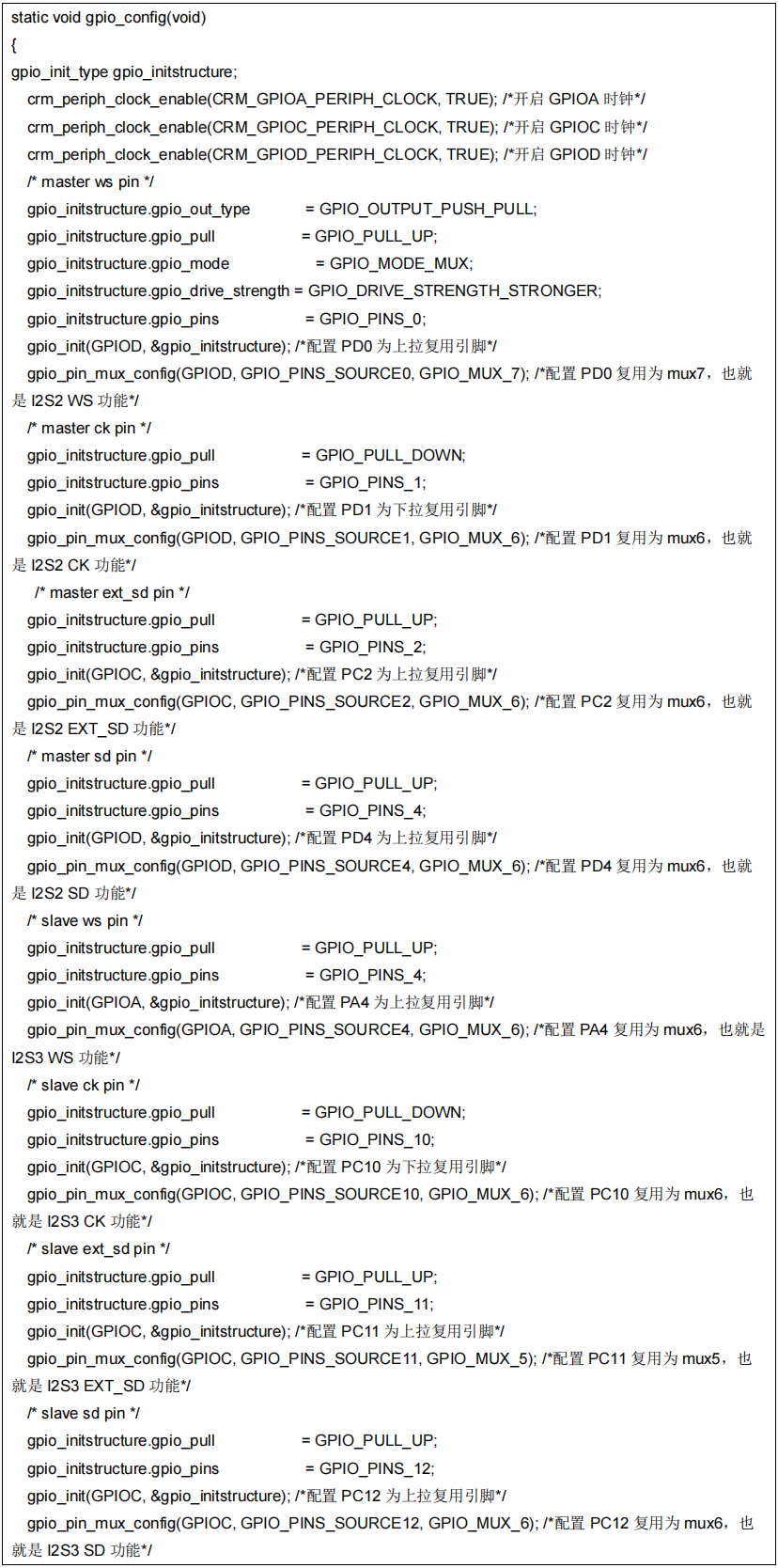

功能簡介實現I2S2和I2S3之間的全雙工DMA通信。接線如下:I2S2 I2S3pd0(ws)<--->pa4(ws)pd1(sck)<--->pc10(sck)pc2(ext_sd)rx<--->pc11(ext_sd)txpd4(sd)tx<--->pc12(sd)rx資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_xxxx\examples\i2s\fullduplex_dma軟件設計1)配置流程

- 配置I2S2和I2S3對應的GPIO;

- 配置I2S2和I2S3的通信配置和DMA配置;

- 開始DMA通信。

2)代碼介紹

- main函數代碼描述

- I2S配置及DMA配置函數代碼描述

- GPIO配置函數代碼描述

實驗效果AT-STARTBOARD的LED2亮起,說明I2S2和I2S3全雙工通信正常。

實驗效果AT-STARTBOARD的LED2亮起,說明I2S2和I2S3全雙工通信正常。

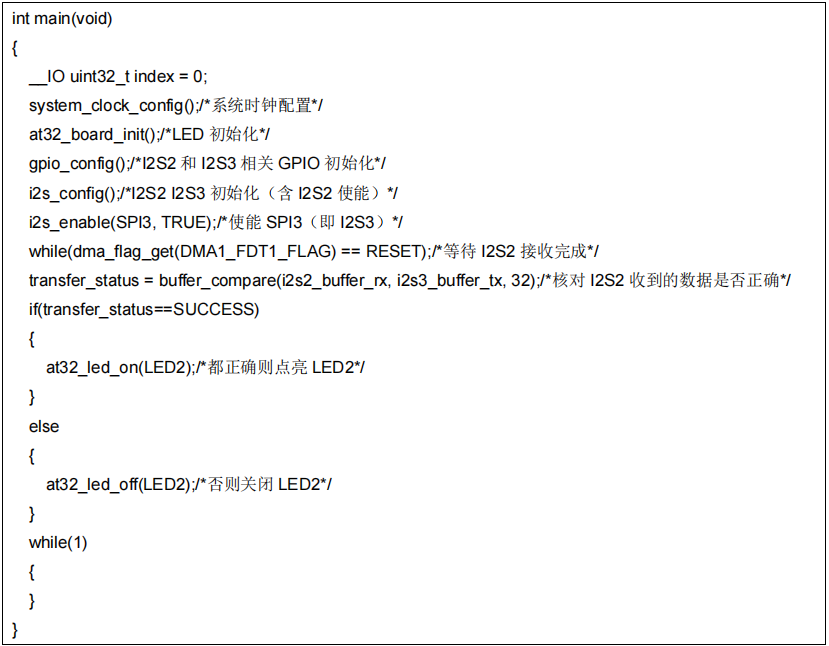

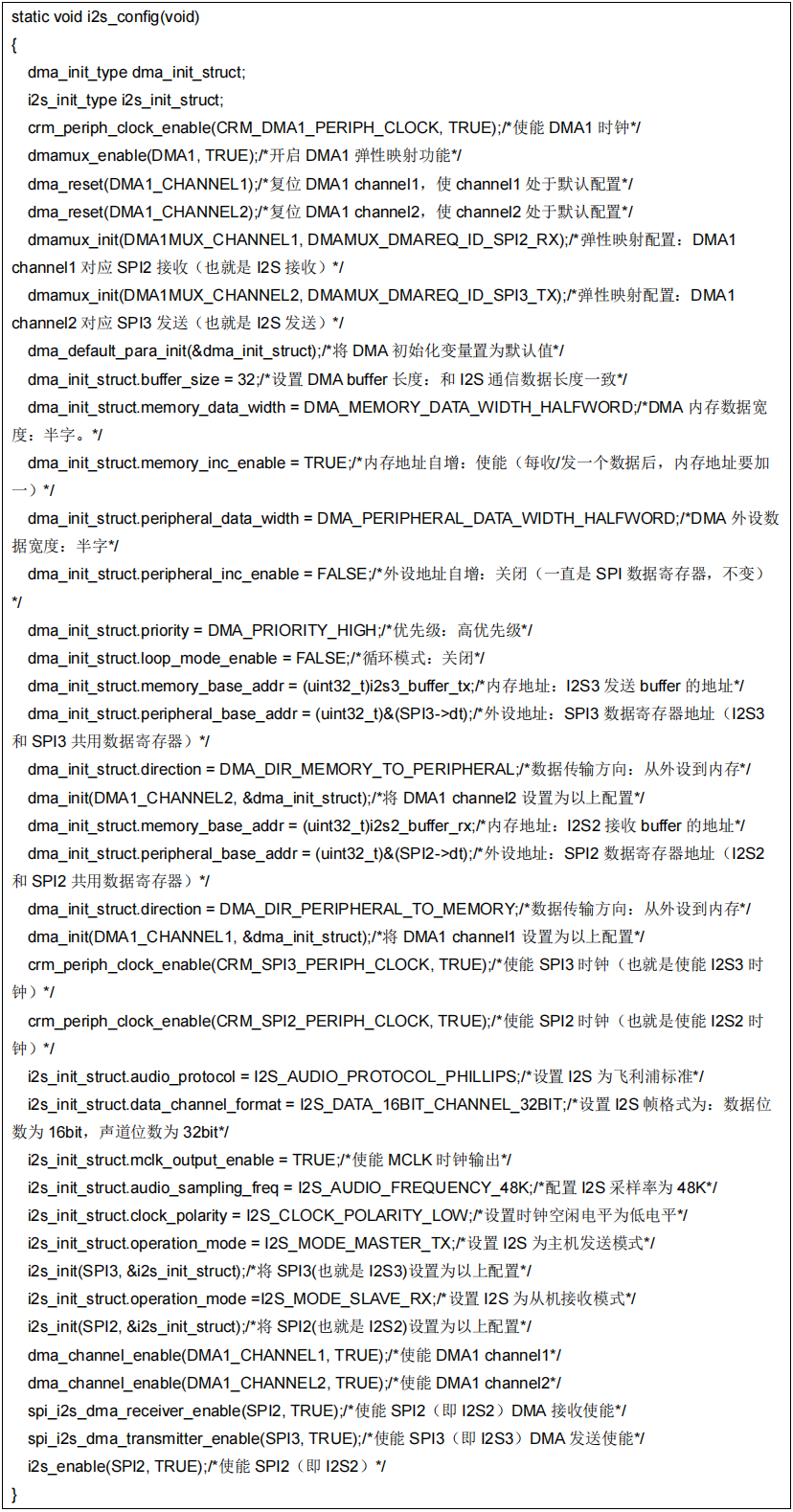

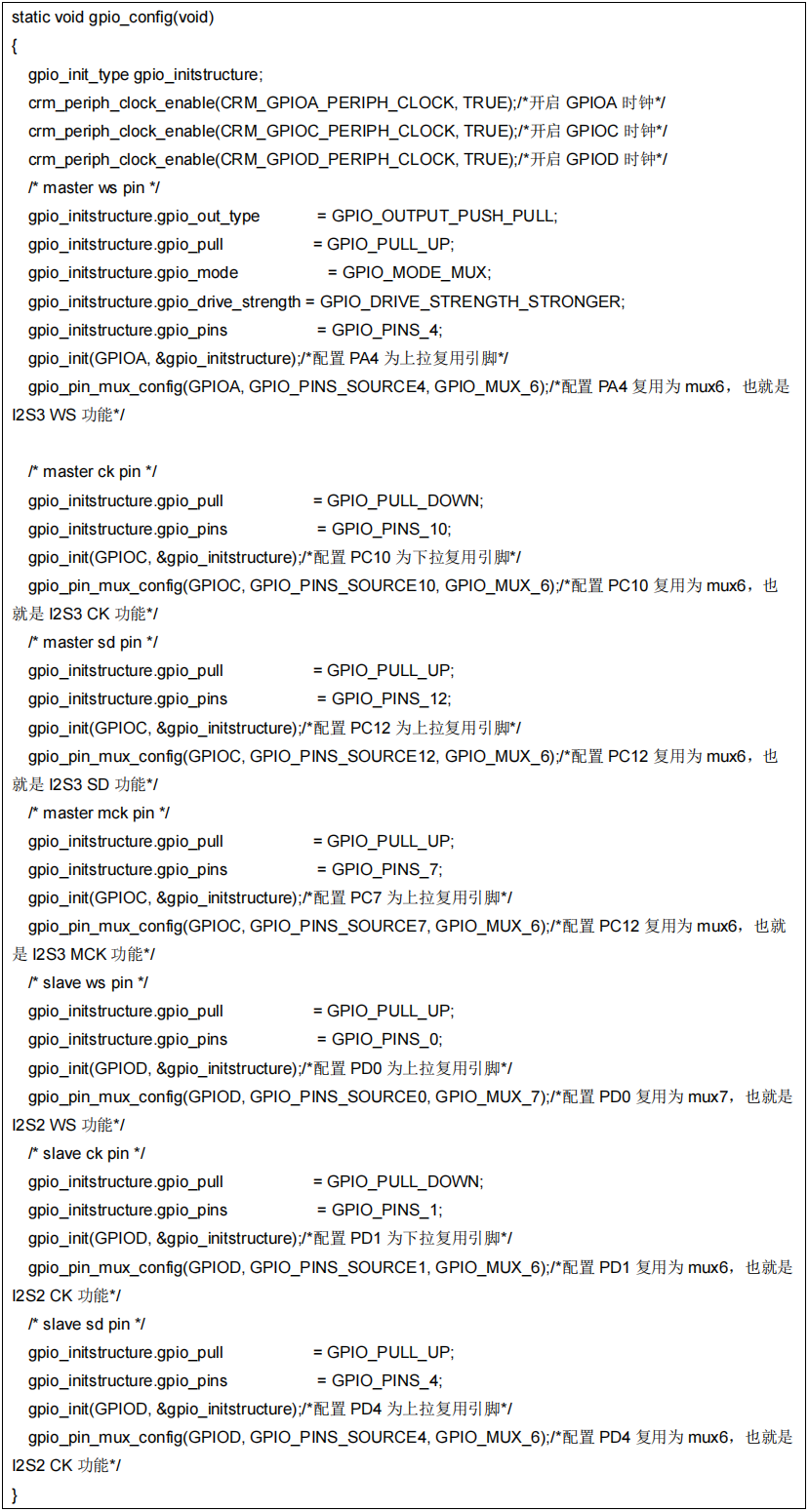

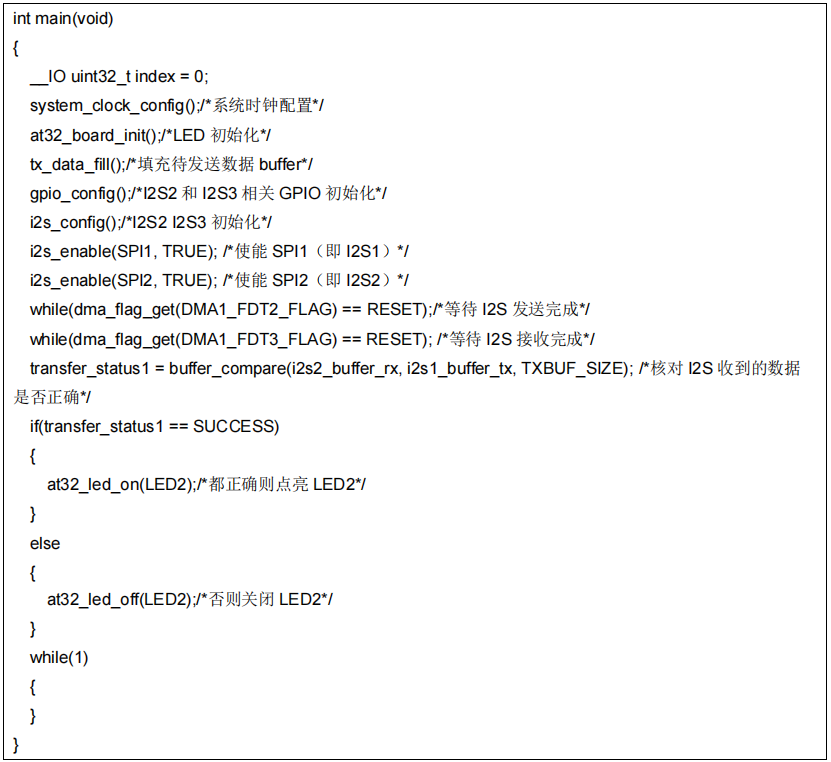

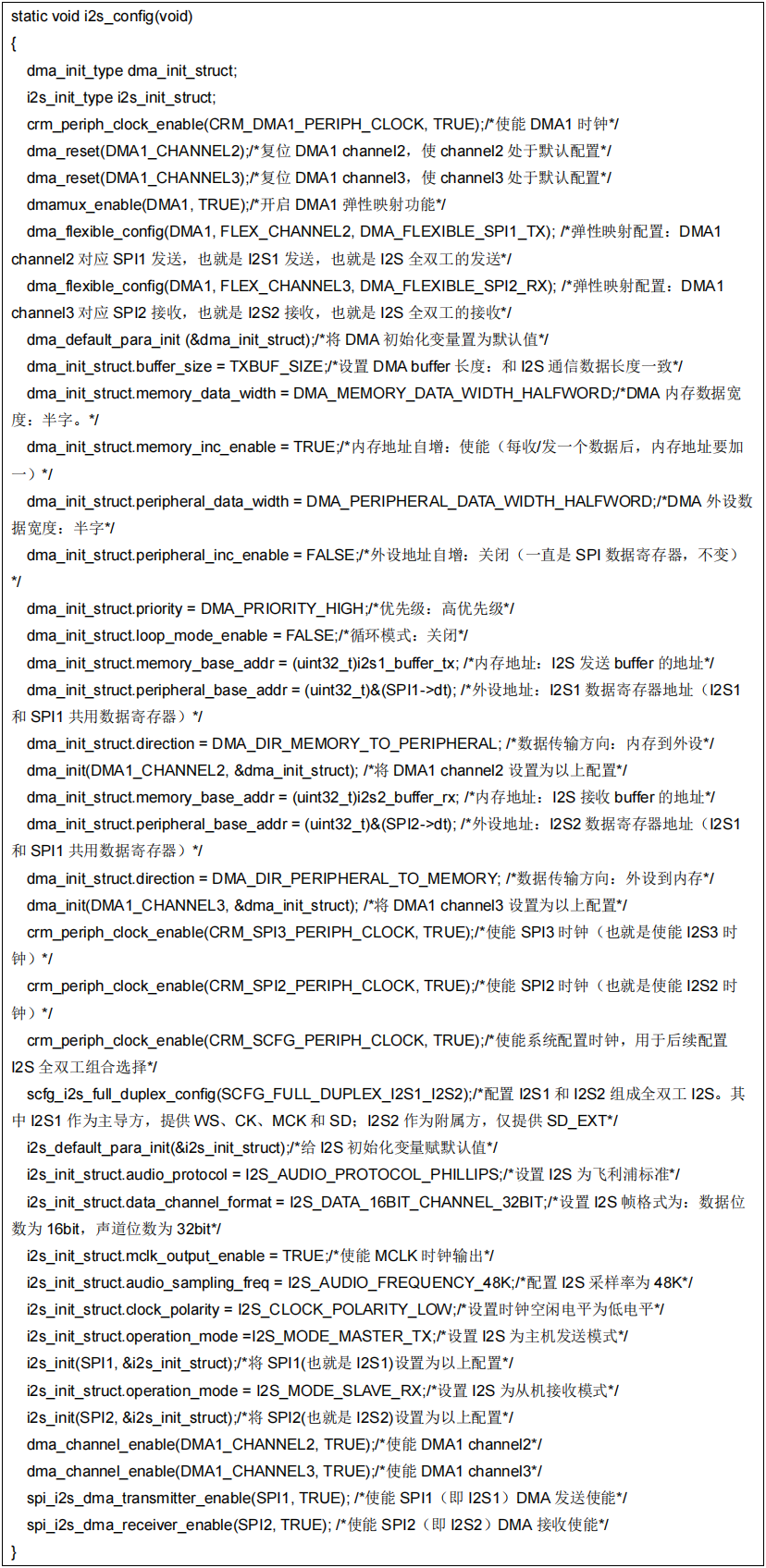

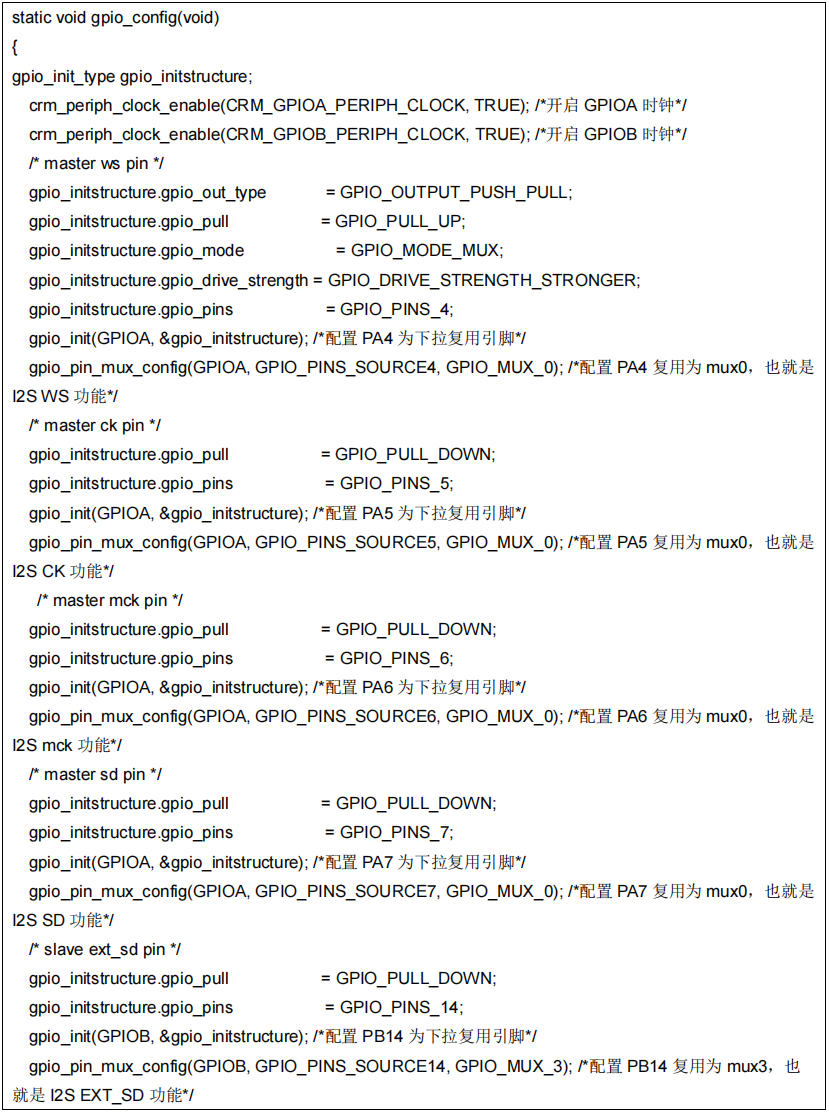

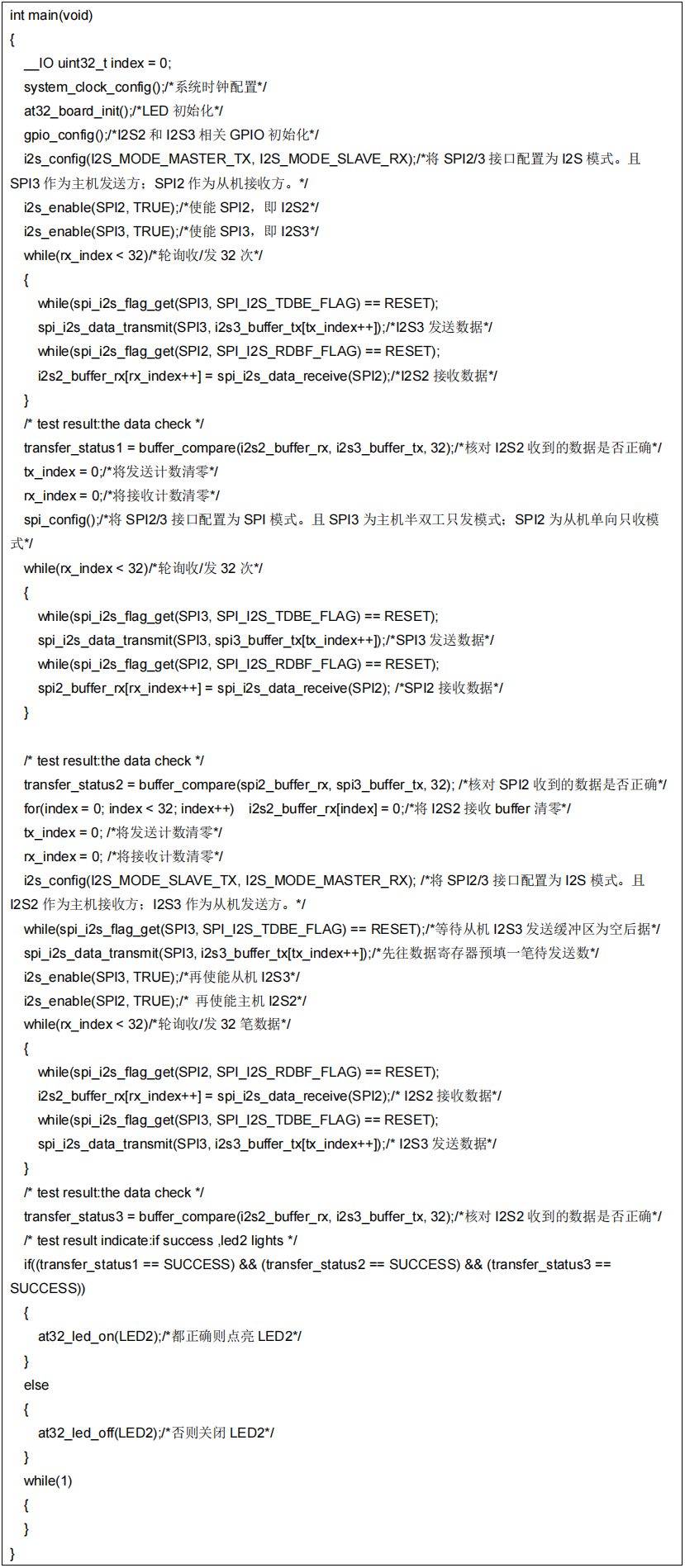

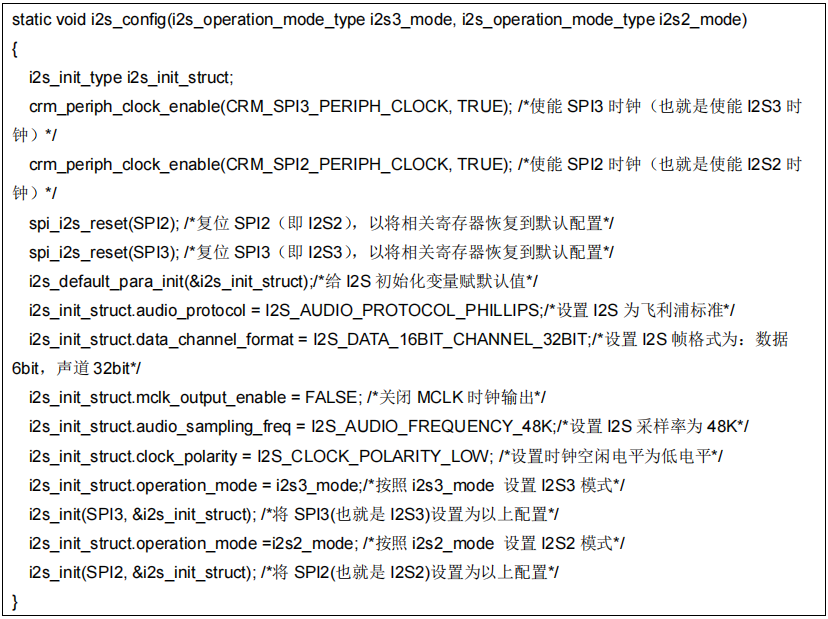

案例4-AT32F425 I2S全雙工DMA方式通信

功能簡介實現I2S1和I2S2組成一個全雙工I2S,組成的全雙工I2S接口定義如下:pa4(ws)pa5(ck)pa6(mck)pa7(sd tx)pb14(ext_sd rx)由于AT32F425只有3個spi(I2S),只能組成一個全雙工I2S,所以不能在同一塊AT-START上用兩個全雙工I2S進行通信。所以本案例使用一個全雙工I2S進行自收自發通信,接線如下:pa4(ws)<--->NCpa5(ck)<--->NCpa6(mck)<--->NCpa7(sd)<--->pb14(ext_sd)用戶也可以準備兩塊AT-START板子對測。使用兩塊板子時,需要注意一塊AT-START配置為主機,一塊AT-START配置為從機。本案例中的代碼僅展示配置為主機,在一塊AT-START上進行自發自收的配置。資源準備1)硬件環境:一塊AT32F425的AT-START BOARD2)軟件環境:project\at_start_f425\examples\i2s\fullduplex_dma軟件設計1)配置流程

- 配置I2S1和I2S2對應的GPIO;

- 配置I2S1和I2S2的通信配置和DMA配置;

- 開始DMA通信。

2)代碼介紹

- main函數代碼描述

- I2S配置及DMA配置函數代碼描述

- GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明I2S全雙工通信正常。

實驗效果AT-START BOARD的LED2亮起,說明I2S全雙工通信正常。

案例5-I2S和SPI功能切換通信

功能簡介實現SPI2和SPI3之間通信切換到I2S2和I2S3之間通信。接線如下:spi2/i2s2 spi3/i2s3pd0(cs/ws)<--->pa15(cs/ws)pd1(sck/ck)<--->pb3(sck/ck)pd4(mosi/sd)<--->pb5(mosi/sd)資源準備1)硬件環境:一塊AT32F437的AT-START BOARD2)軟件環境:project\at_start_f437\examples\i2s\spii2s_switch_halfduplex_polling軟件設計1)配置流程

- 配置SPI2/I2S2和SPI3/I2S3對應的GPIO;

- 配置I2S2和I2S3的通信配置(主發從收);

- 開始I2S2和I2S3的輪詢通信,并核對數據;

- 配置SPI2和SPI3的通信配置(SPI3為主機半雙工只發;SPI2為從機單向只收);

- 開始SPI2和SPI3的輪詢通信,并核對數據;

- 配置I2S2和I2S3的通信配置(主收從發);

- 開始I2S2和I2S3的輪詢通信,并核對數據。

2)代碼介紹

- main函數代碼描述

- I2S配置函數代碼描述

- SPI配置函數代碼描述

- GPIO配置函數代碼描述

實驗效果AT-START BOARD的LED2亮起,說明I2S2和I2S3通信正常,SPI2和SPI3也通信正常。關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發與創新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業界最高主頻288MHz運算效能,并支持工業級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯網、消費、商務及工控等領域。

實驗效果AT-START BOARD的LED2亮起,說明I2S2和I2S3通信正常,SPI2和SPI3也通信正常。關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發與創新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業界最高主頻288MHz運算效能,并支持工業級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯網、消費、商務及工控等領域。

-

mcu

+關注

關注

146文章

16984瀏覽量

350293 -

雅特力

+關注

關注

0文章

156瀏覽量

7974 -

AT32

+關注

關注

1文章

113瀏覽量

2072

發布評論請先 登錄

相關推薦

雅特力發布高性能電機控制專用MCU

AT32講堂088 | 雅特力AT32F402/F405時鐘配置

AT32講堂087 | 雅特力AT32 IDE快速入門指南

雅特力AT32 MCU的隨機數生成

AT32講堂085 | 雅特力AT32 MCU HICK時鐘校準

雅特力電機應用快速入門指南

雅特力攜多款AT32 MCU新品與應用方案亮相2024慕尼黑上海電子展

雅特力AT32 MCU通過IEC 60730功能安全認證,為家電產品提供安全保障

雅特力AT32 MCU與SEGGER攜手合作,開發量產事半功倍

雅特力AT32 MCU與SEGGER攜手合作,開發量產事半功倍

雅特力AT32 MCU HOGP開發指南

AT32講堂048 | 雅特力AT32 MCU SPI/I2S入門指南

AT32講堂048 | 雅特力AT32 MCU SPI/I2S入門指南

評論