一

簡介

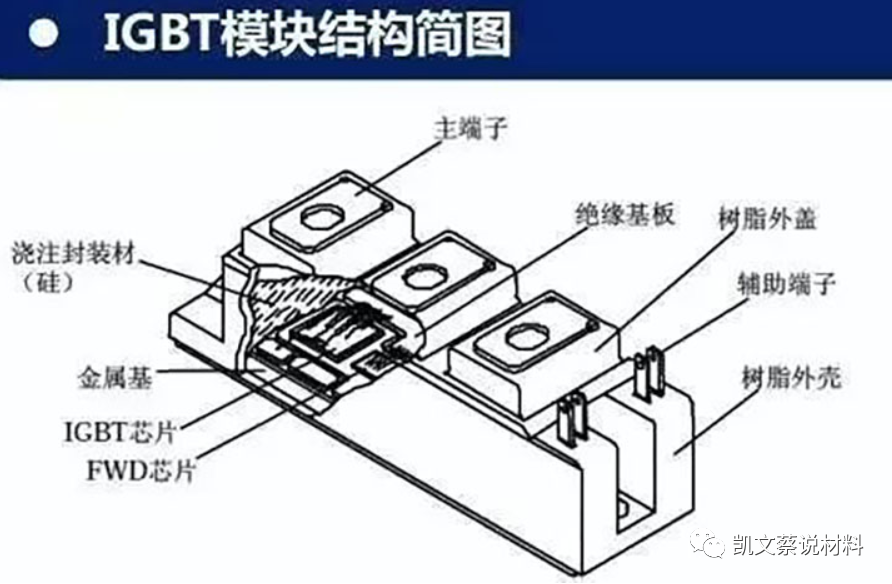

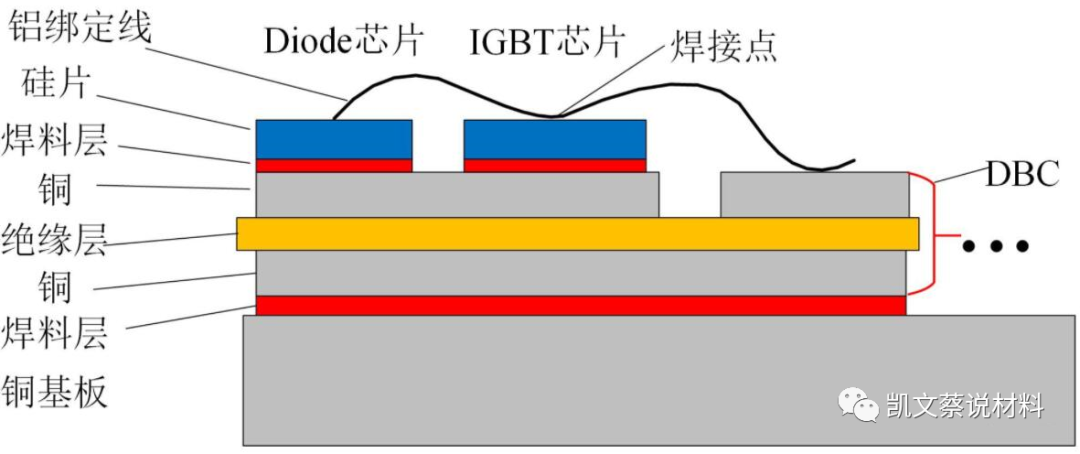

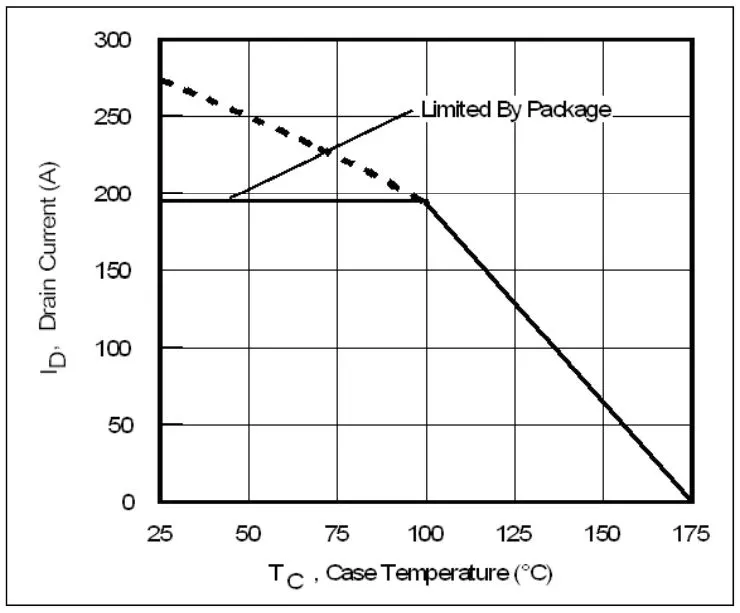

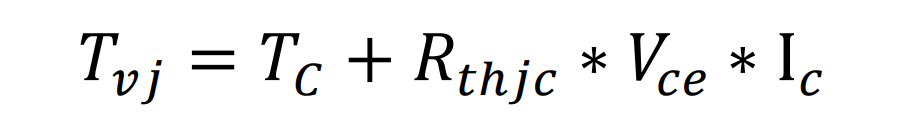

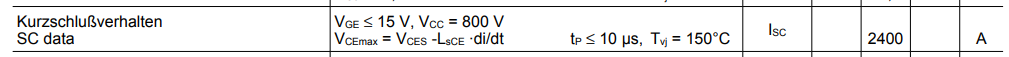

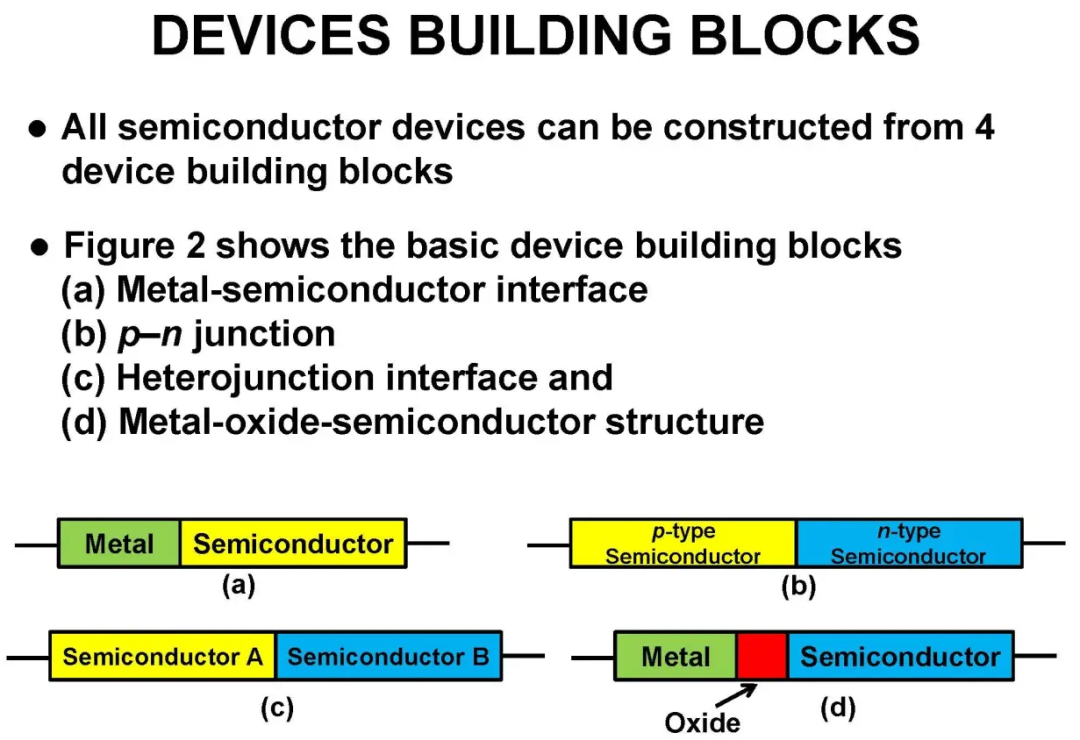

IGBT(Insulated Gate Bipolar Transistor),絕緣柵雙極型晶體管,是由(Bipolar Junction Transistor,BJT)雙極型三極管和絕緣柵型場效應管(Metal Oxide Semiconductor,MOS)組成的復合全控型電壓驅動式功率半導體器件, 兼有(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)金氧半場效晶體管的高輸入阻抗和電力晶體管(Giant Transistor,GTR)的低導通壓降兩方面的優點。GTR飽和壓降低,載流密度大,但驅動電流較大;MOSFET驅動功率很小,開關速度快,但導通壓降大,載流密度小。IGBT綜合了以上兩種器件的優點,驅動功率小而飽和壓降低。非常適合應用于直流電壓為600V及以上的變流系統如交流電機、變頻器、開關電源、照明電路、牽引傳動等領域。IGBT是能源變換與傳輸的核心器件,俗稱電力電子裝置的“CPU”,作為國家戰略性新興產業,在軌道交通、智能電網、航空航天、電動汽車與新能源裝備等領域應用極廣。IGBT模塊是由IGBT(絕緣柵雙極型晶體管芯片)與FWD(續流二極管芯片)通過特定的電路橋接封裝而成的模塊化半導體產品;封裝后的IGBT模塊直接應用于變頻器、UPS不間斷電源等設備上。IGBT模塊具有節能、安裝維修方便、散熱穩定等特點;當前市場上銷售的多為此類模塊化產品,一般所說的IGBT也指IGBT模塊;隨著節能環保等理念的推進,此類產品在市場上將越來越多見。

二

IGBT的結構

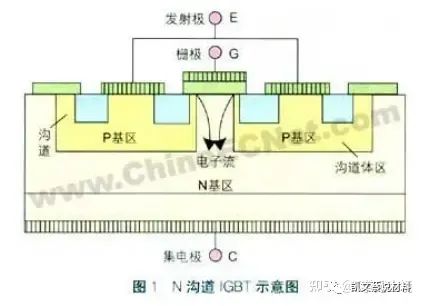

圖1所示為一個N溝道增強型絕緣柵雙極晶體管結構,N+區稱為源區,附于其上的電極稱為源極。N+區稱為漏區。器件的控制區為柵區,附于其上的電極稱為柵極。溝道在緊靠柵區邊界形成。在漏、源之間的 P型區(包括 P+ 和 P一區)(溝道在該區域形成),稱為亞溝道區(Subchannel region )。而在漏區另一側的 P+區稱為漏注入區( Drain injector ),它是 IGBT 特有的功能區,與漏區和亞溝道區一起形成 PNP雙極晶體管,起發射極的作用, 向漏極注入空穴,進行導電調制,以降低器件的通態電壓。附于漏注入區上的電極稱為漏極。

IGBT的開關作用是通過加正向柵極電壓形成溝道,給PNP晶體管提供基極電流,使IGBT導通。反之,加反向門極電壓消除溝道,流過反向基極電流,使 IGBT關斷。IGBT的驅動方法和 MOSFET基本相同,只需控制輸入極N一溝道MOSFET,所以具有高輸入阻抗特性。當MOSFET的溝道形成后,從 P+基極注入到 N一層的空穴(少子),對 N一層進行電導調制,減小N一層的電阻,使 IGBT在高電壓時,也具有低的通態電壓。

IGBT的開關作用是通過加正向柵極電壓形成溝道,給PNP晶體管提供基極電流,使IGBT導通。反之,加反向門極電壓消除溝道,流過反向基極電流,使 IGBT關斷。IGBT的驅動方法和 MOSFET基本相同,只需控制輸入極N一溝道MOSFET,所以具有高輸入阻抗特性。當MOSFET的溝道形成后,從 P+基極注入到 N一層的空穴(少子),對 N一層進行電導調制,減小N一層的電阻,使 IGBT在高電壓時,也具有低的通態電壓。

二

IGBT的發展及現狀

一說起IGBT,半導體制造的人都以為不就是一個分立器件(Power Disceret)嘛,都很瞧不上眼。然而他和28nm/16nm集成電路制造一樣,是國家「02專項」的重點扶持項目,這玩意是現在目前功率電子器件里技術最先進的產品,已經全面取代了傳統的Power MOSFET,其應用非常廣泛,小到家電、大到飛機、艦船、交通、電網等戰略性產業,被稱為電力電子行業里的「CPU」,長期以來,該產品(包括晶片)還是被壟斷在少數IDM手上(FairChild 、Infineon、TOSHIBA),位居「十二五」期間國家16個重大技術突破專項中的第二位(簡稱「02專項」)。

從功能上來說,IGBT就是一個電路開關,用在電壓幾十到幾百伏量級、電流幾十到幾百安量級的強電上的。(相對而言,手機、電腦電路板上跑的電電壓低,以傳輸信號為主,都屬于弱電。)可以認為就是一個晶體管,電壓電流超大而已。家里的電燈開關是用按鈕控制的。IGBT不用機械按鈕,它是由計算機控制的。具體點說,IGBT的簡化模型有3個接口,有兩個(集電極、發射極)接在強電電路上,還有一個接收控制電信號,叫作門極。給門極一個高電平信號,開關(集電極與發射極之間)就通了;再給低電平信號,開關就斷了。給門極的信號是數字信號(即只有高和低兩種狀態),電壓很低,屬于弱電,只要經過一個比較簡單的驅動電路就可以和計算機相連。實際用的“計算機”通常是叫作DSP的微處理器,擅長處理數字信號,比較小巧。這種可以用數字信號控制的強電開關還有很多種。作為其中的一員,IGBT的特點是,在它這個電流電壓等級下,它支持的開關速度是最高的,一秒鐘可以開關幾萬次。GTO以前也用在軌道交通列車上,但是GTO開關速度低,損耗大,現在只有在最大電壓電流超過IGBT承受范圍才使用;IGCT本質上也是GTO,不過結構做了優化,開關速度和最大電壓電流都介于GTO和IGBT之間;大功率MOSFET快是快,但不能支持這么大的電壓電流,否則會燒掉。簡單講,是一個非通即斷的開關,IGBT沒有放大電壓的功能,導通時可以看做導線,斷開時當做開路。IGBT融合了BJT和MOSFET的兩種器件的優點,如驅動功率小和飽和壓降低等。

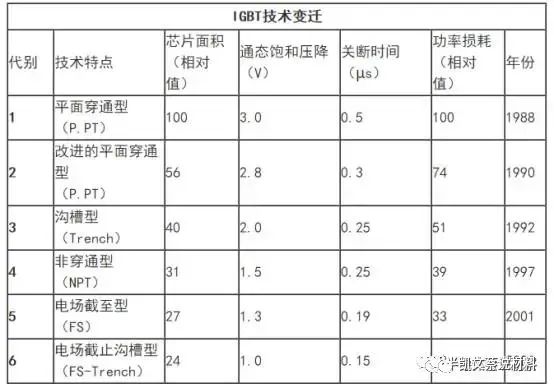

現在IGBT技術發展到什么水平了?IGBT (絕緣柵雙極型晶體管)發明于 80 年代初,多家公司幾乎同時并獨立地發明了這種器件,剛開始各公司對其稱謂也不同。GE 公司剛開始稱其為 IGR(Insulated-Gate Rectifer),其論文于 1982 年 12 月 14 日在 IEDM(國際電子器件會議)上發表。RCA 公司稱其為 COMFET(Conductivity-Modulated FET)并在同一天得到美國專利局的專利批準,接著向 IEDM 提交了正式論文。Motorola 公司也獨立發明了該器件,稱為 GEMFET(Gain-Enhanced MOSFET)。加州伯克利分校發明了類似器件,稱為 BMT(Bipolar MOS Transistor)及 IBT(Insulated-Base Transistor)。GE 公司后來將他們的發明從整流器改稱 IGT(Insulated-Gate Transistor)。德國西門子稱其為 IGBT,由于西門子的 IGBT 發展迅猛,研究生產的 IGBT 性能優良,所以人們認同了 IGBT 的稱謂。至今,IGBT經歷了六代技術的發展演變,面對的是大量的結構設計調整和工藝上的難題。回顧IGBT的發展歷程,其主要從三方面發展演變:器件縱向結構,柵極結構以及硅片的加工工藝。

多年以來,IGBT技術改進的追求的目標是:1, 減小通態壓降。達到增加電流密度、降低通態功率損耗的目的。2, 降低開關時間,特別是關斷時間。達到提高應用時使用頻率、降低開關損耗的目的。3, 組成IGBT的大量“原胞”在工作時是并聯運行,要求每個原胞在工作溫度允許范圍內 溫度變化時保持壓降一致,達到均流目的。否則會造成IGBT器件因個別原胞過流損壞而損壞。4,提高斷態耐壓水平,以滿足應用需要。

具體到每一代的產品發展上。第一代、第二代早期產品曾采用過“輻照”手段,但卻有增加通態壓降(會增加通態功耗)的反作用危險。第一代與第二代由于體內晶體結構本身原因造成“負溫度系數”,造成各IGBT原胞通態壓降不一致,不利于并聯運行,因此當時的IGBT電流做不大。此問題在第四代產品中采用了“透明集電區技術”,產生正溫度系數效果后基本解決了。第二代產品采用“電場中止技術”,增加一個“緩沖層”,這樣可以用較薄的晶片實現相同的耐壓(擊穿電壓)。因為晶片越薄,,飽和壓降越小,導通功耗越低。此技術往往在耐壓較高的IGBT上運用效果明顯。耐壓較低的如幾百伏的IGBT產品,晶片本來就薄,再減薄到如100到150微米的話,加工過程極容易損壞晶片。第三代產品是把前兩代平面絕緣柵設計改為溝槽柵結構,即在晶片表面柵極位置垂直刻槽深入晶片制成絕緣柵。柵極面積加大但占用晶片位置減小,增加了柵極密度。工作時增強了電流導通能力,降低了導通壓降。第四代非穿通型IGBT(NPT)產品不再采用“外延”技術,代之以“硼離子注入”方法生成集電極,這就是所謂的“透明集電區技術”。第五、第六代產品是在IGBT經歷了上述四次技術改進實踐后對各種技術措施的重新組合。第五代IGBT是第四代產品“透明集電區技術”與“電場中止技術”的組合。第六代產品是在第五代基礎上改進了溝槽柵結構,并以新的面貌出現。尤其是承受工作電壓水平從第四代的3300V提高到6500V,這是一個極大的飛躍。上述幾項改進技術已經在各國產品中普遍采用,只是側重面有所不同。除此以外,有報道介紹了一些其它技術措施如:內透明集電極、砷摻雜緩沖層、基板薄膜化、軟穿通技術等。

全球IGBT的市場發展現狀:從市場競爭格局來看,美國功率器件處于世界領先地位,擁有一批具有全球影響力的廠商,例如 TI、Fairchild、NS、Linear、IR、Maxim、ADI、ONSemiconductor、AOS 和 Vishay 等廠商。歐洲擁有 Infineon、ST 和 NXP 三家全球半導體大廠,產品線齊全,無論是功率 IC 還是功率分離器件都具有領先實力。日本功率器件廠商主要有 Toshiba、Renesas、NEC、Ricoh、Sanke、Seiko、Sanyo、Sharp、Fujitsu、Toshiba、Rohm、Matsushita、Fuji Electric 等等。日本廠商在分立功率器件方面做的較好,但在功率芯片方面,雖然廠商數量眾多,但很多廠商的核心業務并非功率芯片,從整體市場份額來看,日本廠商落后于美國廠商。但是全球有近70%的IGBT模塊市場被三菱、東芝及富士等日系企業控制。德系的英飛凌也是全球IGBT龍頭企業之一,其獨立式 IGBT 功率晶體以24.7%的市場占有率位居第一,IGBT 模塊則以20.5%的市場占有率位居第二。

近年來,中國臺灣的功率芯片市場發展較快,擁有立锜、富鼎先進、茂達、安茂、致新和沛亨等一批廠商。臺灣廠商主要偏重于 DC/DC 領域,主要產品包括線性穩壓器、PWMIC(Pulse Width Modulation IC,脈寬調制集成電路)和功率MOSFET,從事前兩種 IC 產品開發的公司居多。總體來看,臺灣功率廠商的發展較快,技術方面和國際領先廠商的差距進一步縮小,產品主要應用于計算機主板、顯卡、數碼產品和 LCD 等設備。

摘要

半導體技術的進步使得芯片的尺寸得以不斷縮小,倒逼著封裝技術的發展和進步,也由此產生了各種各樣的封裝 形式。當前功率器件的設計和發展具有低電感、高散熱和高絕緣能力的屬性特征,器件封裝上呈現出模塊化、多功能化 和體積緊湊化的發展趨勢。為實現封裝器件低電感設計,器件封裝結構更加緊湊,而芯片電壓等級和封裝模塊的功率密度持續提高,給封裝絕緣和器件散熱帶來挑戰。在有限的封 裝空間內,如何把芯片的耗散熱及時高效的釋放到外界環境中以降低芯片結溫及器件內部各封裝材料的工作溫度,已成 為當前功率器件封裝設計階段需要考慮的重要問題之一。本文聚焦于功率器件封裝結構的散熱方面,針對功率半導體器件在散熱路徑方面的結構設計進行歸納總結。通過對國內外 功率器件封裝結構設計的綜述,梳理了功率器件封裝結構設計過程中在散熱方面的考慮及封裝散熱特點,并根據功率器 件散熱特點對功率器件封裝結構類型進行了分類。最后,基于降低封裝結構散熱熱阻、提高器件散熱能力的目的,從高導熱封裝材料和連接工藝、芯片面接觸連接、增加散熱路徑 以及縮短散熱路程四個方面對功率器件封裝結構設計在散熱方面未來的發展趨勢進行了展望。

0 引言

半導體技術的進步極大地促進了電力電子器件的發展和應用。過去幾十年里,在摩爾定律的“魔咒”下,半導體芯片尺寸不斷減小,使得在同樣的空間體積內可以集成更多的芯片,實現更多的功能和更強大的處理能力,為進一步提高功率密度提供了可能。另一方面,芯片尺寸的縮小也增加了芯片散熱熱阻,降低了熱容,使得芯片結溫升高,結溫波動更加明顯,影響功率模塊的可靠性。功率半導體作為電力電子系統的核心組成部分,已經廣泛應用到生活、交通、電力、工業控制、航空航天、艦船等領域。功率器件正呈現出高頻、高壓、高功率以及高溫的發展特點。同時這些特征也對功率器件封裝提出了巨大挑戰,需要考慮到封裝結構、封裝材料和封裝工藝的可行性和適配性,這些涉及到器件的封裝電感、芯片散熱和電氣絕緣等問題,倘若這些不能夠很好的得到解決,就會對器件的熱學、電學、機械性能和可靠性產生極大的影響,甚至導致器件的失效。

尤其是在目前功率器件高電壓、大電流和封裝體積緊湊化的發展背景下,封裝器件的散熱問題已變得尤為突出且更具挑戰性。芯片產生的熱量會影響載流子遷移率而降低器件性能。此外,高溫也會增加封裝不同材料間因熱膨脹系數不匹配造成的熱應力,這將會嚴重降低器件的可靠性及工作壽命。結溫過高將導致器件發生災難性故障及封裝材料因熱疲勞和高溫加速導致材料退化而造成的故障問題。因此,在非常有限的封裝空間內,及時高效的把芯片的耗散熱排放到外界環境中以降低芯片結溫及器件內部各封裝材料的溫度,已成為未來功率器件封裝設計過程中需要考慮的重要課題。加入封裝交流群,加VX:tuoke08。伴隨著電網規模越來越大,電壓等級越來越高,電力系統朝著更加智能化方向發展,高壓、大功率和高開關速度要求功率器件承擔的功能也更加多樣化,工作環境更加惡劣,在此背景下,除芯片自身需具有較高的處理能力外,器件封裝結構已成為限制器件整體性能的關鍵。而傳統的封裝或受到材料性能的限制或因其自身結構設計不能適應高壓大電流高開關速度應用所帶來的高溫和高散熱要求。為保證器件在高壓高功率工況下的安全穩定運行,開發結構緊湊、設計簡單和高效散熱的新型功率器件,成為未來電力系統用功率器件發展的必然要求。本文聚焦于功率器件封裝結構的散熱方面,通過對國內外功率器件封裝結構設計進行綜述,總結了功率器件封裝結構設計過程中在散熱方面的考慮及其結構散熱設計特點,并依據功率器件散熱特點對器件封裝結構進行歸納和分類。最后,基于對功率器件封裝結構熱設計的梳理總結,從提高器件封裝散熱性能的視角,對功率器件封裝材料、連接工藝和封裝結構設計方面的發展趨勢進行了展望。

1 功率器件封裝結構散熱設計原則

針對功率器件的封裝結構,國內外研究機構和企業在結構設計方面進行了大量的理論研究和開發實踐,多種結構封裝設計理念被國內外研究機構提出并研究,一些結構設計方案已成功應用在商用功率器件上。功率器件自身的屬性及其特殊的服役環境決定了封裝器件內部總是受到電場、熱以及應力等多種場效應相互耦合的綜合作用。功率器件的結構設計,應首先要滿足電氣絕緣要求,在此基礎上兼顧結構設計對封裝散熱、芯片及封裝各部件間受力等其他方面的影響。從器件散熱的角度,封裝結構設計應當遵循散熱路徑低熱阻、盡可能多散熱路徑和傳熱路徑上的接觸面積盡可能大的原則。這就要求在設計之初,就應考慮到封裝材料的選擇、散熱路徑的設計、散熱路徑上各部件接觸界面的面積等。但這些不可避免的增加了封裝設計和工藝實現的難度,一種功率器件的封裝實踐往往是考慮多種因素的折中。從目前國內外對于功率器件的研究和開發現狀來看,具備耐高溫、多散熱路徑和大面積連接的封裝特征是未來功率器件封裝的發展趨勢,也是滿足未來高壓、大功率器件工作性能要求的必然選擇。

2封裝結構散熱類型

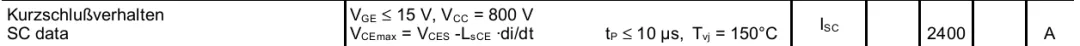

以傳統半導體 Si 芯片和單面散熱封裝為代表的常規封裝器件獲得了良好的發展和應用,技術上發展相對比較成熟。但隨著對更高電壓等級更高功率密度需求的不斷增長,傳統應用于 Si 器件的封裝技術已不能夠滿足現有發展和應用的要,目前傳統 Si 基芯片的最高結溫不超過 175℃,溫度循環的范圍最大不超過 200℃。相比 Si 器件, SiC 器件在導通損耗、開關頻率和具有高溫運行能力方面具有明顯的優勢,最高理論工作結溫更是高達 600℃。若采用現有 Si 基封裝技術,那么以 SiC 為代表的寬禁帶半導體將無法充分發揮其高溫運行的能力。SiC 寬禁帶半導體功率器件更高的開關頻率,可以降低無源器件的重量,占用的封裝體積也更小,因此可以提高功率器件的功率密度,同時 SiC 器件具有更高的熱導率,可以更高效的把芯片耗散熱排出。然而,SiC 器件越來越高的電壓等級和開關速度也給器件封裝帶來巨大的挑戰。目前現有封裝技術的不適配是擺在高壓 SiC 器件應用面前的一道屏障。SiC 芯片尺寸小,厚度更薄,而電壓等級提高,需要特別關注封裝中涉及芯片、基板以及輸出端子等薄弱點的電氣絕緣問題,如 10 kV SiC MOSFET 的芯片厚度僅有 100 μm,平均電場強度達到 100 kV/mm,而對于 1.7 kV 的 Si IGBT,芯片厚度為 210 μm,而平均電場強度只有 8.1 kV/mm。高電壓等級的 SiC 器件電場強度達到 Si 器件的 10倍以上。因此,針對高壓功率器件的封裝需要特殊的設計以滿足高壓絕緣的要求,如需要開發在高電場環境下仍具有高電壓絕緣強度和穩定性的絕緣灌封材料,以隔離水汽、污染物等外界環境。另外,針對灌封過程存在氣泡的問題,現有灌封工藝還需要進一步完善。

SiC 功率器件可以承受更高的工作結溫,降低對外部冷卻器件的要求,縮小封裝器件的體積,使得封裝器件更加輕質高效。然而,缺乏適合的高溫封裝技術體系成為限制 SiC 器件充分發揮其潛力的最大因素,特別是對于高壓大電流應用需求的系統。對于傳統硅基功率器件,單熱管理部分就占到整個器件封裝系統成本的三分之一以上。但隨著 SiC 技術的進步,SiC 器件的高溫運行能力所帶來的優勢足以彌補現階段 SiC 的成本問題。目前商用的 SiC 肖特基二極管受限于傳統塑料封裝形式,其額定工作結溫上限僅能達到 175℃。現有 SiC 器件的封裝仍主要采用焊接封裝,考慮到芯片絕緣和隔離外界環境的目的,封裝模塊內部灌封有完全覆蓋芯片表面的熱導率較低的硅凝膠,硅凝膠上層為空氣,該封裝形式也使得這種從上向下的熱傳導成為芯片產生熱量的幾乎唯一的散熱通道。為了充分利用 SiC 器件高結溫的優勢,發揮 SiC 器件的潛力[,開發新的便于芯片散熱的封裝結構,為芯片封裝提供高效的散熱路徑,達到降低芯片結溫,提升器件整體性能的目的,非常有必要改進現有的傳統功率器件封裝技術,開發新型功率器件封裝結構。由此,通過增加封裝器件的散熱路徑來提高器件散熱能力的方法也就很自然的被提出。基于高壓大功率器件封裝結構散熱方面的考慮,除了在封裝結構設計過程中,采用高熱導率耐高溫封裝材料和高溫焊料,以及時有效的將芯片的熱量傳遞給其他層封裝材料之外,還需要有盡可能多的散熱路徑,如將芯片上表面的鍵合線取消,利用芯片上表面的散熱通路等。近年來,取消鍵合線的功率器件封裝設計研究與實踐也頻頻見于各種文獻資料。這也代表著器件封裝的發展趨勢。同時需要指出的是,取消鍵合線封裝不僅僅對于芯片封裝散熱友好,對于封裝的可靠性也具有優勢。開發體積緊湊、結構設計簡單且具有高效散熱能力的封裝結構成為未來功率半導體器件封裝性能提升的關鍵。 通過對現有功率器件封裝方面文獻的總結,從器件封裝結構散熱路徑的角度可以將功率器件分為單面散熱器件、雙面散熱器件和多面散熱器件。

2.1 封裝結構單面散熱

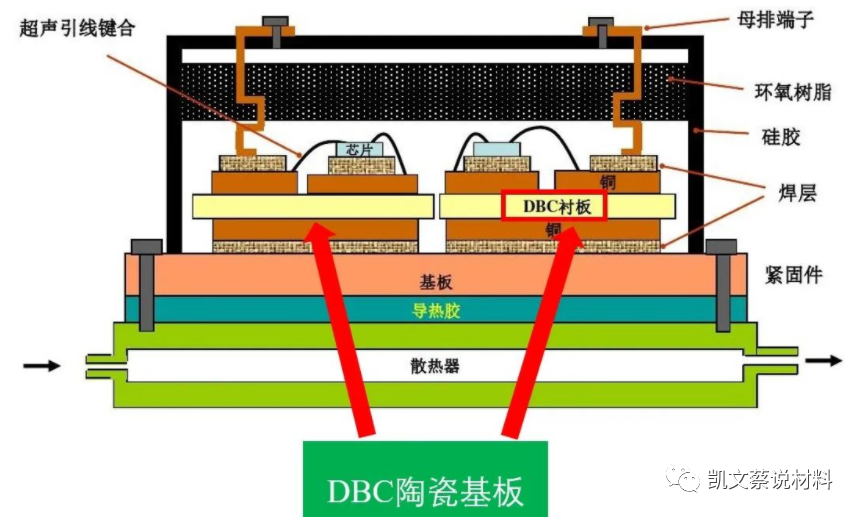

2.1.1 鍵合線類單面散熱

鍵合線連接封裝技術發展較為成熟,在功率器件封裝中具有較長的應用歷史。鍵合線類連接封裝既包含采用鋁線、銅線、鋁帶、銅帶等金屬導線或者金屬帶進行芯片與陶瓷基板以及芯片功率電極與輸出端子連接的封裝,也包括不采用金屬線或者金屬帶連接,而與前者在芯片連接上采用相同原理進行芯片功率電極的連接和引出,實現相同功能的封裝形式。

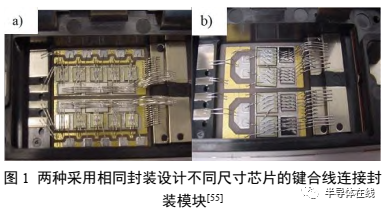

如圖 1(a)和圖 1(b)所示分別為 Cree 與 Powerex 公司基于 Powerex 公司的同等電壓電流等級的硅基 IGBT 模塊合作開發的 1200 V/100 A SiC 鍵合線連接封裝模塊,圖(a)半橋單個開關采用 5 個 25 A 的 SiC MOSFET 芯片和 3 個 50 A 的 SiC JBS 二極管芯片并聯封裝,達到 100 A 的電流等級。圖(b)在單個開關側采用 2 個 80 A SiC MOSFET 芯片和 2 個 50 A SiC JBS 二極管芯片并聯封裝,達到 100 A 的電流等級。兩個版本的模塊采用相同的底板、終端和外殼設計。兩種版本中,SiC MOSFET 芯片電流等級升高,芯片尺寸變大,雖然兩個版本中采用的二極管電流等級相同,但二極管芯片的尺寸不一樣。為了提高模塊散熱性能,兩種模塊均使用氮化鋁陶瓷 DBC 基板,比氧化鋁陶瓷 DBC 基板的導熱系數有明顯提高(AlN 的導熱系數為 210 W/(m·K),Al2O3的導熱系數為 20 W/(m·K))。與(a)版設計相比,(b)版模塊簡化了芯片和鍵合線布局,降低了封裝寄生電阻、電感和導通損耗。SiC 的導熱性能比硅高得多(SiC 的熱導率為 3.7 W/(cm·K),而硅的熱導率為 1.3 W/(cm·K)),其導熱性能取決于 SiC 芯片的面積,由于 SiC 的比導通電阻較低,SiC 的芯片面積通常較小,因此,相比相同封裝設計的硅 IGBT 模塊,熱阻抗降低 37%,散熱性能得到明顯改善。

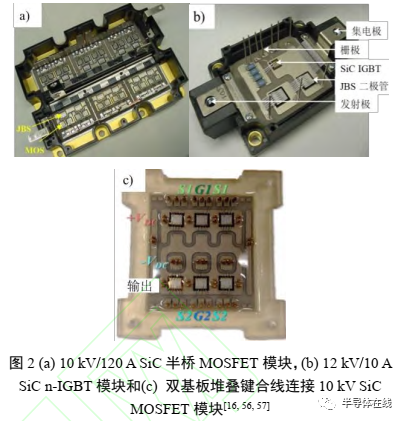

圖 2(a)所示為鍵合線連接的 10 kV/120 A 半橋模塊,該模塊有上下兩個開關,每個開關有 12 個 SiC MOSFET 芯片和 6 個 SiC JBS 二極管芯片,總電流為 120 A[16, 56]。圖 2(b)所示為在 12 kV/10 A SiC IGBT 兩端反并聯兩個串聯的 10 kV/10 A SiC JBS 二極管模塊。從封裝結構上看,圖 2(a)、圖 2(b)與 圖 1 中器件沒有實質不同,均為芯片背面通過焊料焊接在 DBC 基板上,DBC 基板連接到金屬底板, 芯片正面電極采用鍵合線連接,并在芯片正面灌封密封劑對芯片和鍵合線進行保護。圖 2(c)采用了熱循環能力更好的表面鍍銀直接鍵合鋁(DBA)陶瓷基板,陶瓷采用高導熱 AlN。兩個 DBA 基板堆疊有效降低了陶瓷、灌封劑和金屬鋁三結合點處的峰值電場。采用具有低孔隙率、高熱導率且燒結后具有高熔點的大面積燒結銀工藝將兩個 DBA 基板連接在一起。通過納米銀膏將芯片燒結到基板上,芯片正面電極采用鋁鍵合線連接。最后將 NuSil R-2188 灌封到芯片表面,隔離水分和輻射等環境因素,提高芯片表面的電氣絕緣。雙 DBA 堆疊的電氣絕緣和峰值電場得到保障,同時可以對堆疊基板的下底面直接進行冷卻,從而取消底板。盡管基板堆疊會一定程度上增加芯片的散熱熱阻,但基板底部直接冷卻和取消厚度較大的底板所帶來的熱阻改善 彌補了基板堆疊導致的熱阻增加,芯片結溫仍明顯降低。在單個 MOSFET 芯片功率損失為 200 W 且 換熱系數為 5000 W/(m2·K)的條件下,穩態熱仿真結果表明,兩個 1 mm 厚 AlN 陶瓷 DBA 基板堆疊, 芯片結溫峰值降低 34℃,降幅將近 15%,表明雙基板堆疊相對單個基板封裝在熱性能方面的提升。

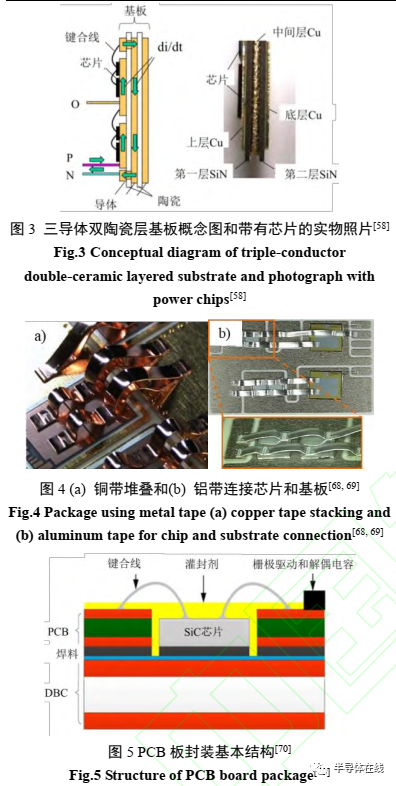

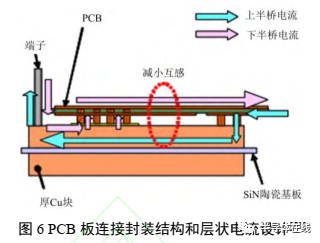

類似于雙基板堆疊,三導體雙陶瓷層基板封裝 (圖 3) 具有三個金屬層和兩個陶瓷層。采用 Sn-Au 高溫焊料將基板連接到帶有翅片的銅底板上,芯片焊盤和基板采用鋁鍵合線連接。將硅凝膠灌入外殼封裝并固化。該基板可以從根本上有效降低回路電感,最大問題是附加陶瓷層(SiN)增加了散熱熱阻。但研究結果表明,該附加陶瓷層也僅使芯片結溫升高了 2℃,影響幾乎可以忽略。采用相同原理和結構封裝的器件還有很多 。圖 4 所示為采用金屬帶進行芯片連接的封裝。金屬帶連接增大了鍵合線的載流能力。圖 5 所示為將芯片嵌入到焊接在 DBC 上的 PCB 板中, 通過鍵合線將芯片電極連接到 PCB 板上。通過優化電流回路、驅動位置和柵極連接可以最小化寄生電感。上述器件在具體封裝結構方面略有差異,但所采用的封裝原理與傳統鍵合線連接封裝相同,這 種封裝形式決定了其單面散熱的封裝熱特性,使得封裝器件內部產生的熱量幾乎只能從芯片一側的基板和底板傳遞,形成了單一的散熱路徑。

2.1.2 無鍵合線單面散熱

取消鍵合線有助于改善器件封裝寄生電感和封裝可靠性。圖 6 所示的超緊湊高可靠性 SiC MOSFET 模塊,取消鍵合線和底板,將芯片直接焊接到基板上,采用銅針取代鋁鍵合線,同時在高導熱 SiN 陶瓷上設計了類似于熱擴散器的更厚銅塊, 具有更好的傳熱效果。相比Al2O3陶瓷基板的鍵合線結構,采用 Al2O3陶瓷的厚銅塊封裝模塊結殼熱阻降低 37%,采用 SiN 陶瓷的厚銅塊封裝模塊結殼熱阻降低 55%。同時該封裝采用新型環氧樹脂和銀燒結技術,具有高達 200℃的高溫運行能力。通過 PCB 板和 DBC 上銅層的層疊電流路徑可抵消掉部分內部電感。從封裝結構上看,雖然取消了鍵合線,但芯片的連接方式沒有改變,芯片通過銅針連接到 PCB 板,采用環氧樹脂進行整體密封,這也使得器件無法通過 PCB 板散熱,只能通過基板側進行散熱。

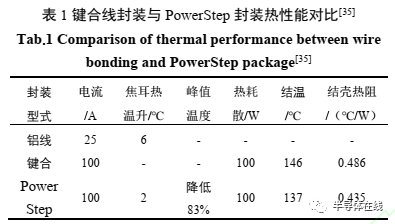

圖 7 所示為被稱作 PowerStep 的無鍵合線互連功率器件封裝,適用于 600~1700 V 的器件封裝。采用大面積薄金屬板與芯片電極連接,金屬板上刻有與芯片焊盤形狀和尺寸相匹配的特征圖案。取消 鍵合線使封裝外形更薄,可有效降低電感。同時, 省略了底板,降低了重量、體積、成本和封裝的復雜性。相比一次只能焊接一個點位的鍵合線連接, 金屬板可通過焊料、燒結膏或其他連接材料一次性 連接到芯片焊盤上。通過改變導通路徑上的幾何形狀,增大接觸面積,有效降低了高壓下導電路徑的寄生電感和電阻。該薄板可采用具有良好導電和導熱性能的金屬銅等制成,大的接觸面積也有利于芯 片熱量的傳導,提高散熱能力。考慮到接觸界面熱膨脹系數的匹配性,可采用 CuMo 或 CuW 合金代替銅。金屬板連接比相同電流下的鍵合線連接具有更低的焦耳熱。表 1 給出了采用 6 根 300 μm 鋁線 鍵合封裝和采用 PowerStep 封裝的模塊熱性能對比,同樣 100 W 的芯片耗散熱,PowerStep 封裝模 塊結殼熱阻降低 10%。采用鋁鍵合線封裝,通入 25 A 電流產生的焦耳熱使鋁線產生了 6℃的溫升;而采用 PowerStep 封裝,通入電流是鋁線鍵合的 4 倍, 而產生的焦耳熱溫升僅是前者的三分之一,充分表明 PowerStep 封裝在降低熱耗散方面更具優勢。

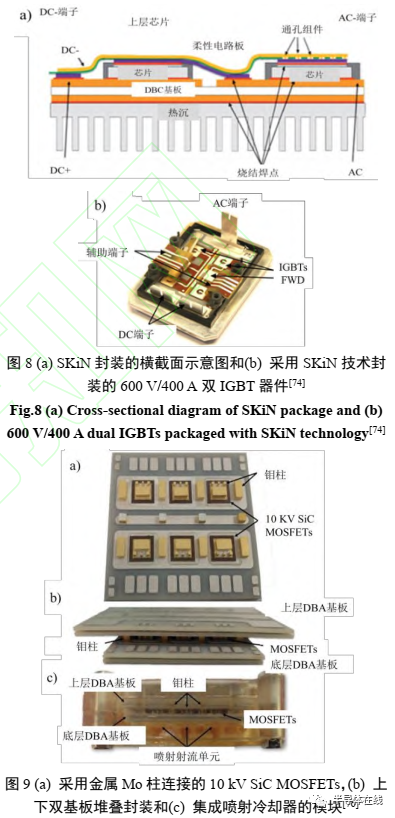

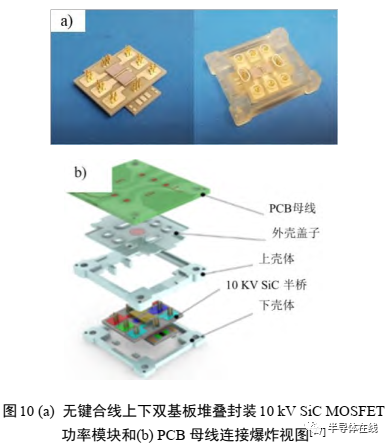

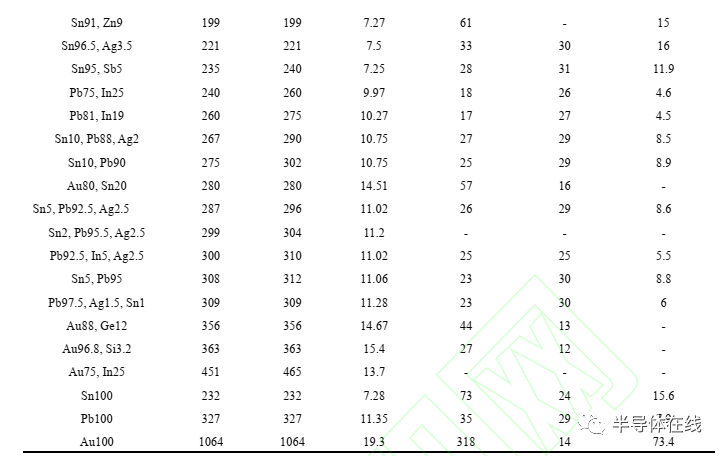

基于面互連原理,圖 8(a)所示的 SKiN 芯片連 接采用擴散銀顆粒燒結取代傳統鍵合線封裝中的焊料連接,芯片燒結到 DBC 基板上,采用兩層柔性板上的可燒結銅箔連接芯片上表面和基板,柔性板的下金屬層成為功率側,承載高功率負載電流, 根據材料(鋁或者銅)以及所需的電流,該金屬層的 厚度在 100 μm 范圍內最合適。柔性板的上下金屬層彼此絕緣,上金屬層為邏輯側,只需相對較薄的厚度(30 μm),主要承載柵極、輔助和感應信號。柔性板上開有通孔,可以將芯片的柵極信號引出到 柔性板的邏輯側。不同于鍵合線的點互連,該柔性銅箔與芯片電極之間可以達到 85%的接觸,而傳統鍵合線與芯片間的接觸僅有 21%,增大接觸面積和金屬層厚度可以改善傳熱,并且可大大提高器件的 功率循環能力。基于雙基板堆疊和面互連,采用上下雙基板堆疊的無鍵合線平面互連封裝如圖 9 和圖 10 所示。該封裝采用 Wolfspeed 第三代 10 kV SiC MOSFET 芯片構建。芯片焊接在下堆疊基板上,芯片正面電極采用金屬 Mo 柱連接,Mo 柱上方連接帶有通孔的上堆疊基板。在上堆疊基板的上表面, 采用高密度彈簧銷端子,將芯片電極連接到 PCB 母線。Mo 柱互連取代鍵合線連接,提高了機械可靠性,降低了封裝雜散電感和電阻。該封裝在芯片的兩側均采用平面連接,少部分熱量可通過芯片上表面傳遞給上部堆疊基板,但由于上基板上表面為彈簧端子連接,不利于熱量傳遞,芯片耗散熱主要 從下堆疊基板散熱,使該封裝僅具有單一散熱通路。通過在下堆疊基板底部集成定制的直接射流噴 射冷卻器,模塊結到環境熱阻達到 0.38 ℃/W。

從單面散熱器件封裝結構來看,鍵合線連接類器件封裝各層從上至下主要由頂蓋、外殼、空氣層、 灌封劑、鍵合線(金屬帶)、芯片、芯片焊料、DBC(DBA)基板、基板焊料和底板組成。鍵合線連接技術較為成熟、成本低且操作上具有靈活性,被 廣泛用于芯片電極與功率端子的連接。但鍵合線連接需要在基板上預留出額外的鍵合面積用于電流傳輸,因此降低了功率密度。基板與鍵合線形成的電流回路也會產生較大的寄生電感、電阻以及更 高的開關噪音和功率損耗,加劇芯片溫升。此外, 鍵合線與半導體器件間存在材料熱膨脹系數的不匹配,使得線鍵合處往往成為易失效位點,甚至出現裂紋或者松動,導致接觸不良,使鍵合點處的接觸熱阻增大,溫度升高,加速該點的失效。無鍵合線單面散熱器件芯片與基板的連接與鍵合線連接器件相同。無鍵合線面互連封裝降低了封裝寄生電感和電阻,大的接觸面積增強了傳熱。上述封裝結構只能通過由芯片底部的陶瓷基板和底板構成的唯一路徑進行散熱。目前鍵合線連接的硅基器件單面散熱封裝結構已接近其散熱極限,硅芯片的工作結溫也接近其承受上限,嚴重影響了器件的性能,更限制了具有更高溫度運行能力的 SiC 器 件的性能。從散熱的角度看,功率器件產生的熱量只能通過底面傳遞,限制了其散熱性能。在目前封裝材料性能和封裝工藝暫時無法取得較大改善的情況下,通過創新結構布局和設計,優化散熱路徑, 是解決功率器件封裝散熱的有效方案。

2.2 封裝結構雙面散熱

隨著器件功率密度的不斷提高,器件封裝的熱管理變得愈加關鍵。基于上述總結與分析,優化器件封裝散熱路徑是解決高壓大電流高功率密度條件下功率器件散熱、降低芯片結溫的有效方案。鍵合線連接器件無法將芯片上表面作為散熱通路,采 用無鍵合線封裝,充分利用芯片上表面進行散熱, 熱量從芯片上下表面兩個路徑傳遞,可增強器件的散熱能力,降低芯片結溫,提高器件的熱性能。

2.2.1 單基板雙面散熱

(1)上 LTCC 基板 press-pack 封裝雙面散熱

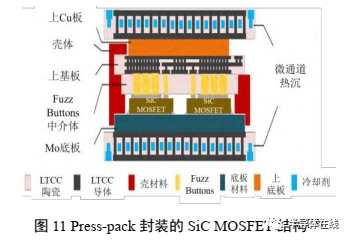

為利用芯片上表面散熱,研究人員提出了圖 11 所示的 press-pack 封裝方法,該方法利用壓力接觸取代鍵合線和焊料,可降低雜散電感且具有更高的可靠性。該封裝使器件具有雙面散熱的能力。現有 press-pack 封裝包括直接壓力接觸和彈性接觸兩種方式,但都需要大的芯片面積且需要對芯片上層金屬化進行特殊設計。SiC 芯片面積比硅芯片小, 芯片表面常采用鋁進行金屬化。為實現壓力接觸, 采用被稱作“Fuzz buttons”的柔性微型壓針插入到薄的插接體中,以產生均勻的壓力分布,并使引入的寄生電感最小。該 press-pack 夾在兩個液冷微通道散熱器之間,SiC 芯片連接在金屬鉬底板上。帶有“Fuzz buttons”微型柔性壓針的壓力接觸插 接體將 SiC 芯片的源極和柵極連接到上部基板。該多層結構的上基板將芯片的源極和上部銅板連接, 并為柵極驅動器提供柵極和開爾文源極端子。微通道散熱器采用低溫共燒陶瓷(LTCC)制成,由于 press-pack 封裝沒有內部絕緣,熱沉的引入增大了 回路的寄生電感,上下兩側的微通道散熱器設計可提供足夠的散熱能力,同時外形上厚度較薄可降低功率回路的電感。微通道散熱器的電氣回路和冷卻回路分離,可以使用非介電流體進行冷卻。雖然 LTCC 的導熱性不如金屬和 AlN 陶瓷好,但仿真結果表明,在總熱耗散為 60 W,采用 LTCC 微通道熱 沉水冷散熱時,SiC 芯片最大結溫僅為 85℃,并聯芯片間的最大結溫差小于 0.9℃,并聯芯片的結溫分布比較均勻。結到熱沉熱阻為 0.2 ℃/W,熱沉最高溫度為 73℃,熱沉到冷卻劑的熱阻為 0.8 ℃/W。

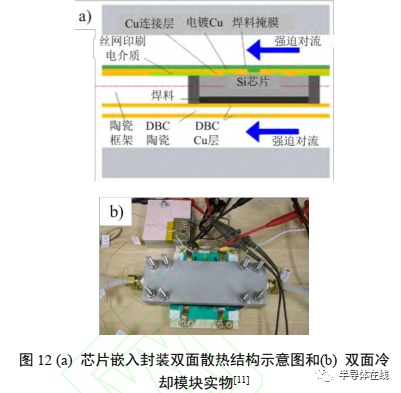

(2)下 DBC 芯片嵌入雙面散熱

為追求更加優異的散熱性能,研究人員提出了嵌入式功率芯片封裝的雙面液體冷卻方案。該嵌入式封裝由扁平陶瓷框架、嵌入式芯片、介電夾層和沉積金屬化層互連組成。將芯片嵌入到具有開 槽的陶瓷框架中,并在固化爐中用粘性聚合物將芯 片四周進行粘接并固化,形成的平坦表面為平面加工提供了平臺。使用聚合物絲網印刷方法在其上涂 上介電夾層。通過通孔與芯片的鋁金屬焊盤相對應,然后在其上沉積金屬層,進行圖案化,引出芯片正面的功率電極。芯片背面可通過焊層與 DBC 基板連接。芯片封裝上下兩個外表面均為平面,可在兩側分別連接熱沉進行冷卻(圖 12)。研究表明, 器件功率損失在 5~300 W 范圍內時,與鍵合線連接的單面液冷相比,嵌入式封裝雙面液冷熱阻可降低 45%~60%。且隨著冷卻流體流速的增加,散熱效果 更加明顯。因此,使用嵌入式功率芯片封裝的雙面液體對流散熱是改善功率半導體器件散熱的可行且有效方案。

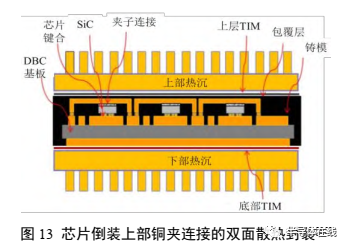

(3)下 DBC 芯片倒裝銅夾連接雙面散熱

與常規芯片封裝相反,將芯片正面連接在 DBC 上,芯片背面通過銅夾引出,即可實現芯片的倒裝封裝,實現芯片兩個表面散熱(圖 13) 。采用燒結銀工藝將芯片倒裝燒結到 DBC 基板上,芯片背面采用銅夾連接,銅夾上連接散熱器,形成芯片上表 面的熱通路。采用聚合物熱界面材料在模塊的上下表面連接兩個陶瓷散熱器,進行雙面散熱。由于芯片倒裝鍵合面積僅占芯片面積的很小一部分,接觸面積較小成為限制該封裝散熱性能的關鍵。該封裝 中倒裝芯片鍵合層和銅夾連接層對模塊熱性能的 影響比連接散熱器的熱界面材料的影響更加顯著。增大倒裝芯片的鍵合面積有助于降低倒裝芯片鍵合層的熱阻,有利于降低芯片結溫。研究表明,通過增大芯片電極金屬化面積,如將芯片電極面積占 比從 22%提高到 88%,采用倒裝鍵合,芯片結溫可 降低 20-30℃。建議可以通過采用擴大芯片電極金屬化面積,增大鍵合面積的方式來降低熱阻。

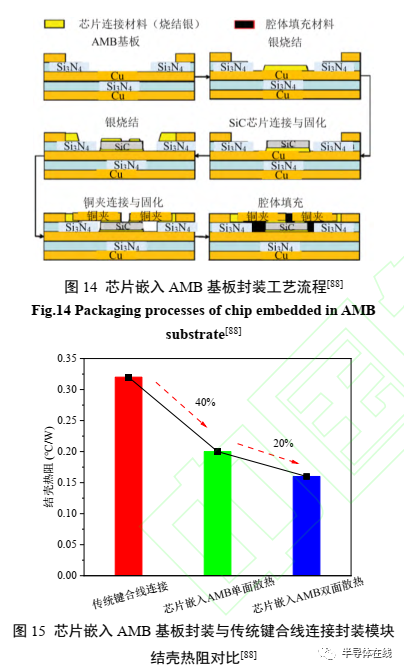

與上述將芯片連接到 DBC 基板封裝不同,在 active metal brazing(AMB)基板中有特殊設計的空腔,將芯片嵌入到 AMB 空腔里(圖 14),采用定制的銅夾連接芯片和 AMB 基板,使其與基板上金屬層在同一水平面,即在封裝上側形成平面,可以在 該表面和 AMB 基板的下表面分別連接散熱器,實現雙面散熱。圖 15 給出了嵌入到 AMB 基板封裝的單面散熱、雙面散熱與傳統鍵合線連接封裝單面散熱的熱性能對比。結果顯示,芯片嵌入 AMB 基板單面散熱封裝模塊相比傳統鍵合線連接單面 散熱模塊,結殼熱阻降幅可達 40%。若在芯片嵌入 AMB 基板采用雙面散熱封裝,模塊的結殼熱阻可進一步降低 20%。綜上所述,表明芯片嵌入到 AMB 基板封裝相對傳統鍵合線封裝在降低封裝熱阻方面的優勢,同時也展現出雙面散熱的熱性能優勢。

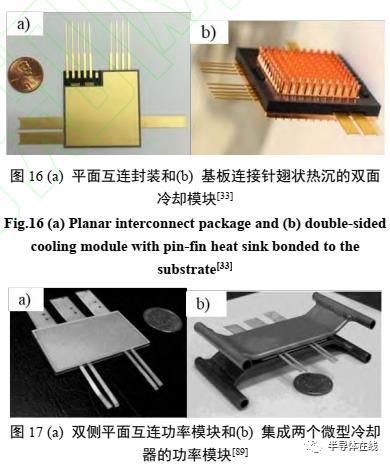

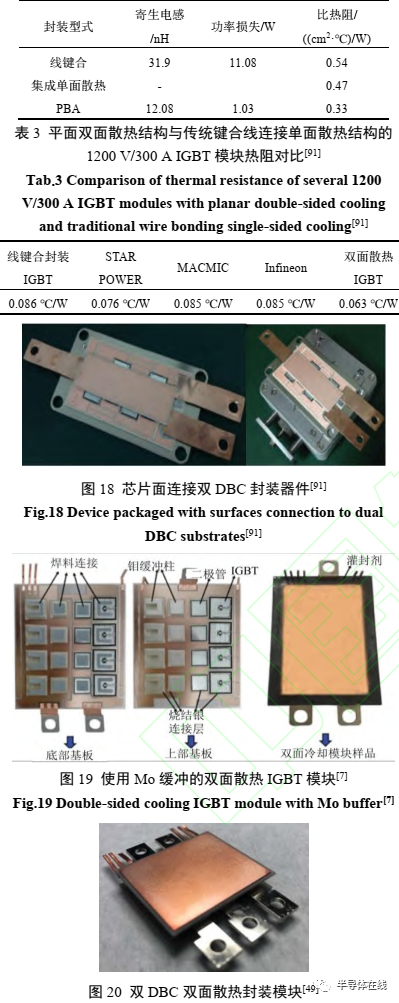

2.2.2 雙基板雙面散熱

(1)雙 DBC 雙面散熱 由上述雙面散熱器件的特點發現,要實現雙面散熱,需要對芯片的兩個表面實現面連接,這樣才能在芯片兩側形成兩個平面,實現兩個熱通路。另一種實現面連接的方式是在芯片的兩側均采用 DBC 基板連接。通過采用“Planar-bond-all,(PBA)” 的功率模塊封裝方法可以在芯片的上表面實現大面積鍵合平面互連。芯片正面朝上/朝下鍵合在兩個 DBC 之間,兩個銅制熱沉直接連接在兩側 DBC 的外表面上。封裝時將 DBC 基板、芯片、墊片、鍵合材料、功率端子等組裝在夾具中,然后同 時加熱形成鍵合。雙側平面鍵合可以使封裝的上下兩個表面都成為散熱通路(圖 16-圖 17)。此外,熱 沉與 DBC 基板直接連接進一步降低了封裝熱阻。PBA 封裝雙面散熱比傳統鍵合線連接單面散熱熱阻降低 38%,表明 PBA 雙面散熱封裝的優勢。雙 DBC 封裝實現雙面散熱的研究還有很多(如圖 18~圖 20),雙面散熱得益于芯片封裝的 兩個表面平臺,給連接 DBC 提供了可能,實現了兩個散熱路徑。表 2 和表 3 對比了雙面散熱結構與 傳統鍵合線連接單面散熱結構的熱性能對比,可以看出雙面散熱結構具有明顯的優勢。

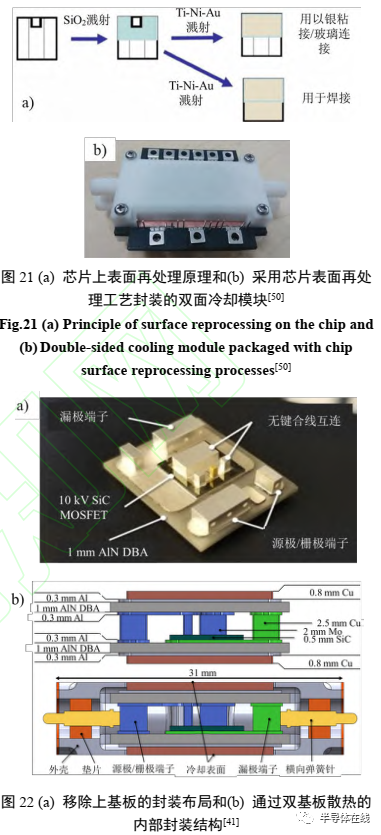

針對面連接,由于芯片柵極焊盤尺寸小和柵極位置,增加了芯片正面連接的難度。研究人員提出了柵極擴大的方法(圖 21)。通過對芯片的柵極焊盤進行再加工和擴大的再處理方法,增大柵極焊盤的面積,使得面接觸更容易實現,進而獲得雙面散 熱路徑,使該封裝具備雙面散熱的能力。

類似于上述雙 DBC 基板封裝雙面散熱器件, 創新性的橫向彈簧針端子和 Mo 柱互連解決了現有標準化封裝在功率密度和熱性能方面的不足,提供芯片頂部和底部的熱通路,從而提高散熱能力(圖 22)。采用燒結銀將芯片連接在兩個高導熱 AlN 陶瓷 DBA 基板之間,通過 Mo 柱將芯片的源極和 柵極連接到上基板,減輕了熱機械應力,改善了可靠性。Cu 柱支撐封裝兩側的基板,并為橫向彈簧針端子提供安裝表面,橫向彈簧針穿過 3D 打印的外殼將模塊連接到高壓 PCB 母線。外殼和彈簧針端子之間采用硅膠墊圈密封,防止密封劑泄漏。將器件安裝在兩個 PCB 母線之間,可以實現高密度集成 和高度模塊化。采用納米銀燒結將 Mo 柱、SiC 芯 片和 Cu 柱連接到基板上。相比合金焊料,燒結銀導熱性能優異,有助于降低芯片連接層的熱阻。可在兩側基板表面分別連接熱沉進行雙面散熱。該雙面散熱封裝模塊的結殼熱阻僅有 0.17 ℃/W,封裝 耗散功率密度超過 200 W/cm2,而同電壓等級的 Cree XHV-9 模塊的結殼熱阻為 0.468 ℃/W,表明該 雙面散熱封裝具有顯著的熱性能優勢。

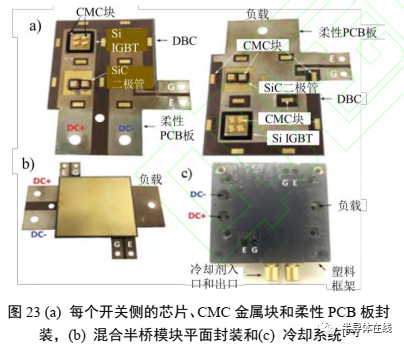

為進一步優化雙面散熱封裝器件的熱性能,提出了柔性印刷電路板互連的平面封裝結構,采用 Cu-Mo-Cu(CMC)復合金屬塊滿足絕緣要求(圖 23)。柔性 PCB 板既可以作為芯片上較小特征的互連,還可以代替傳統的母線,縮短功率模塊的電氣回路長度減小寄生電感。采用銀燒結將芯片和柔性 PCB 板分別連接到兩個 DBC 上,將 CMC 金屬塊燒結到每個芯片的表面,隨后將兩個 DBC 板焊接在一起并進行真空灌封硅凝膠密封。兩側 DBC 外表面為器件散熱提供了雙散熱通路。

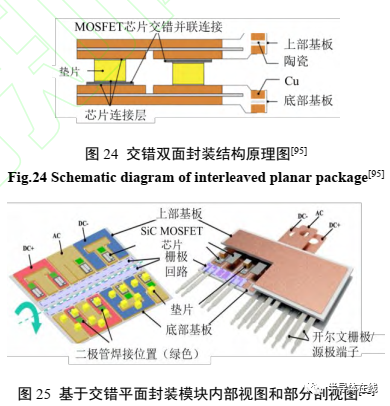

高溫環境下 SiC MOSFET 電流容量降低,并聯 芯片通常由于并聯分支間的寄生不匹配導致電流 不平衡,進而導致芯片溫度分布不均,且并聯芯片間熱耦合嚴重,影響器件散熱。研究者提出一種交錯平面封裝的新型半橋封裝結構,該結構基于平面 封裝原理,具備雙面散熱能力(圖 24-圖 25)。交錯 平面封裝使任意兩個相鄰的并聯芯片在空間上交錯排列,可以避免芯片間的熱耦合,實現更好的熱性能。上下基板分別起到導電、導熱、絕緣和機械支撐的作用。由 CMC 制成的墊片可以傳導電 流、傳遞熱量、保證電氣絕緣距離,并具有與芯片和基板相匹配的可調節熱膨脹系數(CTE)。交錯平 面封裝方法通過增加相鄰芯片間的距離來減小等效耦合熱阻,拉長熱耦合的傳熱路徑,具有均勻且 較小的熱耦合效應。這種封裝方式利用了 3D 封裝結構靈活性的優勢,增大傳熱距離,但沒有增大功 率模塊的尺寸。具有低熱耦合效應、更均勻的溫度分布和出色的熱性能。在相同的耗散熱和散熱條件 下,與傳統芯片布局封裝模塊最大結溫 155.8℃, 封裝內部最大溫差 12.3℃相比,交錯布局封裝最大 結溫為 135.2℃,封裝內部最大溫差僅 3.4℃。顯然, 交錯封裝模塊的溫度分布更加均勻,可有效降低封裝熱阻和芯片間的熱耦合不均勻程度。

(2)雙 MMC 基板雙面散熱

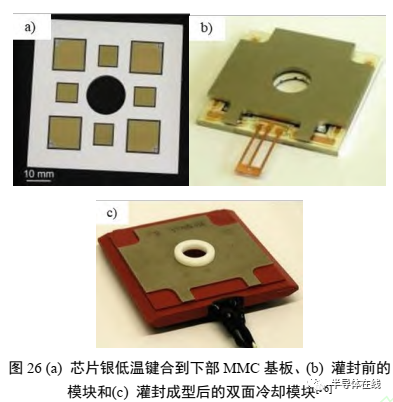

采用低溫銀燒結鍵合(LTB)技術將芯片對稱布置在金屬基復合(MMC)基板的中心安裝孔四周(圖 26),使模塊與熱沉間保持良好的電氣接觸和熱接觸。芯片正面的功率電極通過高熔點焊料連接到上部 MMC 基板,兩個基板與芯片兩個表面緊緊接觸, 芯片的兩側(芯片燒結層-MMC,芯片層焊料-MMC) 均成為散熱路徑。雖然芯片正面的功率電極取消了鍵合線,但柵極仍需采用鍵合線連接。最后,使用硅橡膠成型,使模塊易于集成,同時滿足爬電和間隙距離要求。該封裝技術非常適合于需要冷卻的高 功耗器件。

2.2.3 無基板雙面散熱

(1)PCoB 連接雙面散熱

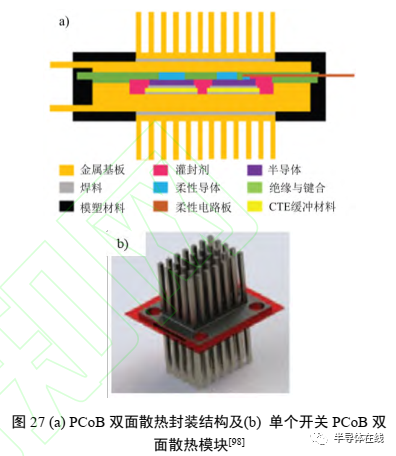

雖然雙基板封裝具備雙面散熱的能力,但基板與底板連接,引入寄生電感,同時存在基板熱阻較大的問題,為提高器件的電氣性能和熱性能,研究人員提出了一種功率芯片連接在總線上(Power Chip on Bus,PCoB)的雙面散熱封裝方法(圖 27), 將芯片連接到 2 個母線狀金屬基板上,基板通過預先成型的環氧樹脂粘合在一起,金屬基板相對于陶瓷基板具有更優異的導熱性能。厚翅片銅既作為熱沉又作為母線。鉬墊片用作芯片和底部基板間的熱膨脹緩沖層,以降低因熱碰撞系數(CTE)失配引起的熱機械應力。芯片下表面焊接連接,上表面采用載銀硅樹脂連接,以進一步降低熱機械應力。柵極端子與聚酰亞胺柔性電路板連接。通過空氣實現散熱器與環境間的電氣絕緣。芯片兩側的基板表面為 翅片狀熱沉的連接提供了平臺,可使用介電流體(如 空氣)進行冷卻,該 PCoB 雙面風冷模塊具有與液冷等效的散熱性能。研究表明,采用該封裝的 1200 V/50 A SiC 肖特基二極管在空氣流速為 15 CFM 的條件下測試得到模塊結到環境的熱阻僅為 0.5 ℃/W。在沒有散熱措施時,結到環境的熱阻也低于 5 ℃/W。而對于類似大小的芯片,采用 25 mil 的AlN陶瓷基板和12 mil的鍍鎳銅底板封裝的傳統功率模塊的結殼熱阻已達到約 0.4 ℃/W。將該模塊 通過導熱脂連接在液冷散熱板上,結到冷卻液體的熱阻為 0.6~1 ℃/W。表明該 PCoB 雙面空冷模塊具 有與傳統液冷模塊相當的熱性能。

(2)壓接封裝雙面散熱

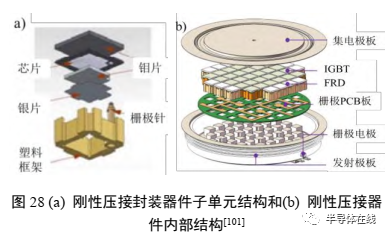

壓接器件通過施加一定的機械壓力實現芯片與外部電極的電氣互連與熱接觸。壓接器件根據 接觸方式不同分為剛性壓接和彈性壓接兩種。剛性壓接器件(如圖 28)主要以 WESTCODE 和 TOSHIBA 等公司的器件為代表,主要由集電極銅板、集電極 Mo 片、芯片、發射極 Mo 片、銀墊片、 柵極針、框架、柵極 PCB 板、凸臺、發射極銅板和外殼等構成。Mo 片作為熱應力緩沖層,柵極針兩端分別連接到芯片柵極和 PCB 板,傳遞驅動信號。銀墊片可以緩解芯片間的壓力分配不均,集電極與發射極銅板外表面可安裝散熱裝置實現雙面散熱。器件工作時通過夾具施加一定的壓力以降低接觸電阻與接觸熱阻,保證封裝器件材料間的良好電熱接觸。但在多芯片并聯封裝器件中,由于剛性壓接器件子模塊數量多,不同子模塊內的芯片、Mo 片以及墊片的厚度難以保證完全一致,各子模塊間就會存在高度差,當將眾多子模塊封裝在同一器件內時,就會存在子模塊承壓不均的問題,影響子模塊的接觸電阻和接觸熱阻。因此,剛性壓接器件普遍對封裝部件的加工精度要求較高。熱性能方面, 以 WESTCODE 4500 V/3000 A press-pack IGBT 模塊為例 , 其最大結溫為 125℃, 模塊熱阻 為 0.0042 ℃/W,表現出良好的熱性能。

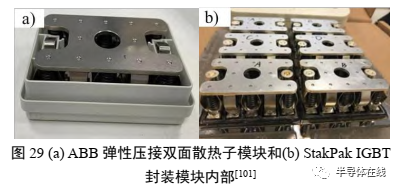

彈性壓接器件以ABB的StakPak彈性壓接雙面散熱器件為代表。彈簧端子的可壓縮性很好地補償 了剛性壓接器件各封裝部件的尺寸差,補償加壓過程中的壓力不足并吸收材料熱膨脹過程的過應力, 結構主要由發射極板、碟簧組件、銀/鋁墊片、Mo 片、芯片、集電極板等構成。圖 29(a)為彈性壓接器件子模塊。碟簧組件近發射極側一端通過鉚接與發射極板連接,碟簧組件另一端為圓柱表面,與芯片上表面的銀墊片形成面連接,Mo 片作為緩沖層以減小熱應力對芯片的沖擊,芯片底面焊接在集電極板上。集電極板和發射極板提供了兩條散熱路徑。雖然該器件具備雙面散熱的能力,但由于碟簧的結構設計以及碟簧組件部分材料熱導率較低,使得通過碟簧側的散熱量非常有限,芯片產生的熱量幾乎都從集電極側的熱通路傳遞,削弱了其雙面散熱的性能。但即使這樣,相比 WESTCODE 4500 V/3000 A press-pack IGBT 模塊,ABB 4500 V/3000 A 彈性壓接 IGBT 模塊僅具有 0.003 ℃/W 的結殼熱阻,熱性能進一步提升。

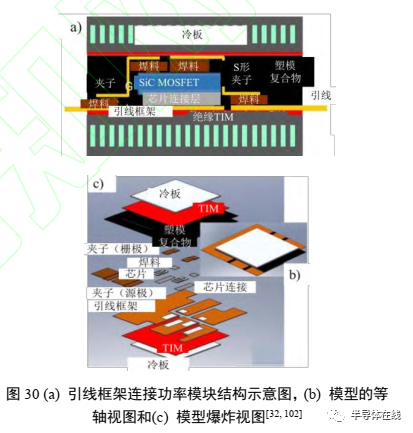

(3)引線框架(LF)連接雙面散熱

雖然芯片兩側均采用 DBC 基板封裝可以實現雙面散熱,但 DBC 基板仍具有較大的熱阻,因此, 基于對 DBC 基板的優化展開研究,開發了一種新型的基于銅引線框架(LF)的雙面散熱封裝方法(圖 30)。該方法采用專用的銅引線框架消除了傳統的陶瓷基板,實現輕薄封裝。芯片直接連接到定制的金屬引線框架上,通過定制的銅夾將芯片電極與引線框架進行焊接,形成柵極和源極的互連。由于在芯片上部采用扁平銅夾連接,使得芯片上部具備連接散熱器的條件。該定制化的銅引線框架同時也作為封裝外部電氣連接的引線端子。芯片和銅夾連接完成后,通過電氣絕緣熱界面材料(TIM)將液 冷散熱器分別連接到銅夾上表面和引線框架的下表面,實現雙面散熱。研究表明,在單個芯片熱耗散功率為 90 W,熱導率為 2.9 W/(m·K)的 50 μm 厚 熱界面材料,塑封料熱導率為 0.8 W/(m·K),采用燒結銀進行芯片連接,芯片電極采用焊料連接的條 件下,仿真得到雙面散熱封裝模塊結到冷卻流體的熱阻為 0.227 ℃/W。

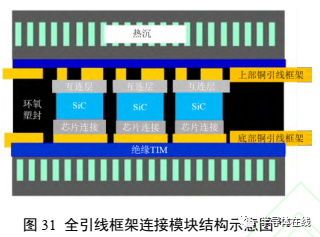

類似于上述引線框架連接封裝,進一步開發了一種全引線框架連接方案(圖 31)。該方案將芯片上下表面的電極均采用銅引線框架引出,然后用環氧成型復合(EMC)材料將引線框架和芯片整體成型。通過介電 TIM 薄層將兩個微通道散熱器分別連接到兩側的引線框架表面,形成雙面冷卻。該模塊通過去除厚重的 DBC 基板以及長回路鍵合線,使得封裝更加輕薄。在單個芯片熱耗散功率為 160 W, 熱導率為 16 W/(m·K)的 100 μm 厚 TIM 層,銅引線框架厚度為 0.4 mm,熱沉冷卻流體流量為 2 L/min, 芯片漏極采用燒結銀連接,柵極和源極采用焊料連接的仿真條件下,得到該雙面散熱封裝模塊的芯片結溫差在 4℃以內,芯片溫度較為均勻,芯片到冷 卻流體的熱阻為 0.152 ℃/W。相比前者,全引線框架連接封裝的熱性能得到進一步提升。

(4)多功能組件(MFC)雙面散熱

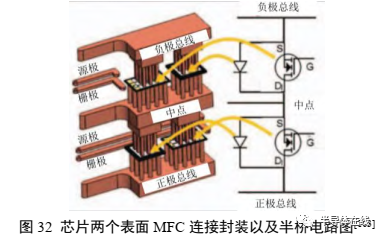

針對當前標準平面封裝受限于包括散熱、可靠性和寄生電感在內的問題,電力電子器件無法充分發揮其全部性能,研究人員提出了一種將芯片堆疊在集成有散熱器的銅母線之間的新型功率器件封裝方法(圖 32)。該方法通過器件堆疊,模塊不再受到平面封裝的限制;通過將散熱器直接集成到芯片的上下表面來解決散熱能力受限的問題。該封裝的關鍵是多功能組件(MFC),MFC 同時承擔著電氣、熱和機械連接的功能。堆疊結構降低了寄生電感并通過減小封裝體積提高了功率密度。這種共同設計的方法旨在消除單一功能組件,如采用 MFC 代替單一導電的焊線和散熱器。空氣或其他介電流體可以直接流過芯片的上下表面以及與芯片直接相連的翅片,對芯片進行雙面冷卻。在芯片熱耗散功率為 500 W/cm2,初始溫度為 20℃,流量為 6 kg/min 的 HFE7500 冷卻條件下,仿真得到封裝器件溫升為 124.6℃,封裝熱阻為 0.25 ℃·cm2/W,遠低于標準功率模塊的熱阻。

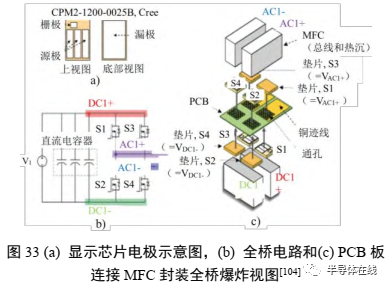

上述 MFC 連接封裝中,芯片柵極仍需使用鍵合線連接,在半橋模塊封裝中,仍需要較長的柵極 回路(圖 32)。研究人員開發了一種基于 PCB 板連接的緊湊型低寄生、無焊線全橋模塊(圖 33)。半橋電路為垂直回路設計,功率回路和柵極回路的電感較低。所有芯片均以柵源朝向 PCB 板的方式連接。半橋上的芯片對角布置在 PCB 板兩側。芯片源極通過 PCB 板上的通孔和另一側的銅制墊片連接到 PCB 板兩側的交直流母線上,最大限度地減小開關節點和直流導軌間的寄生電容。銅或銀制成的母線具有很高的熱導率,同時可以作為熱沉使用, 因此也被稱作 MFC。芯片一面與 MFC 直接接觸, 另一面通過 PCB 板的通孔和墊片與另一側的 MFC 間接接觸,因此被稱為準雙面(QDS)散熱結構。最簡單的 MFC 結構可以使用金屬塊,通過自然對流進行冷卻。對于更高功率損耗的應用,可以考慮有類似幾何形狀且具有內部微通道的強制冷卻散熱器。由于該結構的 QDS 特性且芯片和 MFC 之間取消了熱界面材料(TIM),因此可以顯著提高熱性能。研究表明,采用強制空氣微通道冷卻器作為 MFC 時,結到環境熱阻約為 1.9 ℃/W,而采用 HFE7500 進行液冷時,芯片結到冷卻劑的熱阻僅為0.3 ℃/W, 熱阻大幅降低,因此,在相同的熱耗散情況下,液冷模式可大大降低 MFC 的尺寸。

基于上述雙面散熱封裝綜述,此類結構的特點是無鍵合線封裝。以大面積面接觸代替鍵合線點接觸,充分利用芯片的兩個表面,繼而可以在芯片兩側的封裝平面上連接散熱器進行冷卻,實現雙面散熱。從具體封裝結構上來看,主要有單基板(上基板、 芯片嵌入基板(中基板)、下基板)封裝雙面散熱、上下雙基板封裝雙面散熱以及無基板封裝雙面散熱。芯片電極平面接觸是實現雙面散熱的前提。芯片上下雙基板封裝是易實現雙面散熱的方式,但常規 DBC 基板厚度較大,熱阻大,影響器件的熱性能。去基板封裝,芯片連接到厚度較薄的金屬上(如銅引線框架),散熱路程短且熱導率較高,非常有利于散熱。基于雙面散熱封裝目標,采用高導熱材料平面鍵合同時縮短散熱路程是提高雙面散熱封裝器件散熱能力的主要途徑。另外,創新結構設計,開發 多散熱路徑的封裝方案也在持續探索和發展中。

2.3 封裝結構多面散熱

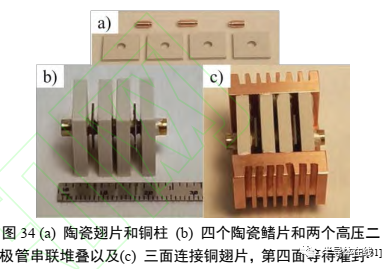

針對目前高壓 SiC 器件封裝體積大、散熱和耐壓不足的問題,研究人員提出了改善封裝尺寸和功率密度的二極管緊湊堆疊封裝方案(圖 34)。采用協同設計高壓 SiC 模塊,器件通過 3 mm 厚 AlN 陶 瓷片將熱量傳遞給外部散熱器。整個模塊由兩個端蓋和四個空冷(或液冷)散熱器組成。銅柱插入到 AlN 中間的孔中,AlN 的四周與銅散熱片連接,端蓋置于兩側。銅柱、陶瓷翅片和外部銅翅片作為多 功能組件(MFC)。銅柱既作為電氣連接又將熱量傳遞給陶瓷翅片。陶瓷翅片既作為絕緣體又作為導熱 體。外部銅翅片作為模塊外殼和散熱器使用。選用高導熱環氧樹脂將銅柱連接到陶瓷翅片上和芯片的兩側。在陶瓷翅片四周均勻涂抹陶瓷基 TIM,然后將銅翅片連接在上面,兩種翅片的邊緣結合處采用高溫樹脂密封。將三個銅翅片按照上述方式連接,留出一面用于灌封。將 ABS 塑料端蓋安裝在兩個端部,用高溫樹脂密封。最后將灌封劑注入到所有的空腔,使每個陶瓷片的兩面都被涂上。灌封劑在固化前進行脫氣處理,確保模塊中沒有氣體殘留。灌封和固化完成后,將最后一側的銅翅片安裝到陶瓷翅片上并進行密封處理。該封裝在模塊的四個側面安裝熱沉,可顯著提高散熱能力。

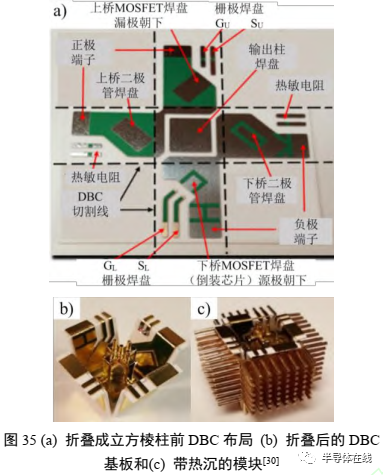

針對寬禁帶功率器件散熱面積有限,器件功率受限的問題,提出了一種新的多側散熱的三維棱柱形功率器件封裝方法(圖 35)。該封裝在模塊的五個側面各安裝了一個針翅散熱器。通過在 DBC 基 板的背面設計斷裂槽(切割槽),基板上部的銅層與 斷裂槽重疊,這樣在折疊時,上銅層就形成了鉸鏈。將各封裝部件和輸出端子焊接到基板上,芯片通過高溫焊料連接到輸出柱上,然后進行高溫硅凝膠絕緣灌封,將散熱器焊接到輸出端子以外的其他五個側面,形成多面散熱。通過熱仿真分析,在對側芯片上施加總功率為 30 W 的熱損失,采用初溫為 20℃、流速為 7 m/s 的空氣強制冷卻時,芯片最大結溫為 95°C,封裝結到空氣的熱阻小于 2.5 ℃/W, 結殼熱阻僅有 0.3 ℃/W。與單面散熱模塊相比,多面散熱熱阻降低 22%。

基于上述多面散熱封裝結構,立體式封裝是其 具有多面散熱能力的前提。創新性的將器件封裝結構從二維平面拓展到三維空間,也拓展了封裝器件的散熱空間。目前多面散熱封裝器件的研究和開發還比較少,高壓方面僅限于二極管,低壓方面已有 SiC MOSFET 的封裝嘗試。多面散熱大大拓展了器件的散熱路徑,這是現有封裝技術所不具備的。功 率器件的封裝,最終呈現的是多因素的綜合,在拓展散熱路徑的同時,滿足封裝絕緣要求是至關重要的。面對器件高壓大功率的發展趨勢,高絕緣和高散熱能力是未來器件封裝需要考慮的首要因素。多面散熱封裝為創新器件封裝結構設計提供了借鑒, 鼓舞了對新型散熱封裝結構設計的研發熱情。

3 功率器件封裝散熱發展趨勢

由上述對器件封裝結構散熱的綜述和總結,器件封裝結構散熱從鍵合線封裝和無鍵合線封裝的單面散熱到去鍵合線雙面散熱再到多面散熱,代表了功率器件封裝結構散熱的發展趨勢,即從單一散熱路徑發展為多散熱路徑,這也是器件發展和用途 需求倒逼器件封裝需要更優異散熱性能的結果。之 前在功率器件封裝方面的努力主要是由鍵合線標準器件驅動,芯片通常只能通過非鍵合線側進行散熱。出于電氣絕緣和鍵合可靠性的考慮,鍵合線側未被用作散熱通路。這一設計在面對高溫高壓大功 率器件應用場景時,已不能滿足高性能器件的封裝要求。高導熱封裝材料及連接工藝、去鍵合線連接、 大面積面接觸、多散熱路徑同時縮短散熱路程、降低散熱路徑的熱阻等可能是未來高壓高溫大功率器件封裝應具備的關鍵特征。

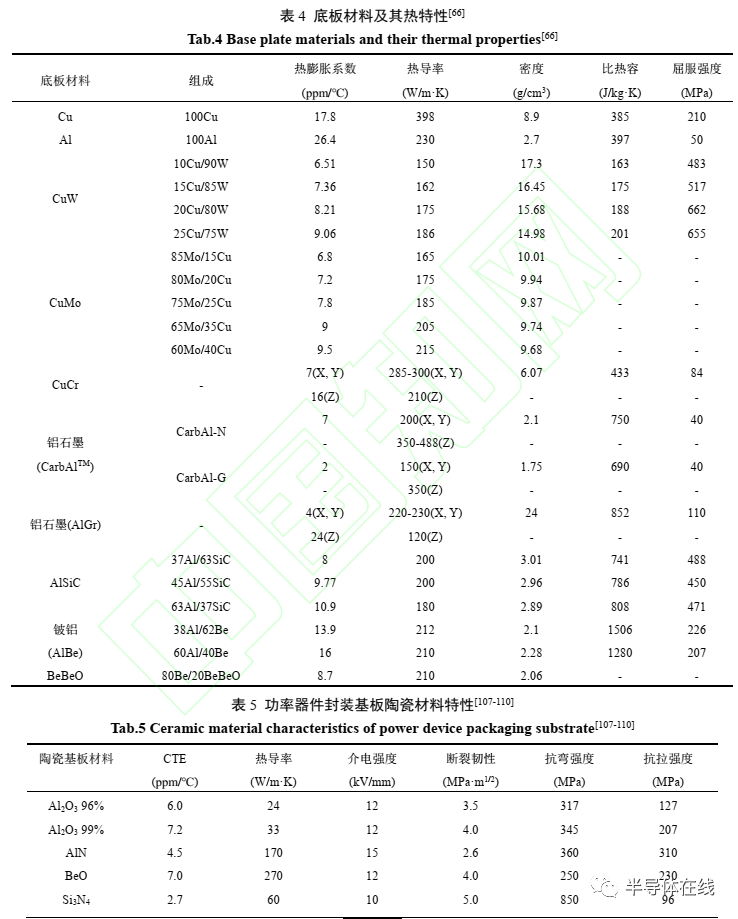

3.1 高導熱封裝材料和連接工藝

對于功率器件封裝,要想獲得優異的熱性能, 首先要采用高熱導率的封裝材料和先進連接工藝, 使封裝各層材料及其連接層均有利于熱量的傳導。 通常,金屬和合金的熱膨脹系數與熱導率之間是相互矛盾的,但金屬基復合材料(MMCs)提供了 一種很好的折中。雖然其成本較高,但仍是一類非常有潛力的底板材料。AlSiC 具有優異的導熱性能, 且能夠很好地匹配 DBC 的熱膨脹,降低熱膨脹應力和熱失效或者振動失效的風險。底板通常占整個模塊一半以上的重量,對器件熱性能有積極的也有負面的影響,這主要是考慮到傳熱和自身厚度的綜合作用。表 4總結了適用于功率模塊高溫封裝底板材料的熱性能。底板的熱性能很大程度上受到底板面積的影響,并隨底板厚度的增加而提高。原因是由底板厚度帶來的熱阻增大的消極影響被大底板面積所帶來的積極影響而抵消,但底板位移也會相應變大。 基板作為功率模塊的必要組成元素,起到提供電氣連接、高壓絕緣和熱耗散路徑的作用。理想的 基板材料需要跟與其連接的其他元件間具有良好的熱膨脹匹配性、高熱導率、高抗彎強度以及高斷裂韌性。通常采用在陶瓷表面鍵合金屬層的三明治 結構制作基板。但由于金屬和陶瓷層間的熱膨脹系數的差異,金屬鍵合的厚度、陶瓷的脆性和熱應力 是在選擇功率基板時需要考慮的問題,同時也是比較棘手的問題。 DBC 基板需要滿足電氣、熱以及機械可靠性要求。在各種候選材料中,夾在兩層銅之間的常用陶瓷有 Al2O3、BeO、AlN 和 Si3N4。表 5 總結了 上述幾種材料的性質。

其中,Al2O3最常用且成本 最低,但是與 BeO 相比,Al2O3熱導率較低,對于高功率器件封裝,通常不是好的選擇,尤其是在高 溫條件下。雖然 BeO 具有較高的熱導率,但由于機加工過程產生粉塵危害健康的原因需要特殊的制 造和加工工藝,這必然增加了成本。AlN 材料由于其優異的電性能和化學穩定性成為 SiC 器件封裝的理想候選材料。其具有高熱導率同時能夠匹配 SiC 的低熱膨脹系數(4.6-5.1 ppm/℃),且成本低,易獲取。但是其機械強度差、鍵合難度大。Si3N4熱導率適中,機械性能出色,可彌補其在導熱性上的差距。 在實際應用中,AlN 需形成 0.64 mm 厚的薄板以承受鍵合過程的應力,而 Si3N4比較堅固,0.32 mm 的厚度即可滿足要求。Al2O3或 BeO 在低氧氣氛下對銅或者鋁箔進行加壓并加熱到略低于金屬熔點的溫度形成 DBC 或者 DBA。相比 DBA, DBC 具有低電阻率 、 高熱導率 (390 vs 240 W/(m·K))和易刻蝕的優勢;但 DBA 在改善熱循環可靠性方面更具優勢,氧化鋁和陶瓷間的結合力比氧化銅要強得多,鋁更軟,對應變硬化具有更 大的抵抗力。研究表明,DBC 在-50~250℃下經過 100 個熱循環后會發生金屬分層的失效問題, 對于高可靠性系統,相比 DBC 基板,DBA 能夠承受更加嚴苛環境下的熱循環。因此,DBA 具有更好的熱循環性能和高溫可靠性。

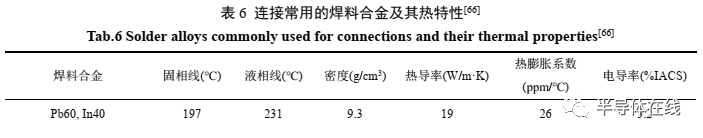

功率器件連接工藝通常有焊接和燒結連接兩種。焊接工藝采用焊料合金連接,燒結工藝通常采用納米銀和納米銅連接。焊料合金(如 SnPb 和 SnAgCu)是最常用的芯片和基板互連材料。但傳統焊料連接層熱導率通常較低,僅有幾十 W/(m·K)(表 6)。納米金屬燒結可實現封裝材料間的高導熱連接,熱導率一般都在數百量級, 非常有利于熱量的傳導。目前,納米金屬燒結連接仍處于研究階段,尚無法實現大面積燒結連接。 金基焊料,如共晶 AuSn,具有高溫(>280℃)、 高導電和高導熱性以及易無助焊劑焊接的特點而受到青睞。然而,由于其剛度特性和高成本, 僅適用于小規模應用。 銀具有高導電導熱性,非常適合于高溫封裝, 但同時也具有非常高的熔點(960℃)。為了降低燒結溫度,通常有兩種策略:一是利用壓力來增加 燒結驅動力,另一種是利用無壓的納米顆粒。新的研究嘗試在使用納米顆粒的同時施加一定的壓 力。但是有壓燒結難以實現自動化,成本增加。同時,施加壓力也可能會導致芯片碎裂。通過將銀顆粒尺寸從微米級減小到納米級,可以獲得額外的表面能,理論上該過程可以在 300℃以下的 無壓條件下進行,從而降低燒結溫度。

研究表明, 采用納米銀燒結連接,芯片和基板間的結合非常牢固。銀燒結互連具有低溫(>220℃)和高熔點的鍵合優勢,同時具有高導熱性,能夠增強熱循環和 功率循環的可靠性。納米銀漿料具有較大的表面積,燒結溫度較低,燒結接頭具有優異的導熱、 導電以及高溫穩定性。商用納米銀可以在 250℃ 的溫度下燒結。盡管 Semikron、Infineon 和 ABB 等廠商進行了大量的燒結銀研發工作,并在早期 產品中應用了該技術,但到目前為止,銀燒結技術在量產方面還很有限,面臨著尚未完全解決的 可制造性和成本挑戰。封裝過程復雜、過程伴隨壓力和表面金屬化以及大面積芯片的連接等問 題仍需要解決。弗吉尼亞理工大學于 2017 年設計了高功率密度和高開關速度的 10 kV/54 A SiC MOSFET 模 塊。在 DBA 基板上印刷 200 μm 厚的銀膏層,在 120℃下進行干燥并蒸發掉所有溶劑。干燥結束后 在 260℃、5 MPa 的壓力下燒結 1 h 將兩個 DBA 基板燒結在一起。針對芯片連接,分別研究了焊 料和無壓銀燒結兩種方式。采用 Indium 50 μm 厚 含有助焊劑的 96.5Sn/3.5Ag 焊料預制件,在空氣氣氛下 260℃焊接到鍍銀 DBA 基板,焊接強度為 36 MPa,焊層空洞率約 40%-50%。采用無壓燒結 銀膏連接時,對于不同類型的 Ag 膏,Kyocera’s CT2700R7S Ag 膏在 200℃下燒結 90 min 時鍵合 強度最高(>45 MPa)。

但在相同條件下燒結較大面 積的芯片時,芯片剪切強度明顯降低,將燒結溫度提高到 230℃,芯片剪切強度得到明顯改善。需要注意的是,10 kV SiC MOSFET 芯片下表面鍍 有 Au,由于 Ag 會往 Au 層中擴散,若 Ag 擴散較 多會在 Ag-Au 界面產生 Kirkendall 空隙,降低鍵合強度。雖然有壓燒結能夠產生致密銀層,提高剪切強度,但是有壓燒結更加復雜,尤其是在同時燒結多個芯片時壓力均勻分布的問題。該團隊在 2020 年針對無鍵合線封裝的 10 kV SiC MOSFET 模塊,采用無壓納米銀燒結進行功率基板、芯片和金屬柱之間的連接,芯片在 230℃下 燒結 90 min,平均剪切應力為 15 MPa,峰值應力 達到 18 MPa。采用壓力輔助銀燒結將兩個基板連接在一起,相比焊料連接,銀燒結層具有低孔隙率、高熱導率和更高的可靠性。同時,銀燒結漿料不能直接與 Cu 結合,需要 Au 或 Ag 等界面金屬化來加強結合,增加了整體成本。此外,由 于有機揮發物的蒸發使得燒結接頭局部致密化, 燒結接頭產生孔隙。在大尺寸的芯片燒結連接中, 空洞現象更加嚴重。孔隙的存在會降低燒結接頭的力學、熱學和電學性能。不含有機物的納米銅燒結在芯片連接驗證中可加工性得到改善,應力管理設計更加靈活,使其成為功率芯片高溫連接 材料的潛在替代品。

2016 年美國洛克希德馬丁空間系統公司將開發的一種新型納米銅基封裝材料用于 LED 和熱沉之間的連接,同樣也適用于其他晶圓級高功率芯片的封裝連接,以實現高熱導率。這種無焊料的納米銅克服了傳統焊料的加工溫度對后續最大可能操作溫度的限制。由于納米銅可在 280℃ 以 下熔化 , 熔化后恢復成塊狀銅 ( 熔點 1084.87℃),熱導率和導電性是典型焊料的 5-10 倍, 且不需要擔心前道工序的連接層發生回流,因此能夠在超過其原加工溫度的環境下服役,使其成為理想的高溫封裝材料。銅具有高熱導率(~400 W/(m·K)),且納米銅連接層中沒有空洞。同時該材料的總成本已經低于 AuSn 共晶焊料,在工業規模上,預期將能夠與無鉛焊料競爭。

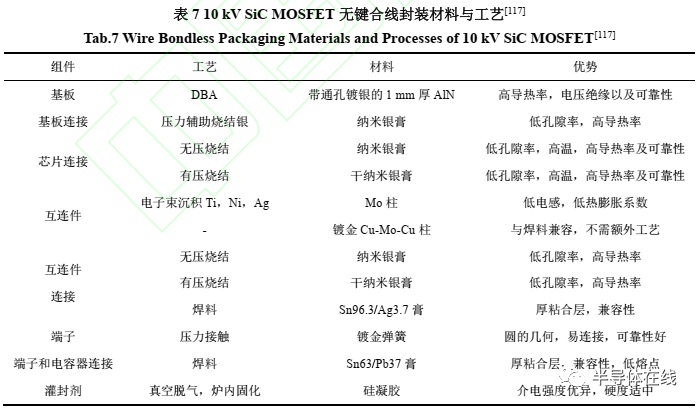

3.2 芯片面接觸連接

鍵合線連接由于芯片引線鍵合及保障鍵合質量可靠性和絕緣的需要,限制了通過該鍵合側安裝 熱沉散熱,僅具有單一散熱路徑。為改善散熱性能, 取消鍵合線,以面接觸代替點接觸連接可增大電極 引出部件與芯片的接觸面積,即增大芯片表面的散 熱面積,是提高器件散熱能力的有效方式。同時也降低較小截面積的長導線鍵合帶來的回路寄生電感,如采用金屬帶代替長導線連接。 采用雙層柔性 PCB 板代替鍵合線實現芯片大 面積接觸連接的 SKiN 封裝,柔性 PCB 板與芯 片有源區的燒結面積大大增加,接觸表面增大改善 了芯片的熱分布和功率循環能力,不足之處在于柔 性 PCB 板的存在限制了其高溫運行的可靠性。 此外,采用平面互連實現芯片正面功率電極的 端子直連(direct lead bonding,DLB) (圖 36),其 最大特點是將功率端子與芯片表面電極直接連接, 相比于傳統引線鍵合的點接觸,該技術的電極端子 與芯片表面互連面積更大,可有效降低寄生電感, 提高互連可靠性。

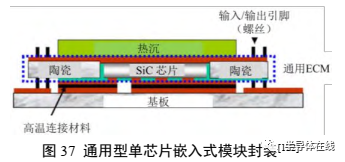

三維嵌入式芯片模塊(Embedded chip module, ECM)封裝也可以實現芯片面接觸連接(圖 37), 將芯片倒裝嵌入到陶瓷中,采用玻璃或者陶瓷粘接 劑將芯片和陶瓷連接,芯片兩個表面金屬化取代鍵 合線,雙面金屬化提供了一個機械平衡結構,可以 減少高溫下的機械應力,同時芯片電極金屬化提供 了較大的面積可以連接熱沉,實現雙面散熱。實現芯片表面電極的面接觸連接,增大接觸面 積,不僅可以減小電流回路,減小雜散電感和電阻, 還可以充分利用芯片兩表面的散熱通路,實現芯片 表面雙散熱路徑,可明顯改善封裝器件的散熱性 能。因此,基于保障功率器件高溫運行可靠性和高 功率密度封裝的考慮,實現芯片的面接觸連接,增 大接觸面積,去鍵合線連接是提高封裝器件熱性能 和實現高功率密度器件封裝的必然要求。

3.3 增加散熱路徑

傳統鍵合線連接器件僅具有單一散熱路徑,熱 性能已達到其散熱極限,不能適應更高功率密度的 封裝要求。從散熱的角度,盡可能多的散熱路徑對 于器件的散熱無疑是有利的。功率器件高溫高功率 密度應用驅使開發散熱性能更好的封裝形式。目前 封裝材料的熱特性短期內無法取得較大的改善,除 現有芯片背面的導熱通路外,拓展新的散熱路徑, 將芯片正面作為另一條散熱通路。盡管由于芯片正 面連接墊片等部件可能使得芯片上下兩側封裝結 構不對稱,通過芯片上表面熱通路的散熱量與芯片 下表面熱通路的散熱量未必相同,但這種雙面散熱 能力可以大幅降低器件的熱阻,顯著提升器件的散 熱性能。增加散熱路徑必然要改變芯片的連接方 式,因此,去鍵合線連接成為增加散熱路徑的必然 選擇。為了實現功率器件的高溫高壓高功率密度應 用,功率器件的封裝由傳統鍵合線連接的單一散熱 路徑發展為去鍵合線面接觸連接的雙散熱路徑。隨 著對功率器件更高溫度、更高電壓等級和更高功率 密度封裝的追求,功率器件的熱耗散越發嚴重,優 異的散熱性能是功率器件封裝永恒的追求,各種新 型的封裝結構也在持續發展中,比如最近關于器件 多面散熱封裝的研究。雖然目前在器件多面散熱封 裝方面的報導還較少,更多的是關于器件雙面散熱 封裝的研究,反應了功率器件封裝由單一散熱路徑 到多散熱路徑的發展趨勢。尤其是對于多面散熱器 件的研究報導,更是展現出功率器件在多散熱路徑 封裝方面的巨大研究空間和潛力。

3.4 縮短散熱路程

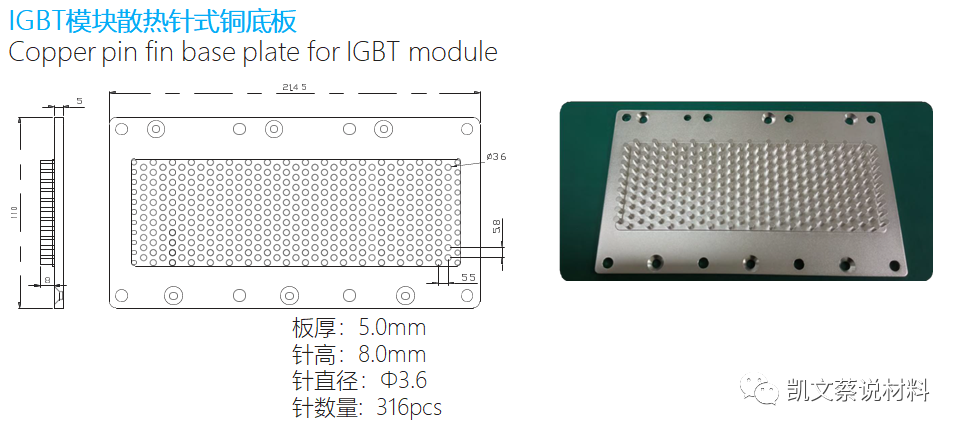

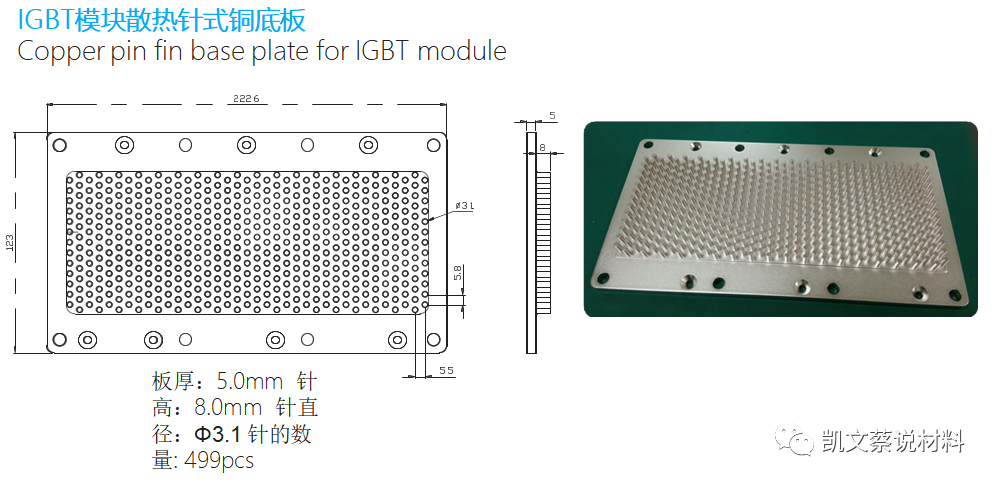

封裝器件內部芯片損耗產生的熱量主要通過 熱傳導的方式將從結傳遞至器件封裝外殼。根據傳 熱學理論和熱量傳遞的規律,縮短熱流傳遞路徑上 的距離,是降低芯片散熱路徑熱阻的有效方式之 一。功率器件封裝是由多層結構組成的,那么從縮 短散熱路徑路程的角度,一是可以減薄封裝各層材 料的厚度,二是減少封裝材料的層數。前者由于當 前材料厚度已經是在滿足絕緣、散熱和力學等方面 要求的折中,材料的介電強度等屬性無法取得較大 的改進,那么從減薄材料厚度的角度可能無法對散 熱路徑的熱阻有較大的改善。縮短散熱路程唯一有 效的方式只能從減少封裝材料的層數著手。從對有 陶瓷基板的器件封裝各層材料的熱阻分析可知,底 板和陶瓷基板的熱阻較大。減少封裝結構層,取消 底板,將陶瓷基板直接與熱沉連接。功率器件 從單個陶瓷基板封裝到無基板封裝,如芯片與金屬 底板(電極板)直接連接封裝、引線框架連接封裝和金屬多功能組件封裝。取消陶瓷基板可大大縮短散 熱路程,降低熱阻,顯著提高封裝散熱性能。因此, 減少封裝結構層數來縮短散熱路程的方式是可行 的,這也產生了高效散熱的緊湊型封裝結構,實現 器件的高功率密度封裝。

4 結論

本文聚焦于功率器件封裝散熱方面,綜述了現 有功率器件在封裝結構散熱方面的設計特征,總結 了功率器件封裝結構的散熱設計原則,通過對現有 功率器件從散熱路徑的角度進行分類,總結其封裝 散熱特點和為追求高效散熱在高導熱封裝材料和 連接工藝、芯片封裝接觸形式、封裝散熱路徑數量 以及散熱路程方面的發展趨勢。本文的結論如下: 1)從封裝器件散熱的角度可以將功率器件分 為單面散熱器件、雙面散熱器件和多面散熱器件。封裝結構設計應當遵循散熱路徑低熱阻、盡可能多 散熱路徑和散熱路徑上的接觸面積盡可能大的原 則。 2)鍵合線連接器件只能通過芯片非鍵合側散 熱,影響了功率模塊的熱性能。在目前封裝材料性 能和封裝工藝技術暫時無法取得較大改善的情況 下,通過創新結構布局和設計,優化散熱路徑,是 解決目前功率器件封裝散熱的有效方案。 3)實現對芯片表面電極的平面接觸是實現雙 面散熱的前提。散熱路徑上采用高導熱材料平面鍵 合同時縮短散熱路徑的路程是提高雙面散熱封裝 器件散熱性能的兩個主要途徑。 4)立體式封裝是封裝器件具備多面散熱能力 的前提。功率器件封裝結構從二維平面封裝拓展到 三維空間封裝,拓展了封裝器件的散熱空間。功率 器件封裝結構熱設計表現出從單一散熱路徑向多 散熱路徑發展的趨勢。 5)高熱導率封裝材料和高導熱納米金屬連接 工藝、去鍵合線連接、大面積面接觸、追求多個散 熱路徑同時盡可能縮短散熱路程、降低散熱路徑的 熱阻等是未來高壓高溫大功率器件封裝應具備的 關鍵特征。

來源:《中國電機工程學報》

作者:

王磊1 ,魏曉光 1,唐新靈 1 ,林仲康 1 ,趙志斌 2 ,李學寶 2

1. 北京智慧能源研究院2. 華北電力大學新能源電力系統國家重點實驗室

-

IGBT

+關注

關注

1265文章

3761瀏覽量

248300 -

功率器件

+關注

關注

41文章

1728瀏覽量

90317

發布評論請先 登錄

相關推薦

半導體IGBT功率器件封裝結構熱設計探討

半導體IGBT功率器件封裝結構熱設計探討

評論