在許多應用中,ADC需要在存在大共模信號的情況下處理一個很小的差分輸入信號。傳統的儀表放大器(In-Amp)只具有單端輸出和有限的共模范圍,因此在這些應用中并不常用。為了充分利用這些器件的高性能和低成本,可以設計一個簡單的電路,將其單端輸出轉換為差分輸出,并且改善其輸入共模范圍,使之更適合這些應用。

許多低成本儀表放大器所具備的帶寬、直流精度和低功耗可以滿足所有的系統要求。使用儀表放大器的另一好處是,用戶無需構建自己的差分放大器,因此省去了很多高成本的分立器件。本文將提出一種簡單的方法來構建一個低成本儀表放大器并優化其性能。此外,該解決方案的成本和性能與單芯片儀表放大器不相上下。

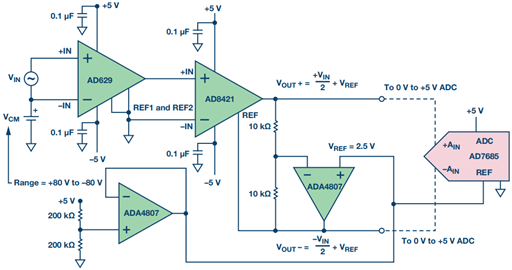

圖1詳細介紹了所提出的精密系統設計,該設計允許用戶在存在高共模電壓的情況下測量差分信號。該電路包括一個輸入緩沖器、一個ADC驅動器和一個基準電壓源。緩沖器驅動儀表放大器的參考引腳,并將單端輸出轉換為差分輸出。該電路具有非常高的輸入共模電壓范圍。它可以處理高達±270 V的共模電壓(采用±15 V電源供電),在正負方向幾乎達到電源電壓的20倍,這是電機控制應用的關鍵。此外,還對輸入提供高達±500 V的共模或差模瞬變保護。

圖1. 單端輸入差分輸出放大器

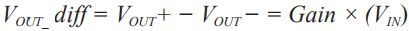

此應用使用±5 V電源,這樣輸入電壓才能具有±80 V共模范圍。差分輸出由如下公式確定:

共模輸出由如下公式設置:

這個電路的好處是直流差分精度取決于AD629差動放大器和AD8421儀表放大器,而不是運算放大器或者外部10 kΩ電阻。此外,這個電路充分利用了儀表放大器對其基準電壓相關的輸出電壓的精確控制。雖然運算放大器的直流性能和電阻匹配會影響直流共模輸出精度,但是這些誤差很可能會被信號鏈路上的下一個器件抑制,因此它對整個系統精度的影響將會很小。

為獲得最佳交流性能,推薦使用具有高帶寬和高壓擺率的運算放大器。此電路中選擇的運算放大器是ADA4807。

為了避免寄生電容使ADA4807不穩定,電阻至反相輸入端之間的走線長度應盡可能短。如果必須使用較長的走線,需使用阻值較低的電阻。高性能ADC通常采用5 V單電源,并具有自身的基準電壓。該基準電壓用作差分輸出的共模電壓,從而無需使用基準電壓源。因此,其輸出與ADC成比例,這意味著ADC的VREF任何變化都不會影響系統的性能。

此差動放大器抑制共模電壓的能力取決于AD629差動放大器內部微調電阻的比例匹配。因此,它比采用分立式放大器的儀表放大器更好。

對于采用0.1%外部電阻的分立式放大器,CMR限制為54 dB。儀表放大器集成了精密的激光微調電阻,使系統的CMR可達到80dB或更高。這些電阻均采用相同的低漂移薄膜材料制成,因此在一定溫度范圍內可提供出色的比例匹配。

ADC可采用5V單電源供電,參考引腳上有2.5V低阻抗電壓源。這樣可將輸出設為中間電源,并升高ADC輸入端呈現的共模電壓。

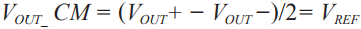

示波器輸出波形曲線如圖2所示。兩個儀表放大器的增益均為1。VIN是一個大共模電壓上的1 V pp 10 kHz正弦波。VOUT+和VOUT–分別是±0.5 V pp正弦波和余弦波。VOUT_diff是1 V pp差分輸出電壓,也就是消除共模信號后的VIN。

圖2. 電路的性能:頂部:兩個互補輸出中間:帶有大共模信號的輸入電壓底部:差分輸出

圖2. 電路的性能:頂部:兩個互補輸出中間:帶有大共模信號的輸入電壓底部:差分輸出

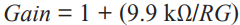

通過增加一個電阻RG可以提高儀表放大器的增益:

此電路也可以用于功耗敏感型應用。總靜態電流為5 mA,采用5V雙電源,其功耗僅約50 mW,相較于其他采用基本ADC驅動器(例如,AD8138和AD8131差分驅動放大器)或分立式放大器的解決方案,功耗節省達50%。

原文轉自亞德諾半導體

-

放大器

+關注

關注

143文章

13553瀏覽量

213113 -

儀表

+關注

關注

5文章

511瀏覽量

33516

發布評論請先 登錄

相關推薦

【世說設計】輕松掌握學會一個低成本儀表放大器設計方法

【世說設計】輕松掌握學會一個低成本儀表放大器設計方法

評論