本文的關鍵要點

?漏極和源極間的浪涌是由各種電感分量和MOSFET寄生電容的諧振引起的。

?在實際的版圖設計中,很多情況下無法設計出可將線路電感降至最低的布局,此時,盡可能在開關器件的附近配備緩沖電路來降低線路電感,這是非常重要的。

首先,為您介紹SiC MOSFET功率轉換電路中,發生在漏極和源極之間的浪涌。

·漏極和源極之間產生的浪涌

·緩沖電路的種類和選擇

·C緩沖電路的設計

·RC緩沖電路的設計

·放電型RCD緩沖電路的設計

·非放電型RCD緩沖電路的設計

·封裝引起的浪涌差異

SiC MOSFET的漏極

和源極之間產生的浪涌

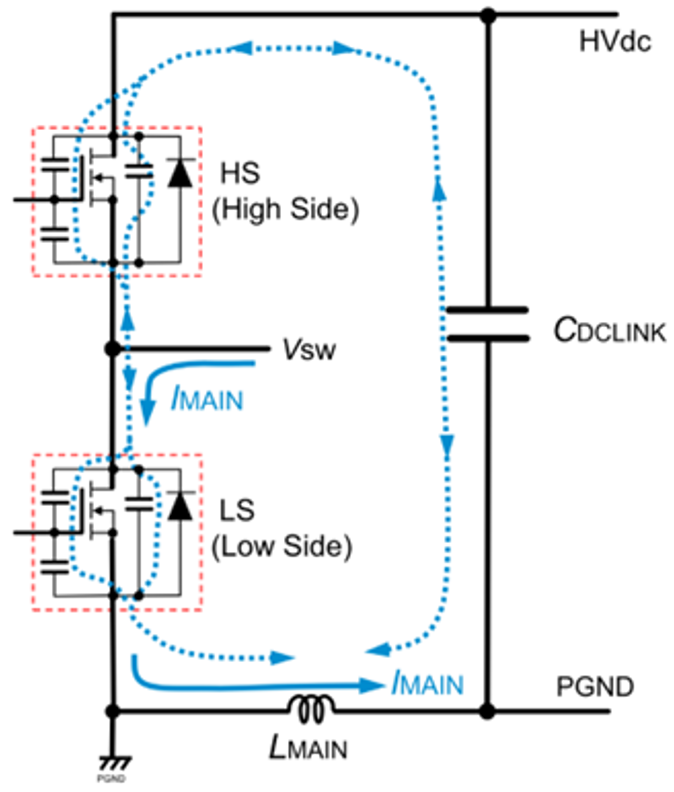

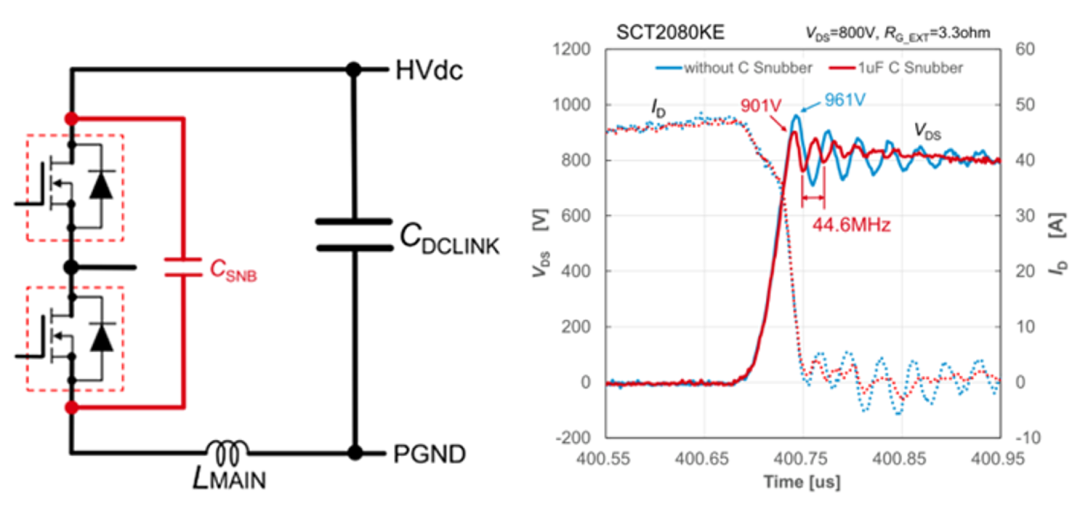

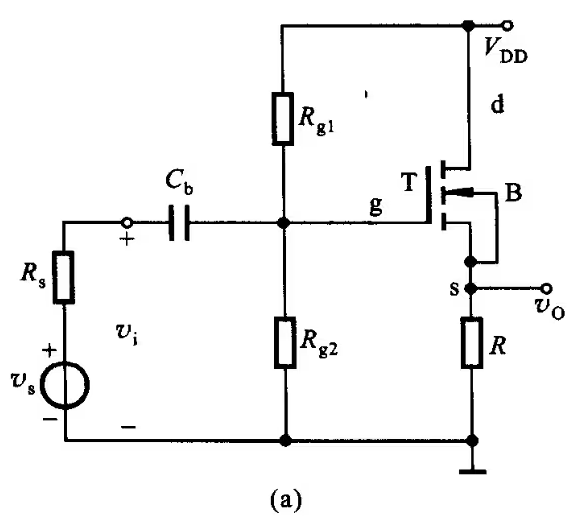

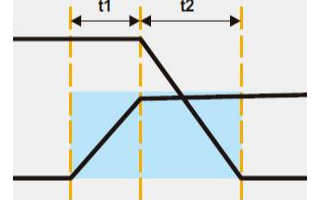

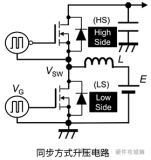

開關導通時,線路和電路板版圖的電感之中會直接積蓄電能(電流能量)。當該能量與開關器件的寄生電容發生諧振時,就會在漏極和源極之間產生浪涌。下面將利用圖1來說明發生浪涌時的振鈴電流的路徑。這是一個橋式結構,在High Side(以下簡稱HS)和Low Side(以下簡稱LS)之間連接了一個開關器件,該圖是LS導通,電路中存在開關電流IMAIN的情形。通常,該IMAIN從VSW流入,通過線路電感LMAIN流動。

圖1:產生關斷浪涌時的振鈴電流路徑

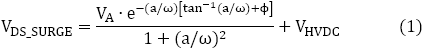

接下來,LS關斷時,流向LMAIN的IMAIN一般是通過連在輸入電源HVdc和PGND之間的大容量電容CDCLINK,經由HS和LS的寄生電容,按照虛線所示路徑流動。此時,在LS的漏極和源極之間,LMAIN和SiC MOSFET的寄生電容COSS(CDS+CDG)就會產生諧振現象,漏極和源極之間就會產生浪涌。如果用VDS_SURGE表示施加在HVdc引腳的電壓,用ROFF表示MOSFET關斷時的電阻,則該浪涌的最大值VHVDC可以用下述公式表示(*1)。

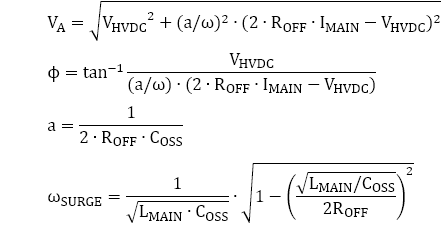

圖2是使用SiC MOSFETSCT2080KE進行測試時關斷時的浪涌波形。當給HVdc施加800V的電壓時,可以算出VDS_SURGE為961V,振鈴頻率約為33MHz。利用公式(1),根據該波形,可以算出LMAIN約為110nH。

圖2:關斷浪涌波形

再接下來,增加一個圖3所示的緩沖電路CSNB,實質性地去掉LMAIN后,其關斷浪涌的波形如圖4所示。

圖3:C緩沖電路

圖4:通過C緩沖電路降低關斷浪涌

可以看到,增加該CSNB之后,浪涌電壓降低50V以上(約901V),振鈴頻率也變得更高,達到44.6MHz,而且包括CSNB在內,整個電路中的LMAIN變得更小。

同樣,利用公式(1)計算LMAIN,其結果由原來的110nH左右降低至71nH左右。原本,最好是在進行版圖設計時,將線路電感控制在最低水平。但是,在實際設計過程中,往往會優先考慮器件的散熱設計,所以線路并不一定能夠按照理想進行設計。

在這種情況下,其對策方案之一就是盡可能在開關器件附近配置緩沖電路,使之形成旁路電路。這樣既可以將線路電感這一引發浪涌的根源降至最低,還可以吸收已經降至最低的線路電感中積蓄的能量。然后,通過對開關器件的電壓進行鉗制,就可以降低關斷浪涌。

*1:“開關轉換器基礎”P95-P107,P95~P107 作者:原田耕介、二宮保、顧文建,出版社:CORONA PUBLISHING CO., LTD. 1992年2月

了解碳化硅功率元器件及其應用案例

介紹了在電源產品的小型化、降低功耗和提高效率方面具有巨大潛力的碳化硅(SiC)的基本物理特性,以及SiC二極管和晶體管的使用方法及其應用案例。

漏極和源極之間產生的浪涌

相關文章一覽

·SiC MOSFET:緩沖電路的設計方法 —前言—

·緩沖電路的種類和選擇

·C緩沖電路的設計

·RC緩沖電路的設計

·放電型RCD緩沖電路的設計

·非放電型RCD緩沖電路的設計

·封裝引起的浪涌差異

· SiC MOSFET:緩沖電路設計方法 —總結—

END?

咨詢或購買產品

掃描二維碼填寫相關信息

將由工作人員與您聯系

點擊閱讀原文 了解更多信息

-

羅姆

+關注

關注

4文章

399瀏覽量

66293

原文標題:R課堂 | 漏極和源極之間產生的浪涌

文章出處:【微信號:羅姆半導體集團,微信公眾號:羅姆半導體集團】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

mos管源極和漏極電流相等嗎

mos管連續漏極電流是什么

mos管漏極電壓增大,為什么溝道變窄

晶體管的漏極與源極有什么區別

MOS管源極和漏極是什么意思

mosfet漏極外接二極管的作用 mosfet源極和漏極的區別

為什么叫源極跟隨器 源極跟隨器的作用和特點

R課堂 | 漏極和源極之間產生的浪涌

R課堂 | 漏極和源極之間產生的浪涌

評論