MicroBlaze CPU 是可修改的拖入式預設 32 位/64 位 RISC 微處理器配置系列。

MicroBlaze 處理器能滿足眾多多樣化的應用程序的不同需求,惠及工業(yè)、醫(yī)療、汽車、消費品和通信市場。MicroBlaze 使用哈佛 (Harvard) 架構(gòu),此架構(gòu)的 PL 內(nèi)通常包含雙 LMB BRAM。但在本篇博文中,我們將探討如何在 Zynq UltraScale ZCU104 開發(fā)板上通過 PSU DDR 執(zhí)行 MicroBlaze 應用。

退出復位時,MicroBlaze 將從 MicroBlaze 配置中的 C_BASE_VECTORS 參數(shù)內(nèi)指定的存儲器地址提取其指令。在本例中,此 C_BASE_VECTORS 將設置為 PSU DDR 內(nèi)的某個區(qū)域。

但根據(jù)采用的啟動流程,這樣可能導致潛在問題,即 PSU DDR 可能無法先于 PL 完成配置。這可能導致 MicroBlaze 掛起。為避免此現(xiàn)象,我們可以使用 MicroBlaze 上的“Reset Mode”(復位模式)信號。

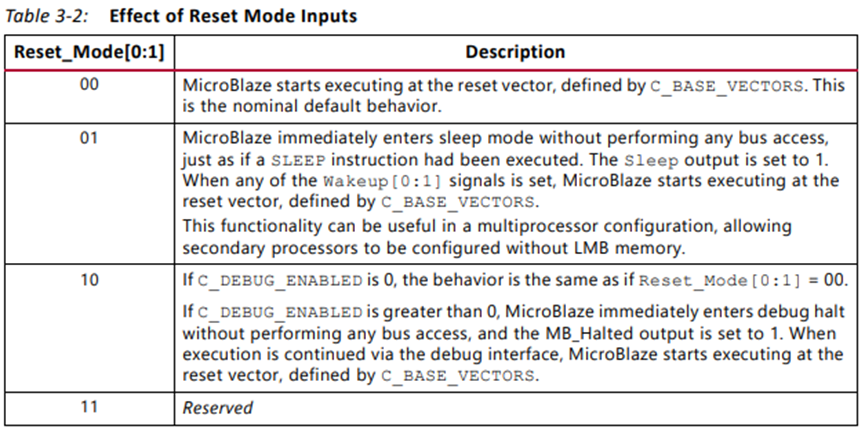

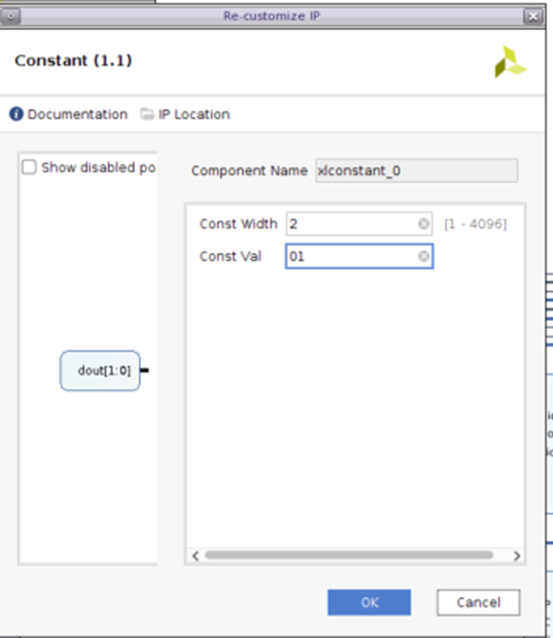

在上表中,可以看到各種 reset_mode 配置。最適合我們的用例的配置為“01”,其中 MicroBlaze 將保持處于復位狀態(tài),直至我們準備就緒為止。我們將在 PSU 上通過 EMIO 來使用 GPIO 對 MicroBlaze 進行解復位。

創(chuàng)建硬件:

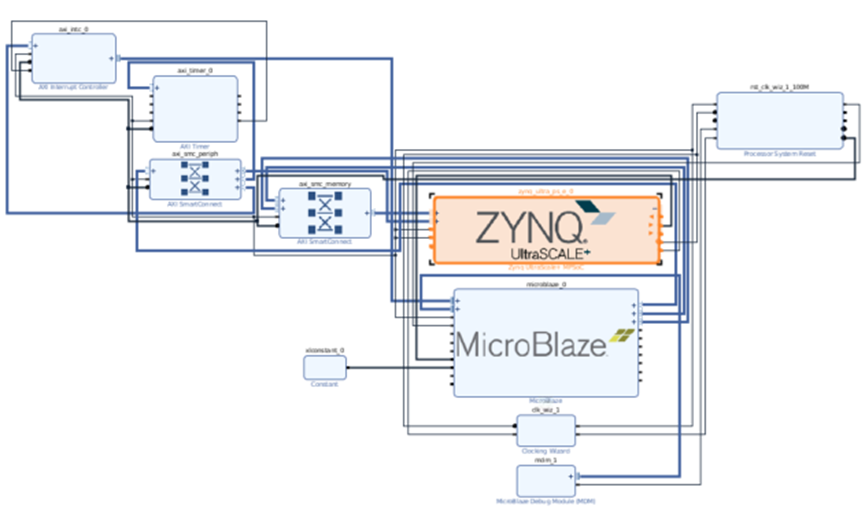

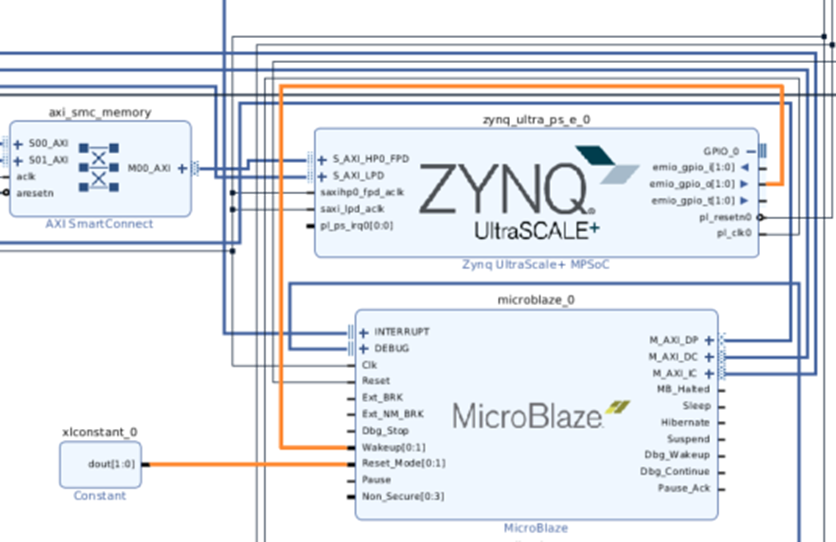

Vivado IP integrator 塊設計如下所示:

用戶可以根據(jù)自己認為合適的方式來自定義設計。

關鍵組件配置如下所述。

MicroBlaze 配置:

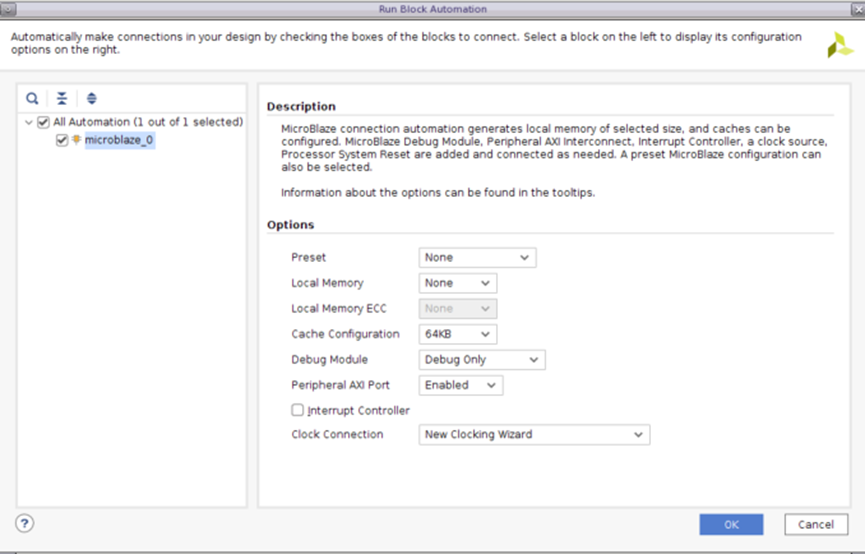

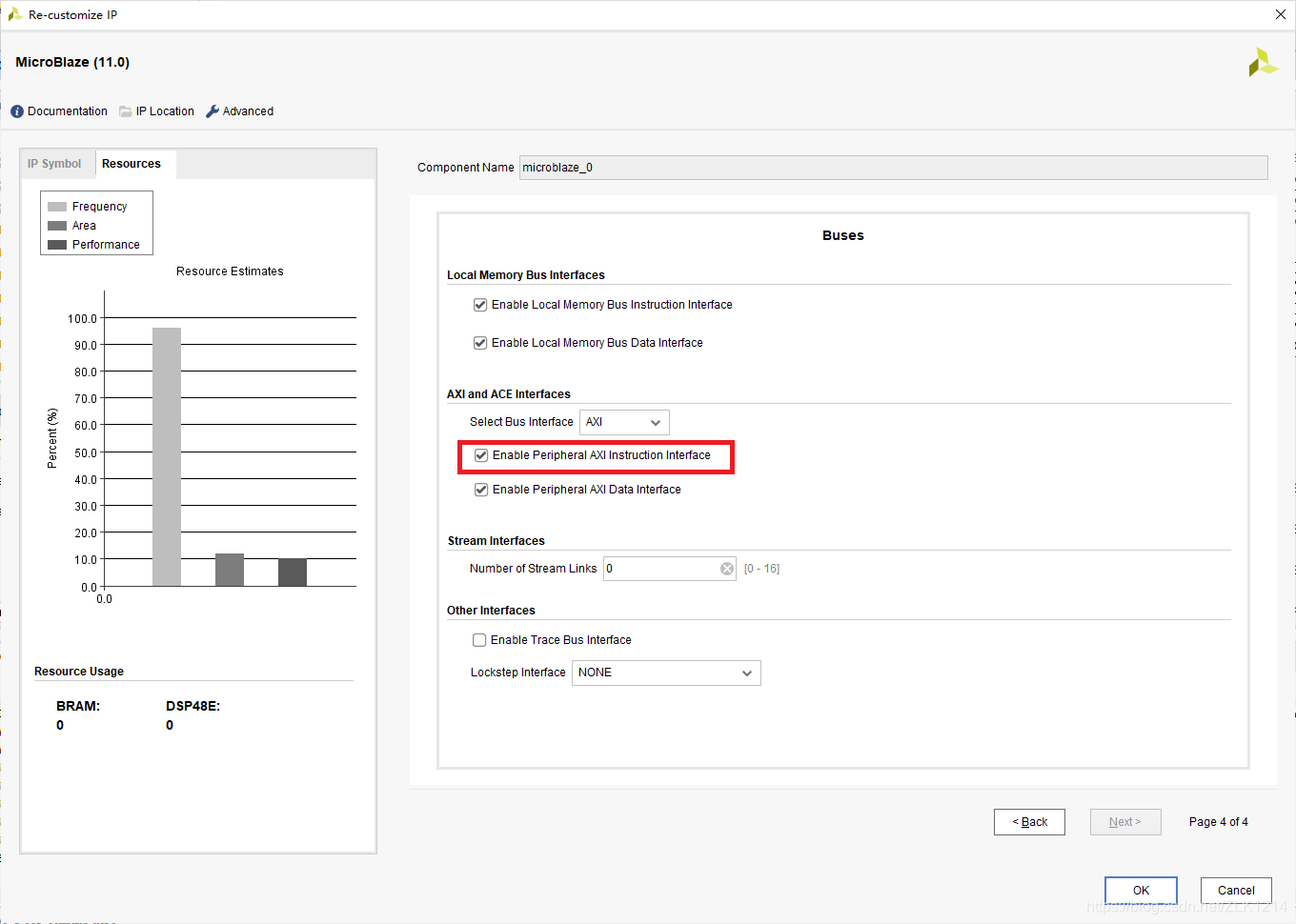

在 Vivado IP integrator 中使用“Block Automation”(塊自動化設置)工具來對 MicroBlaze 進行初始配置,如下所示。此處移除了本地存儲器,改為使用 64K 高速緩存:

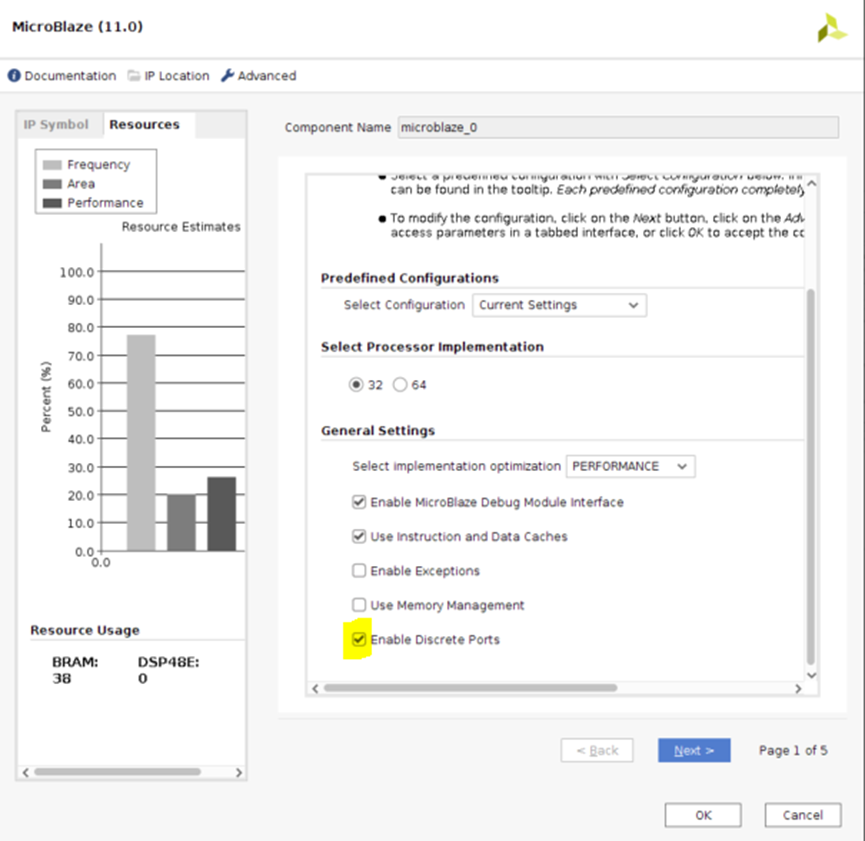

要啟用 reset_mode 和 wakeup 管腳,用戶需在 MicroBlaze 配置中選中“Enable Discrete Ports”以啟用離散端口:

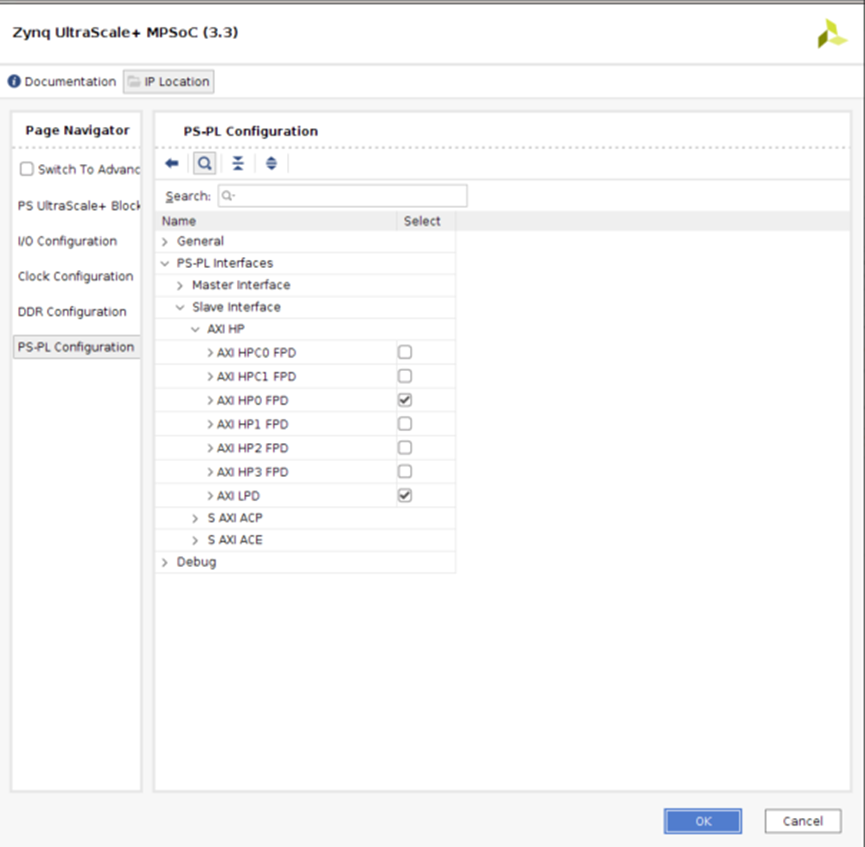

在 Zynq UltraScale PS 配置中,啟用兩個從端口;一個用于存儲器,另一個用于外設:

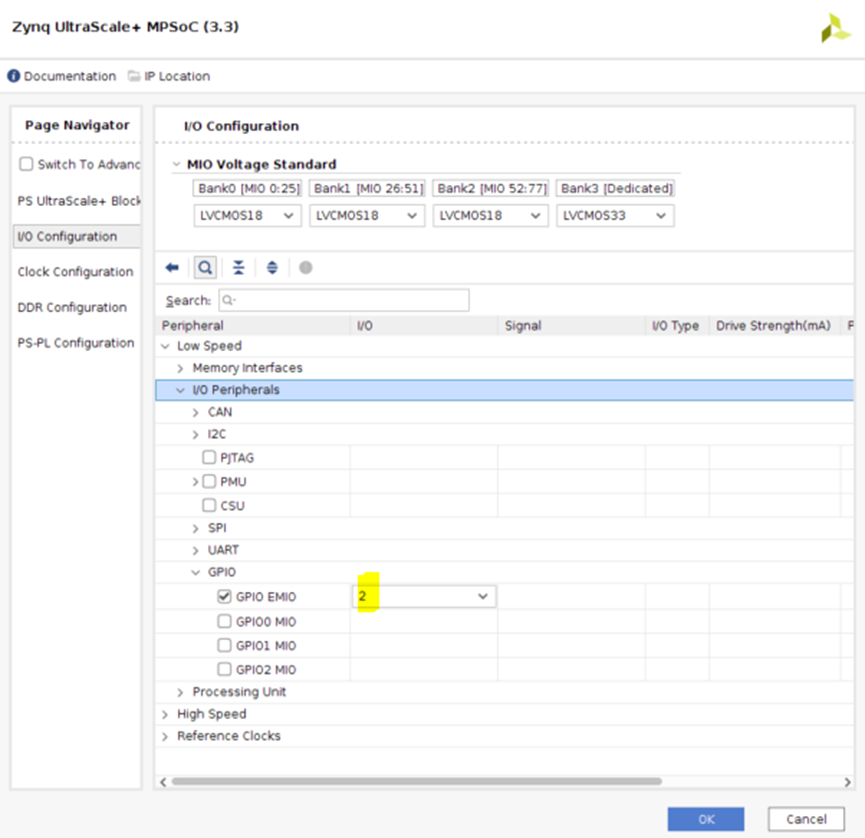

通過 EMIO 啟用 GPIO,這樣就可以控制 MicroBlaze 的 wakeup 管腳:

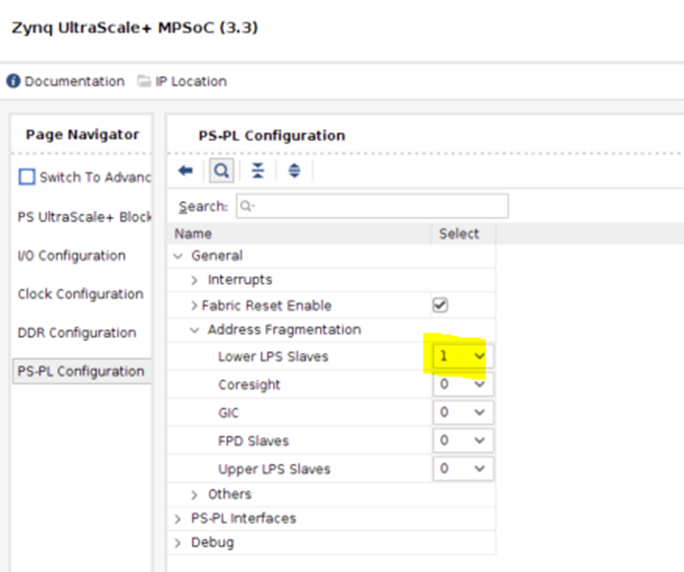

我們還可訪問已從 MicroBlaze 啟用的所有 Zynq UltraScale IP。為此,請啟用“Address Fragmentation”(地址分段):

在上文中我們討論了復位模式。接下來,MicroBlaze 將保持復位狀態(tài),直至我們準備就緒為止。

要使 MicroBlaze 保持復位,可以使用 IP 目錄中的“Constant IP”:

最后,連接 GPIO 和 Constant IP:

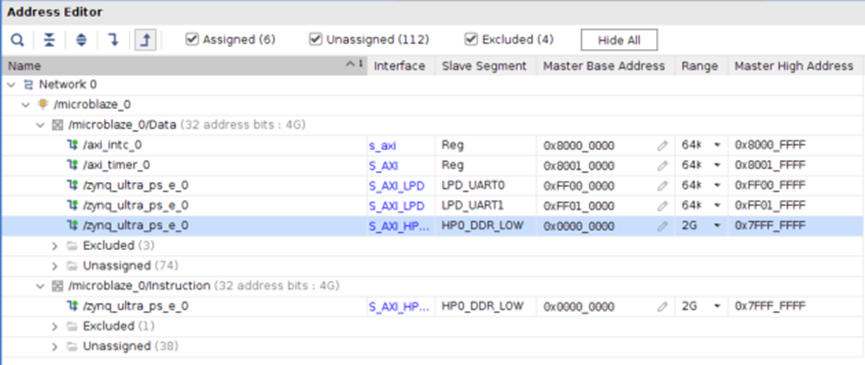

MicroBlaze 地址映射如下所示:

用戶可以右鍵單擊地址段,在地址映射中添加或排除地址段。

此操作適用于硬件配置。我們可以使用“Generate the Output Products”(生成輸出文件)、“Create the HDL wrapper”(創(chuàng)建 HDL 封裝文件)和“Generate the Bitstream”(生成比特流),然后導出硬件。

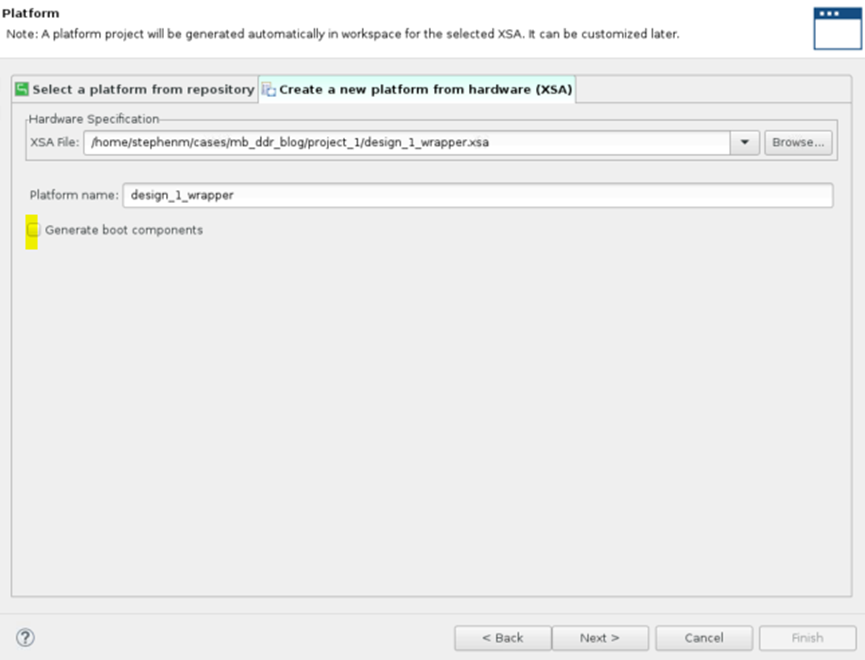

這將生成 XSA 以供在 Vitis 中用于生成我們的軟件。

創(chuàng)建軟件:

Vitis IDE 可用于生成 MicroBlaze 應用。Vitis 還將自動創(chuàng)建啟動鏡像,包括 FSBL 和 PMUFW。

但由于我們想要從 FSBL 控制 GPIO EMIO,因此我們選擇不使用工具來生成啟動鏡像。

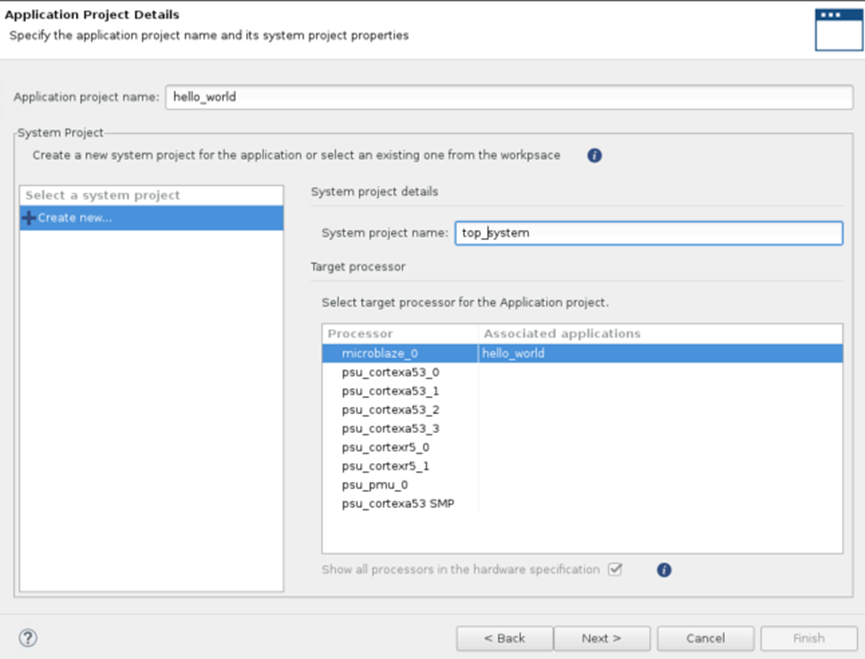

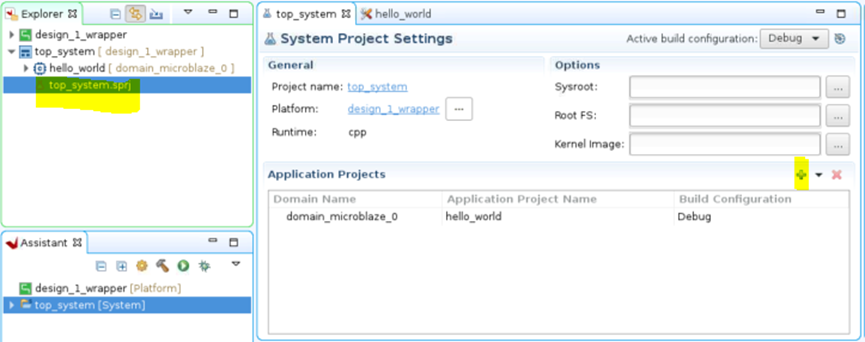

生成 MicroBlaze Hello World 應用:

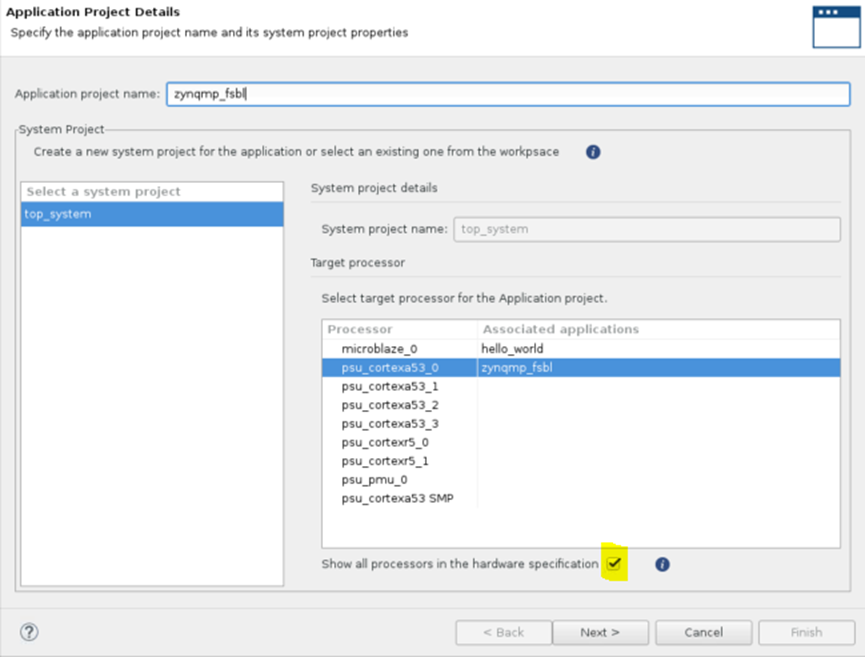

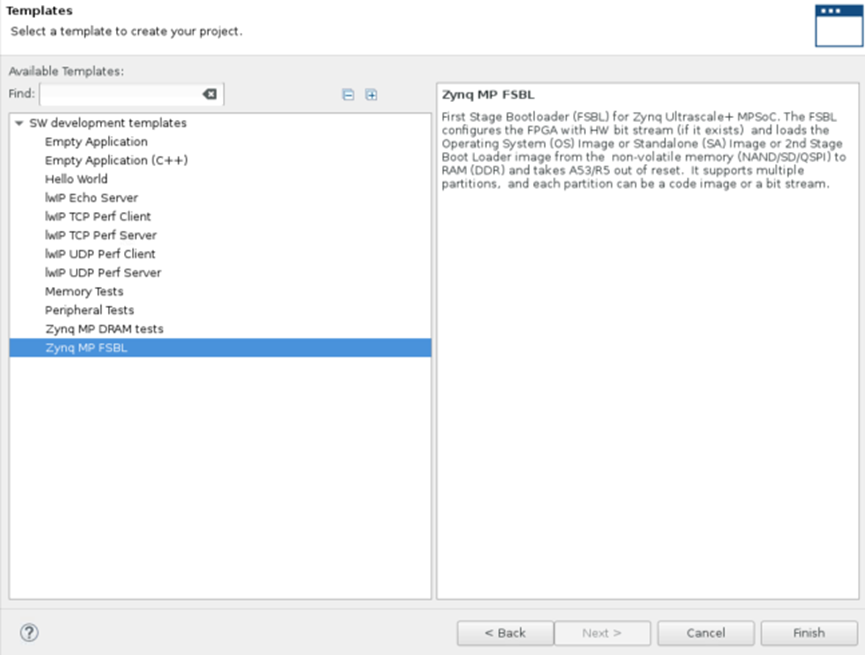

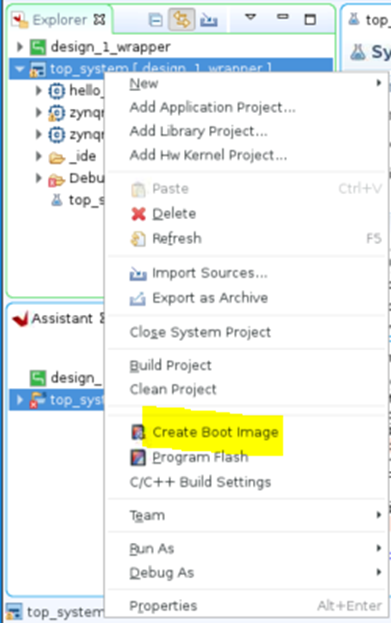

我們可以添加新工程應用,如下所示。例如,對于 Zynq FSBL:

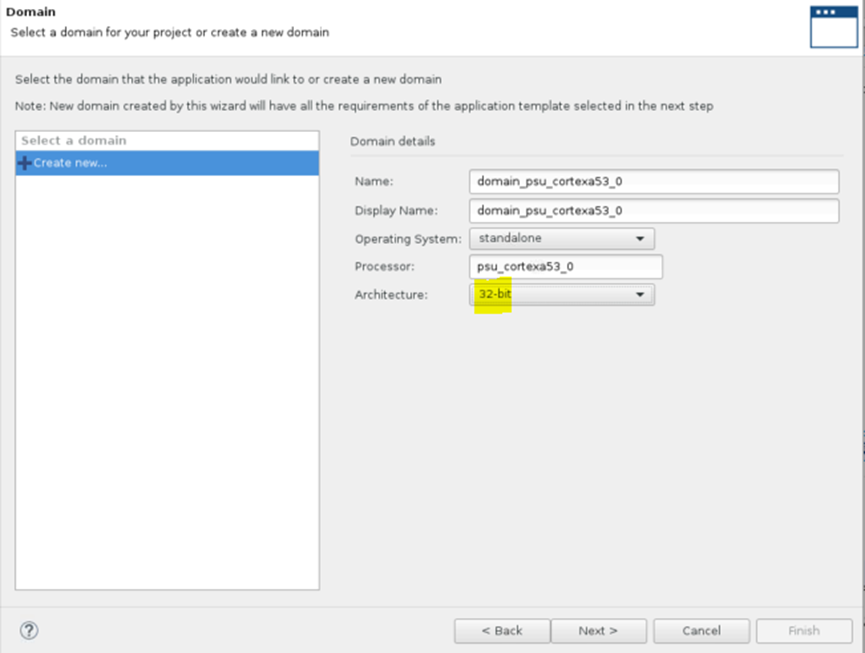

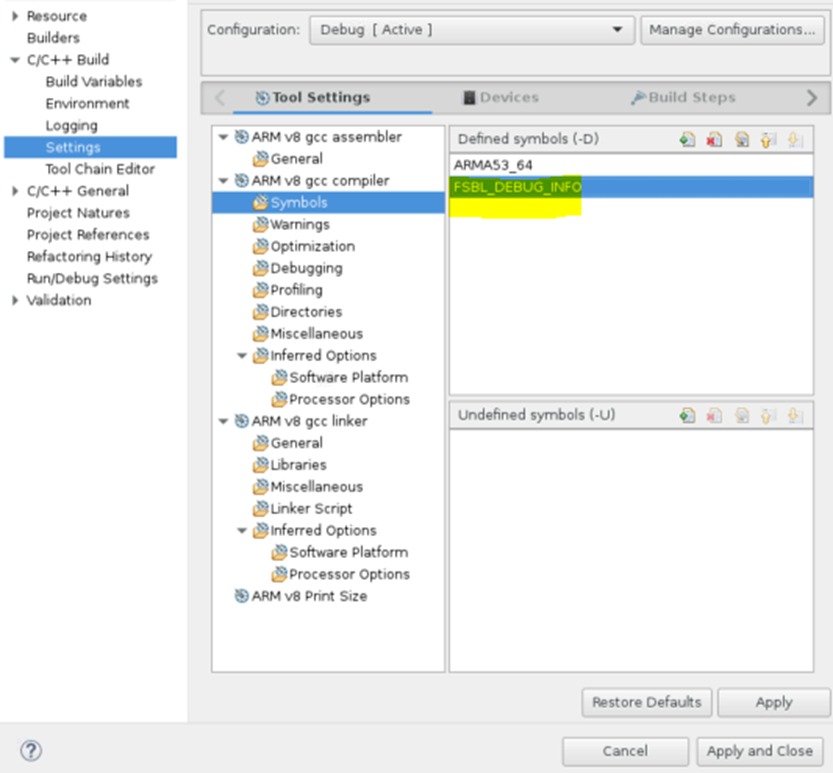

注釋:FSBL 不支持 64 位到 32 位交接。因此,由于 MicroBlaze 為 32 位,我們也應將 FSBL 設置為 32 位。

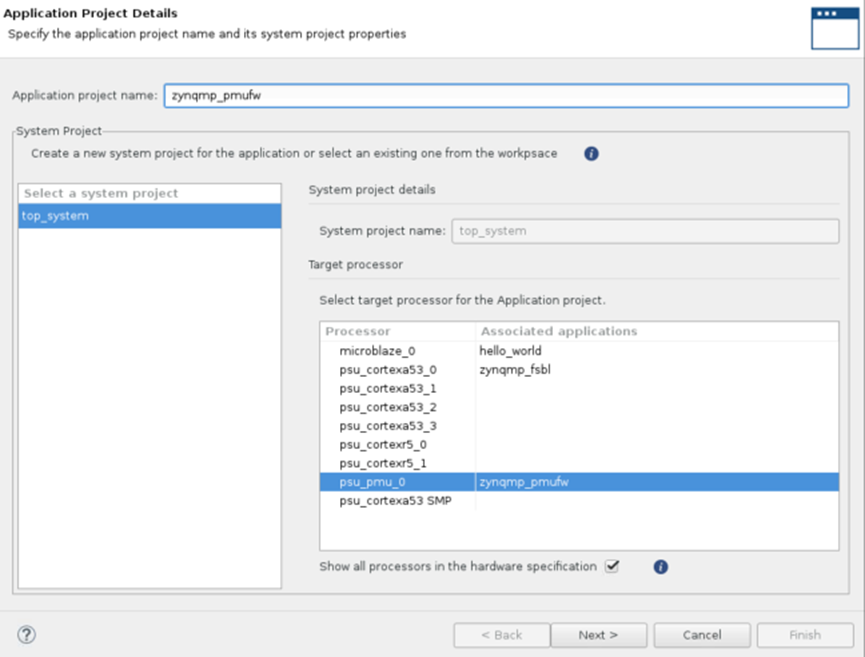

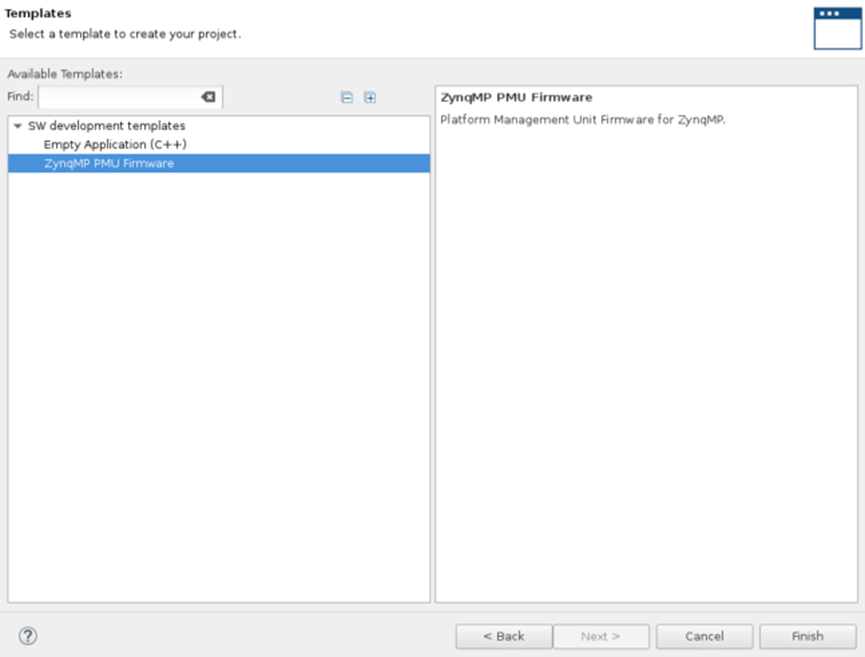

針對 PMUFW 重復上述操作:

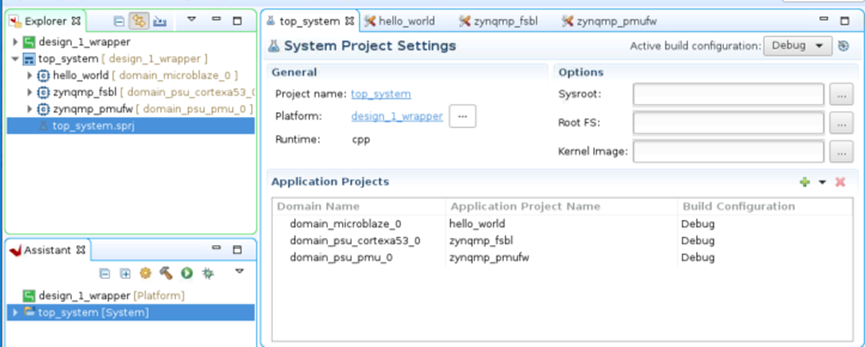

可看到所有應用工程如下所示:

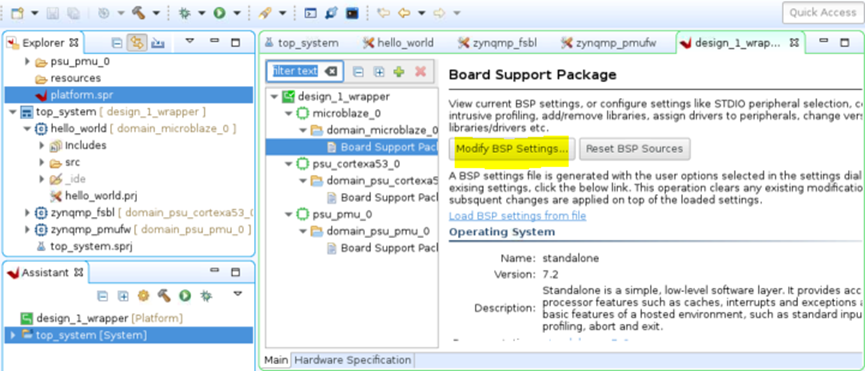

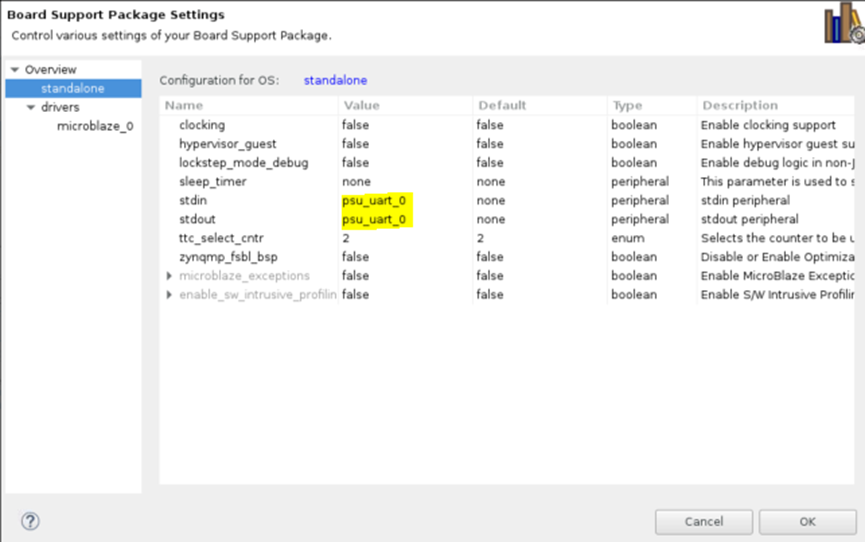

由于我們已將 PS UART 添加到 MicroBlaze 地址映射中,因此可在 BSP 中將其用于 STDIN/OUT。

此處可以看到 MicroBlaze Hello World 連接器:

其布局位置為 DDR 基址 (0x00000000) 處。用戶創(chuàng)建啟動鏡像時,需牢記此地址,以免應用程序發(fā)生重疊。

首先,更新 FSBL。

我們可以使用 Xil_Out32 API 來切換 GPIO。

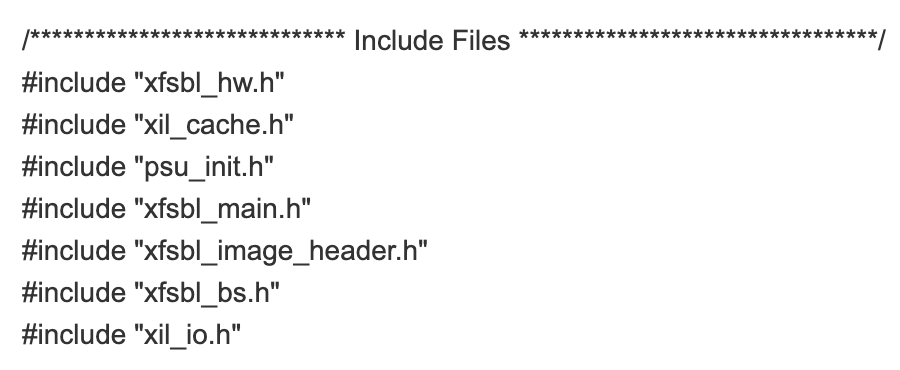

將 xil_io 頭文件添加到 xfsbl_handoff.c 文件:

將此添加到 XFsbl_HandoffExit 函數(shù)

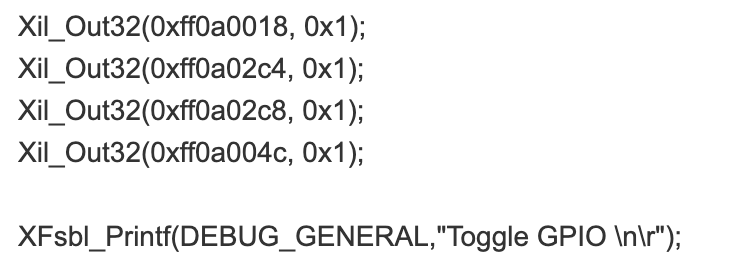

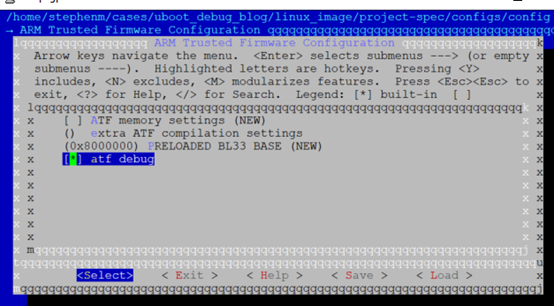

同時啟用 FSBL 調(diào)試信息:

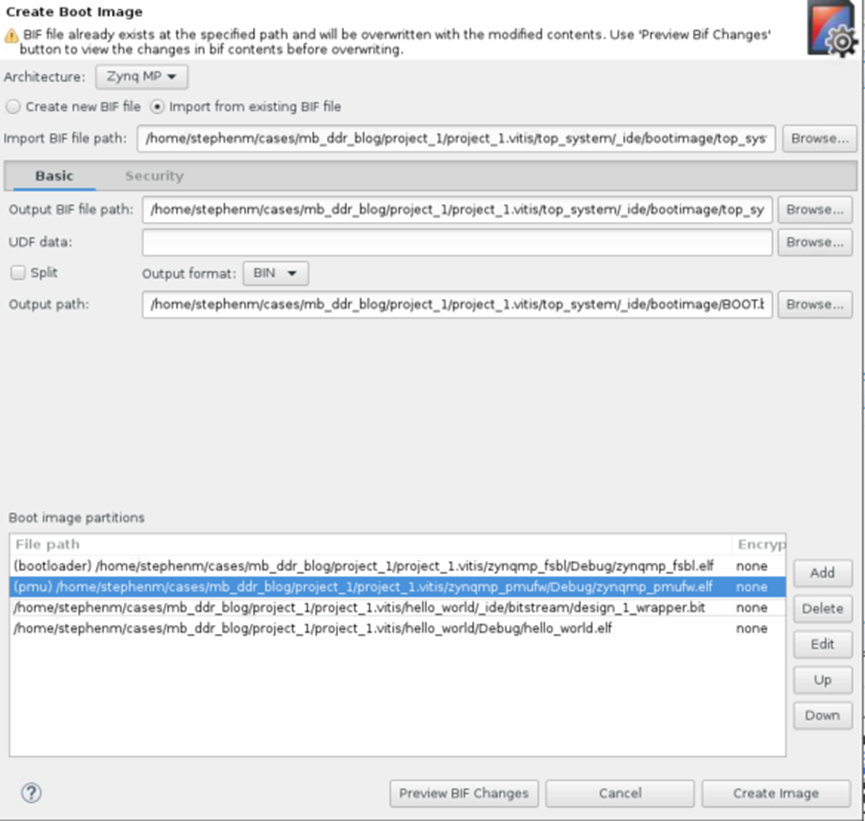

創(chuàng)建啟動鏡像:

移除 FSBL 和 PMUFW,并使用正確的鏡像類型重新添加。

請確保分區(qū)鏡像順序正確(使用上下控件來調(diào)整其順序)。

注釋:由于此處共享相同 UART,用戶可以在 Hello World 應用中布局延遲。

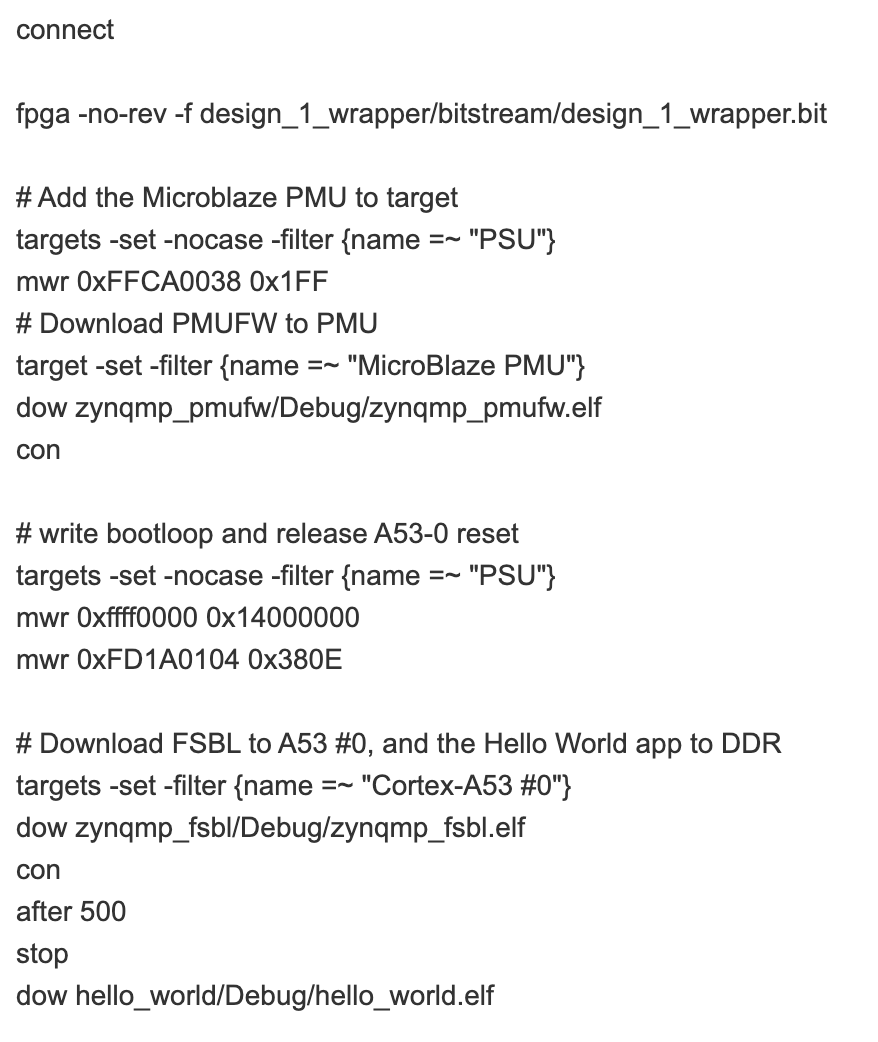

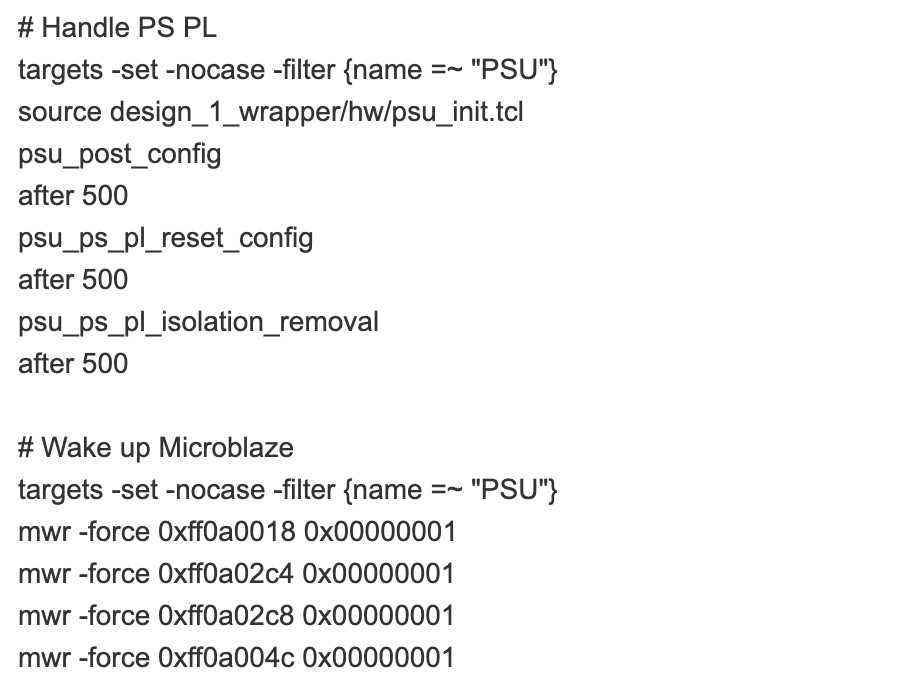

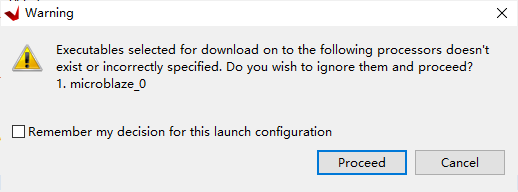

通過 JTAG 進行編程:

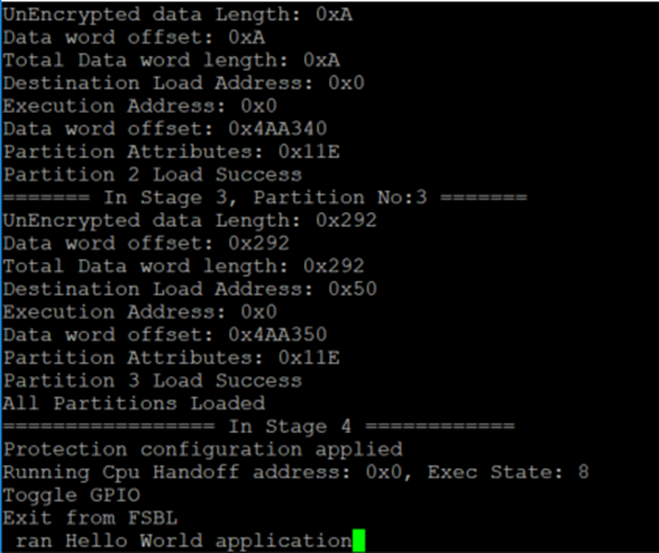

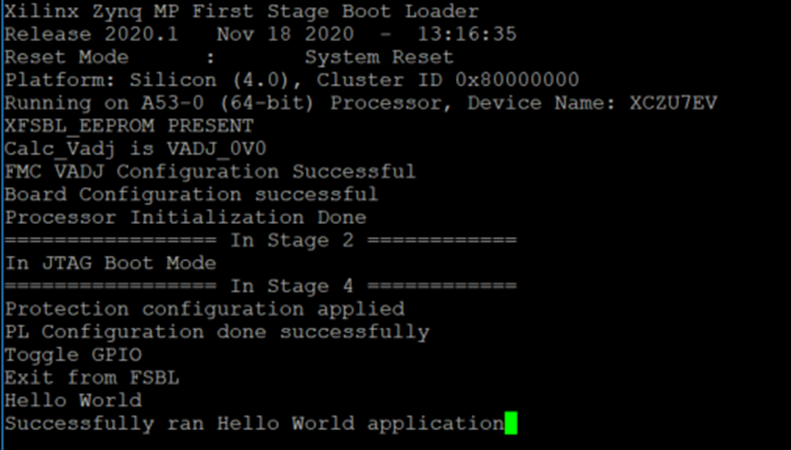

這樣可看到如下輸出:

審核編輯:湯梓紅

-

cpu

+關注

關注

68文章

10826瀏覽量

211162 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121015 -

微處理器

+關注

關注

11文章

2247瀏覽量

82324 -

RISC

+關注

關注

6文章

461瀏覽量

83656 -

Vitis

+關注

關注

0文章

145瀏覽量

7405

原文標題:開發(fā)者分享|在Vitis中通過 PSU DDR 執(zhí)行 MicroBlaze 應用

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

MicroBlaze串口設計

Vitis2023.2使用之—— updata to Vitis Unified IDE

vivado下外部邏輯和MicroBlaze交換數(shù)據(jù)

DDR3 SDRAM的簡單代碼如何編寫

使用Vitis 在EBAZ4205(ZYNQ)礦機上實現(xiàn)"Hello World!"

請問如何通過MicroBlaze訪問BRAM?

【正點原子FPGA連載】第一章MicroBlaze簡介--摘自【正點原子】達芬奇之Microblaze 開發(fā)指南

使用Vitis HLS創(chuàng)建屬于自己的IP相關資料分享

PYNQ中MicroBlaze程序文件的加載過程

怎么在Vitis中設定Kernel的頻率?

Xilinx Vitis 2020.1里面MicroBlaze軟核的sleep函數(shù)卡死的問題

在Vitis中調(diào)試ARM可信固件和U-boot

UCC25640X在LED照明PSU中的優(yōu)勢

在Vitis中通過PSU DDR執(zhí)行MicroBlaze應用

在Vitis中通過PSU DDR執(zhí)行MicroBlaze應用

評論