IP核配置

定制輸出數據位寬

這里的輸出數據指的是輸出的波形數據,其位寬相關參數介紹如下:

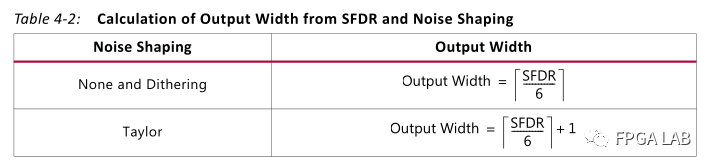

可見,輸出數據寬度和SFDR以及Noise Shaping有關,你可先不必知道Noise Shaping和SFDR是什么?只需要暫時知道在IP核定制時需要選擇即可,如果Noise Shaping選擇了None and Dithering,則輸出數據寬度為:

如果為Taylor:

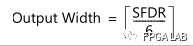

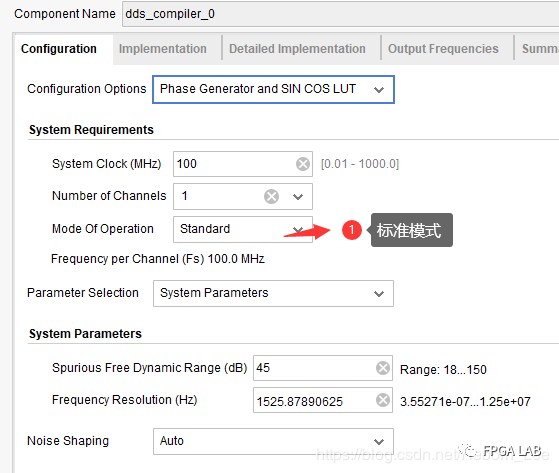

而Spurious Free Dynamic Range (SFDR)翻譯為無雜散動態范圍,和輸出數據寬度以內部總線寬度以及各種實現策略有關;假設我需求的數據寬度為10位,Noise Shaping選為None,則SFDR為60,輸入IP定制頁面:

查看輸出是否為10bit:

定制相位位寬(或頻率分辨率)

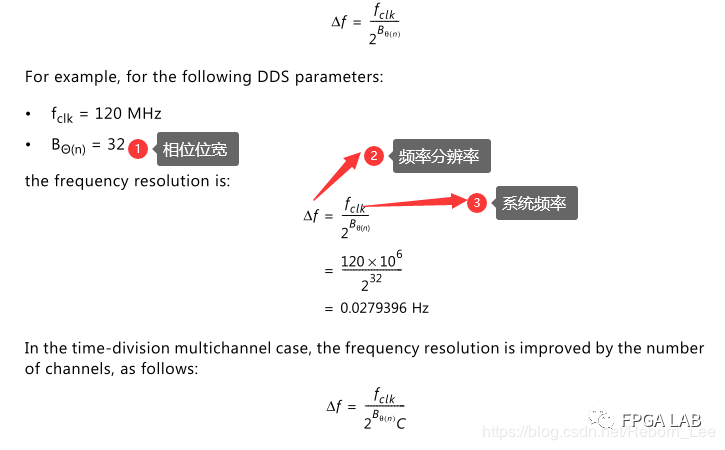

根據數據手冊對頻率分辨率的描述:

頻率分辨率:以赫茲為單位指定,指定最小頻率分辨率,用于確定相位累加器使用的相位寬度及其相關的相位增量(PINC)和相位偏移(POFF)值。較小的值可提供較高的頻率分辨率,并且需要較大的累加器。較大的值會減少硬件資源。根據噪聲整形的選擇,可以增加相位寬度,并且頻率分辨率高于指定的分辨率。

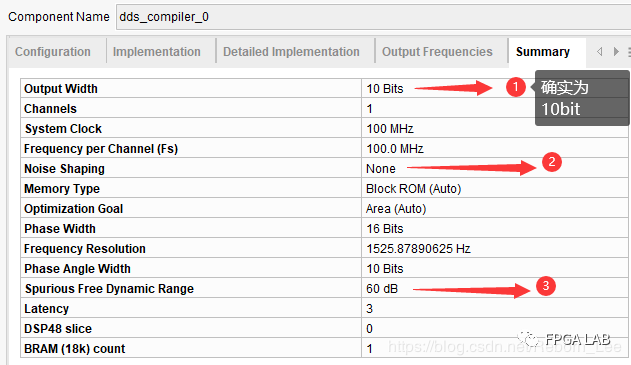

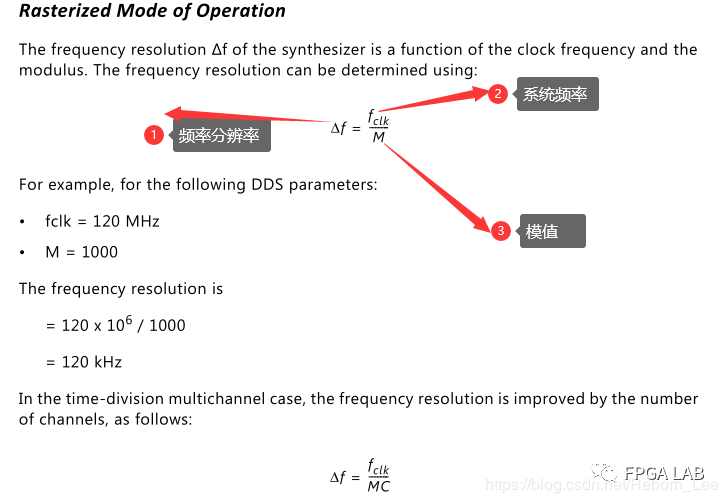

對于光柵化模式(rasterized mode),頻率分辨率由系統時鐘、通道數和所選模數固定。從這段描述,我們得出信息,頻率分辨率可以用來控制相位位寬。如果操作模式選擇標準模式,如下IP 核定制頁面:

頻率分辨率可以這樣計算:

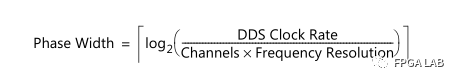

我們先給定需求的相位寬度,又已知系統頻率值,根據公式就可以算出頻率分辨率;將頻率分辨率代入IP核定制頁面,即可自動得到相位寬度。 其實從上式也可以直接推出相位寬度:

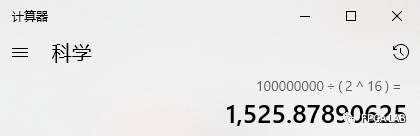

本例我們的系統頻率為100MHz,如果想要相位寬度為16位,則頻率 分辨率為:

在IP核定制頁面,如下圖,我們輸入頻率分辨率的值:

查看相位寬度為16位:

上面選擇的是標準模式,如果選擇另一種模式呢?Rasterized Mode of Operation:光柵化操作模式;我們可以根據下面公式得到頻率分辨率, 但和相位寬度沒有直接關系 ,為了知識完整性,簡介如下:

在IP核定制頁面提現如下:

輸出頻率

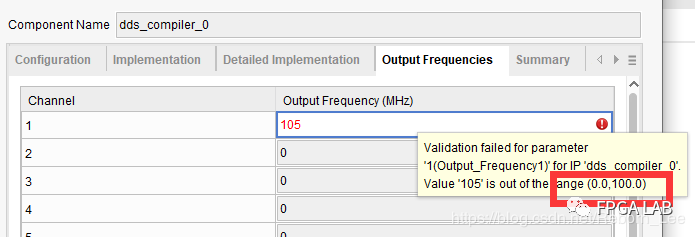

本示例選擇的是單通道,也即通道數為1,因此輸出頻率也只能選擇一個:

輸出頻率值也不是隨便選擇的,而是有其范圍的,例如我輸入105MHz,則通過不了:

提示超出范圍,范圍為(0,100).

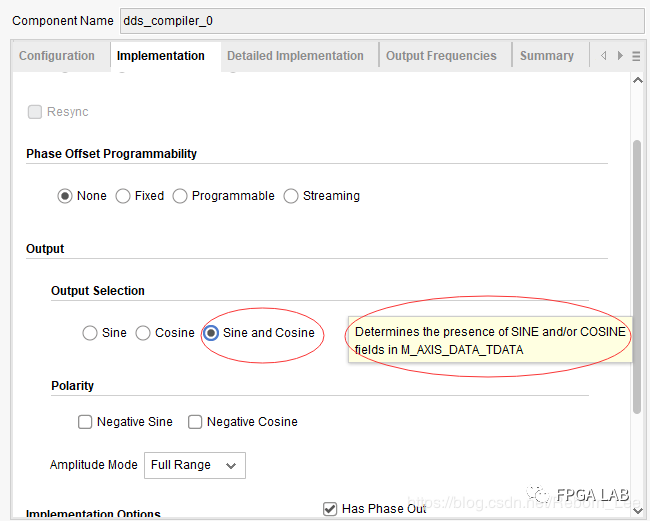

輸出正余弦選擇以及數據格式

可以在IP核定制頁面選擇輸出正弦還是余弦還或者是都輸出:

本示例選擇輸出正余弦,由于輸出采用的是axi總線,因此輸出數據位于M_AXIS_DATA_TDATA中,那么正余弦輸出結果是如何組合成M_AXIS_DATA_TDATA的呢?

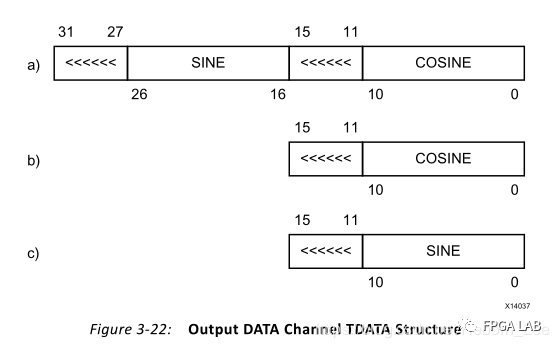

數據手冊給出解釋:

輸出DATA通道TDATA結構將正弦和余弦輸出字段符號擴展到下一個字節邊界,然后以最低有效部分的余弦進行連接,以創建m_axis_data_tdata。如果僅選擇正弦或余弦之一,則將其符號擴展并放入m_axis_data_tdata的最低有效部分。

下圖顯示了這三種配置的TDATA的內部結構。正交輸出,僅余弦和僅正弦。例如,在圖中顯示了11位輸出,符號擴展到16位。<<<表示符號擴展名:

因此我們可以這么認為,由于存在擴展符號位的關系,我們可以提取低一半的數據為COS,高一半的數據未SIN。

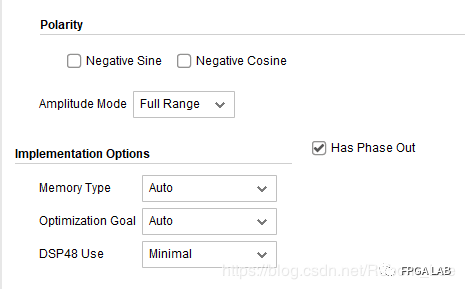

其他設置

有了上面的定制參數,輸出波形是沒有問題了,至于其他的定制參數,本文選擇默認:

點擊OK,等待IP核定制完成。

電路設計

本示例設計十分簡單,就是單純例化下IP核:

復制例化模板:

給出設計文件:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: Reborn Lee

// Module Name: waveform_gen

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: Reborn Lee

// Module Name: waveform_gen

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module waveform_gen(

input i_clk,

output o_data_valid,

output [31 : 0] o_data,

output o_phase_valid,

output [15 : 0] o_phase

);

dds_compiler_0 inst_dds (

.aclk(i_clk), // input wire aclk

.m_axis_data_tvalid(o_data_valid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(o_data), // output wire [31 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(o_phase_valid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(o_phase) // output wire [15 : 0] m_axis_phase_tdata

);

endmodule

求一種基于DDS IP核的任意波形發生器設計方案

求一種基于DDS IP核的任意波形發生器設計方案