在FPGA開發(fā)過程中不可避免的要使用到一些IP,有些IP是很復(fù)雜的,且指導(dǎo)手冊(cè)一般是很長(zhǎng)的英文,僅靠看手冊(cè)和網(wǎng)絡(luò)的一些搜索,對(duì)于復(fù)雜IP的應(yīng)用可能一籌莫展。

這里以Xilinx為例,在Vivado中使用SRIO高速串行協(xié)議的IP演示如何使用官方例程和手冊(cè)進(jìn)行快速使用,在仔細(xì)閱讀參考官方例程后進(jìn)行一些修改就可以應(yīng)用在實(shí)際項(xiàng)目中。

1.導(dǎo)入IP

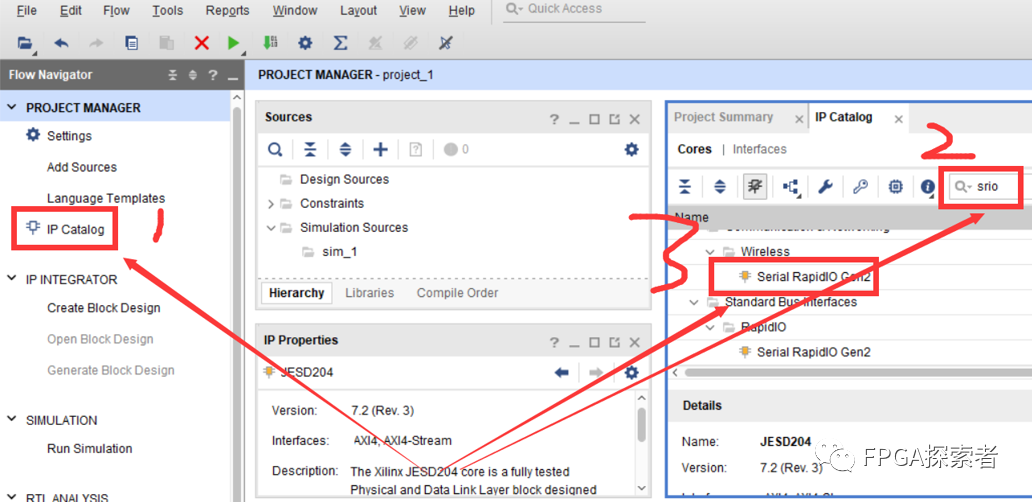

點(diǎn)擊“IP Catalog”,選擇要使用的IP,雙擊3處配置IP。

2.配置IP

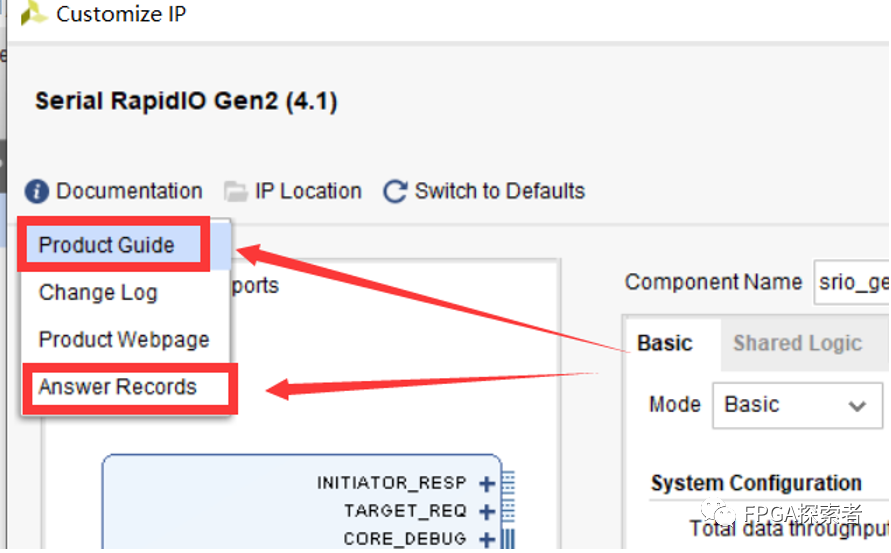

點(diǎn)擊左上角可以閱讀官方的IP說明手冊(cè)、IP更新信息、常見問題及解決方式。根據(jù)實(shí)際的需求配置IP的參數(shù),如工作時(shí)鐘等。

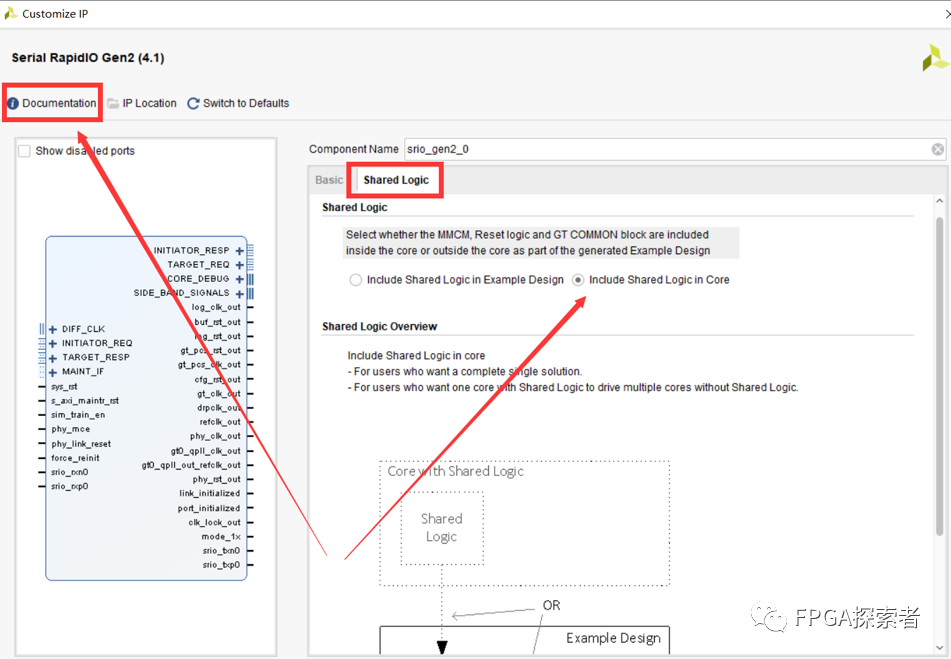

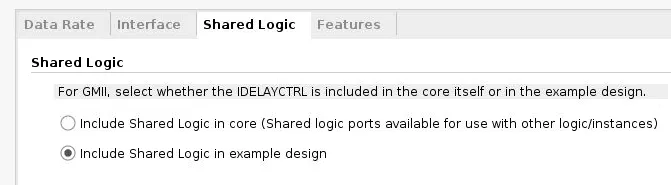

在“Shared Logic”選項(xiàng)中(SRIO、Aurora、JESD204等使用GT的IP核中常常有此選項(xiàng)),如果選擇“ Include Shared Logic inExample Design ” (推薦方式) ,則在IP核外部的示例工程中生成時(shí)鐘、復(fù)位等必要邏輯,且這些邏輯作為共享邏輯,加入使用 多個(gè)IP核時(shí),可以共享一些復(fù)位等信號(hào) , 且這些時(shí)鐘、復(fù)位可以被使用者修改 ;

當(dāng)選中“ Include Shared Logic in Core **”****(簡(jiǎn)單)**選項(xiàng)時(shí),時(shí)鐘、復(fù)位邏輯等邏輯被包含在IP核中, 對(duì)其他的IP不可見 , 這些邏輯也不能被修改(Read-Only) 。

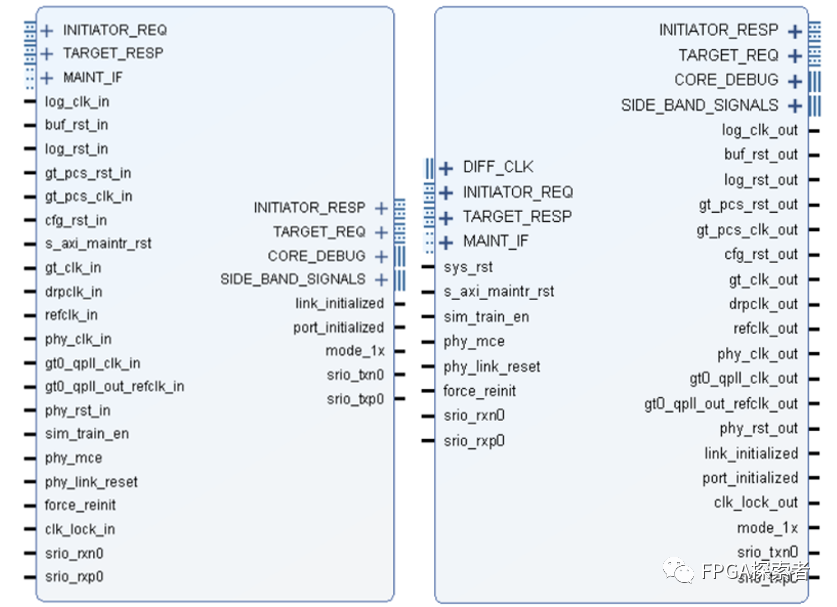

下圖中左邊是“ IncludeShared Logic in Example Design ”,右邊是“ Include Shared Logic in Core ”,可見不同配置下IP對(duì)外呈現(xiàn)的時(shí)鐘、復(fù)位和GT的一些引腳是不同的。

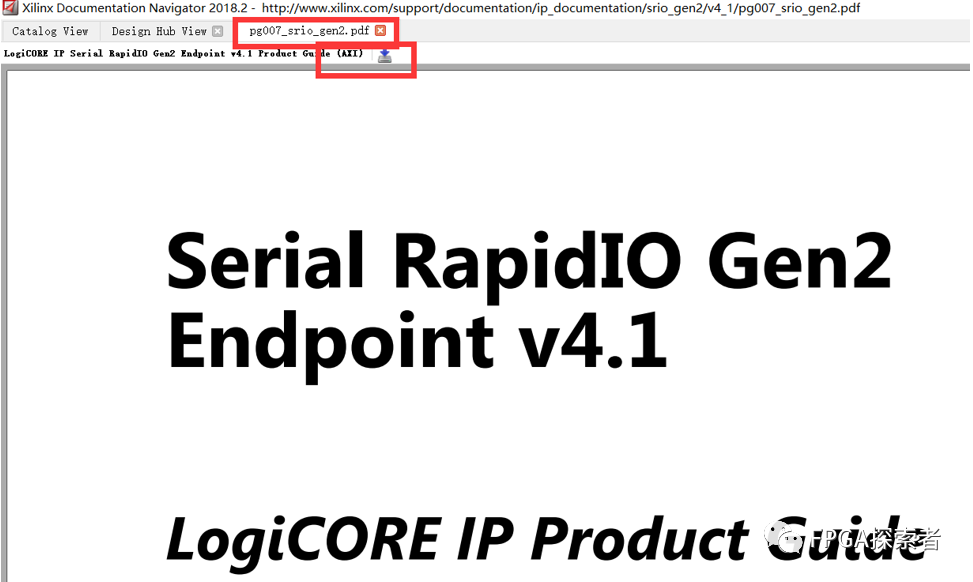

3.閱讀手冊(cè)

點(diǎn)擊“Product Guide”可以轉(zhuǎn)到Xilinx的DocNav中,查看、閱讀、下載各FPGA器件手冊(cè)、開發(fā)板資料、IP手冊(cè)。 Xilinx官方手冊(cè)和配套例程是最具參考價(jià)值的資料 ,沒有其他。雖然是英文版,但是借助翻譯軟件及關(guān)鍵詞查找,還是能夠進(jìn)行閱讀。

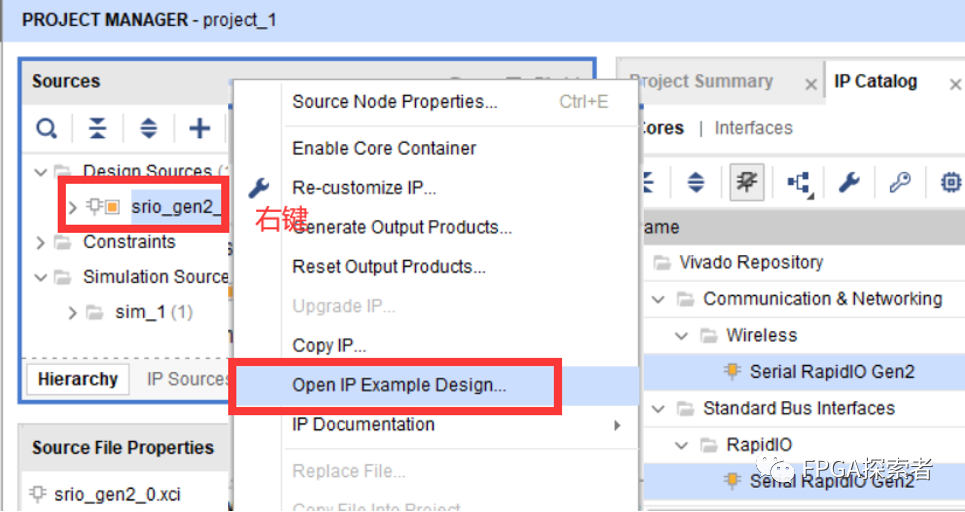

4.生成例程

選擇OOC編譯,等編譯完成后,右鍵“ Open IPExample Design ”,打開IP對(duì)應(yīng)配置下的測(cè)試工程,選擇指定路徑,自動(dòng)打開新生成的測(cè)試工程。

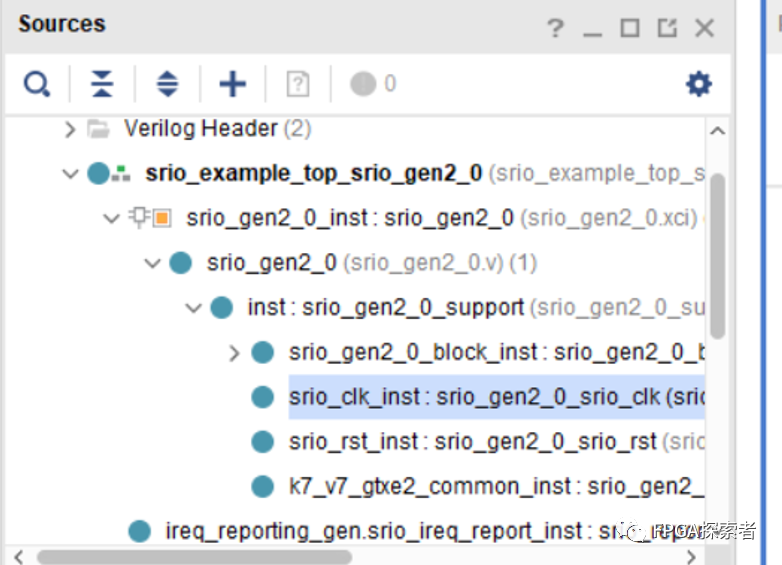

5.閱讀示例工程,仿真分析

工程中包含了 時(shí)鐘 、復(fù)位及 輸入輸出 、AXI總線協(xié)議等必要的配置,包含 TestBench仿真測(cè)試文件 ,閱讀分析源碼,仿真查看波形,通過少量更改可以下板測(cè)試,ILA監(jiān)測(cè),參考示例工程,在實(shí)際應(yīng)用中即可使用。

選擇“ Include Shared Logic inExample Design ” (推薦方式) ,則在IP核外部的示例工程中生成時(shí)鐘、復(fù)位等必要邏輯,且這些邏輯作為共享邏輯,加入使用 多個(gè)IP核時(shí),可以共享一些復(fù)位等信號(hào) , 且這些時(shí)鐘、復(fù)位可以被使用者修改 ;

選中“ Include Shared Logic in Core **” **(簡(jiǎn)單)選項(xiàng)時(shí),時(shí)鐘、復(fù)位、GT收發(fā)器配置是包含在IP核內(nèi)部, 對(duì)其他的IP不可見 ,這些邏輯也不能被修改(Read-Only) ,不對(duì)外呈現(xiàn)。

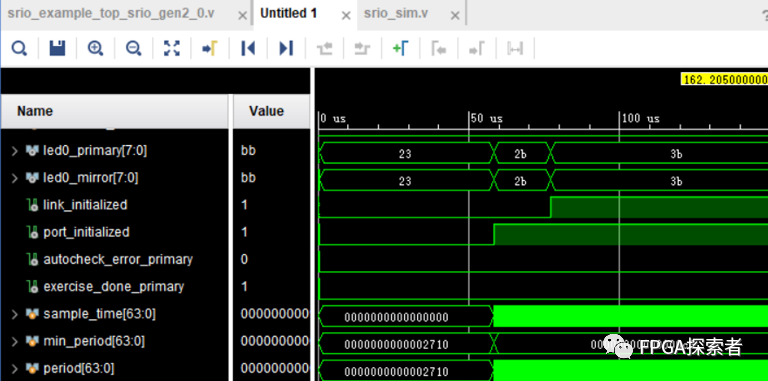

運(yùn)行仿真即可查看波形,,可以分析內(nèi)部的信號(hào),包括物理層PHY、協(xié)議層LOG等多個(gè)信號(hào)。

其余 IP 類似使用,多閱讀官方的IP手冊(cè)和例程。

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3338瀏覽量

105542 -

sRIO

+關(guān)注

關(guān)注

1文章

30瀏覽量

20913 -

PHY

+關(guān)注

關(guān)注

2文章

296瀏覽量

51555 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14215 -

FPGA開發(fā)板

+關(guān)注

關(guān)注

10文章

120瀏覽量

31427

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Vivado IP中的Shared Logic到底是干嘛的

基于FPGA的通用高速串行互連協(xié)議設(shè)計(jì)

使用ZYBO板在VIVADO中使用AXI4 BFM仿真接口創(chuàng)建外設(shè)IP時(shí)收到錯(cuò)誤消息

Vivado環(huán)境下如何在IP Integrator中正確使用HLS IP

如何了解SRIO IP核三層協(xié)議的作用?

如何導(dǎo)出IP以供在Vivado Design Suite中使用?

基于VIVADO的PCIE IP的使用

如何導(dǎo)出IP以供在 Vivado Design Suite 中使用

在FPGA和DSP兩種處理器之間實(shí)現(xiàn)SRIO協(xié)議的方法

SRIO IP核的三層協(xié)議的作用解析

在Vivado中使用SRIO高速串行協(xié)議的IP演示

在Vivado中使用SRIO高速串行協(xié)議的IP演示

評(píng)論