8

存儲器

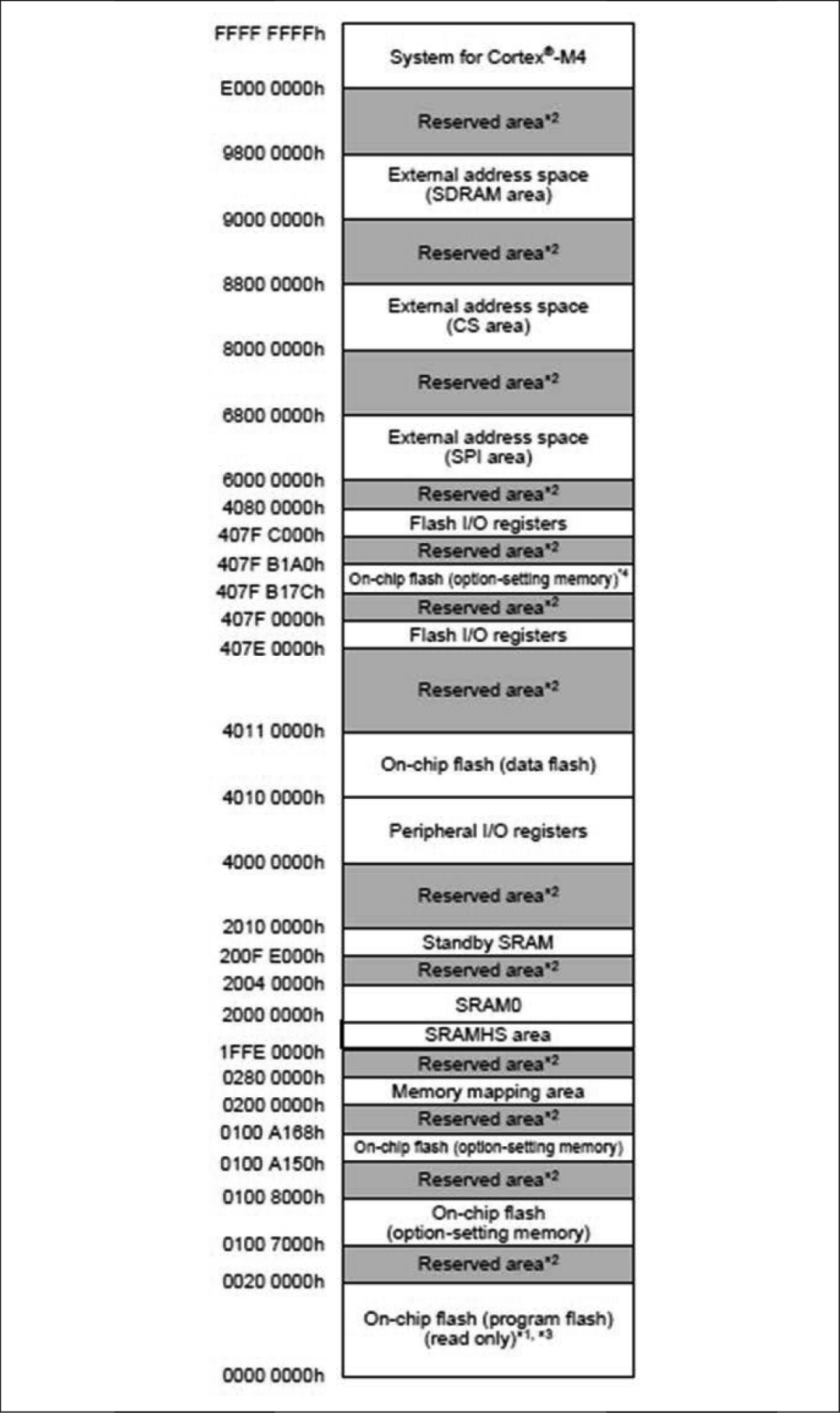

RA6 MCU支持4GB的線性地址空間,范圍為0000 0000h到FFFF FFFFh,其中包含程序、數(shù)據(jù)和外部存儲器總線。該系列的某些產(chǎn)品包括一個SDRAM控制器,可利用該控制器訪問連接到外部存儲器總線的SDRAM器件。程序和數(shù)據(jù)存儲器共用地址空間;使用單獨的總線分別訪問這兩個存儲器,從而提高性能并允許在同一個周期訪問程序和數(shù)據(jù)。存儲器映射中包含片上RAM、外設(shè)I/O寄存器、程序ROM、數(shù)據(jù)閃存和外部存儲器區(qū)域。

圖16. RA6M3存儲器映射

8.1 SRAM

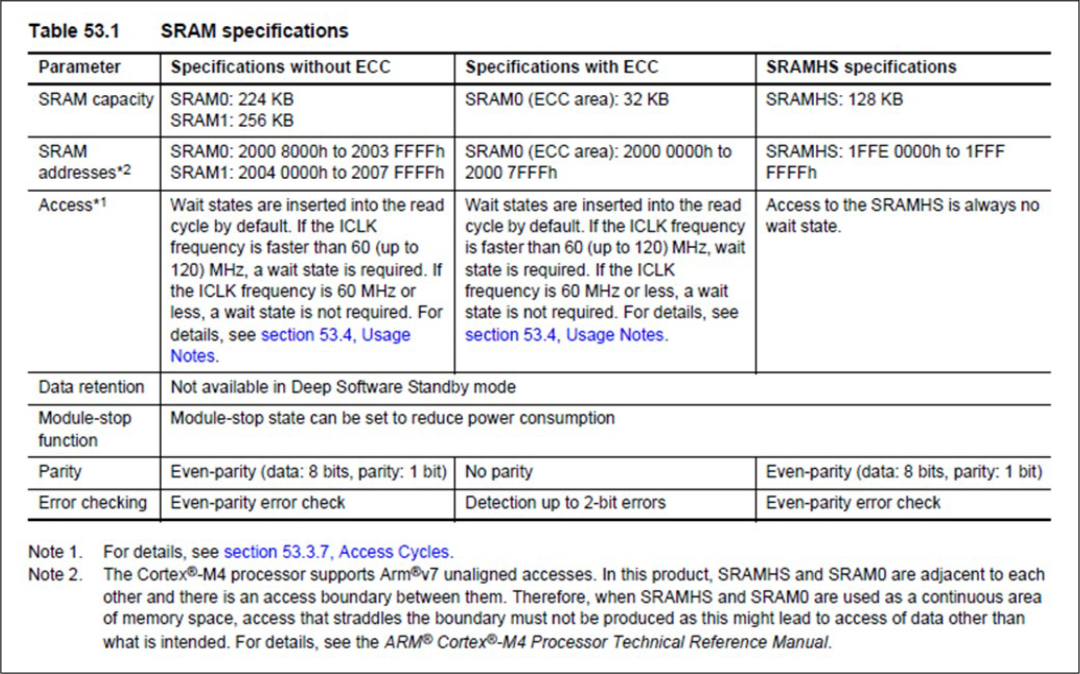

RA6 MCU提供帶奇偶校驗位或ECC(糾錯碼)的片上高速SRAM模塊。SRAM0的前32KB區(qū)域受ECC控制。奇偶校驗在其他區(qū)域執(zhí)行。下表列出了SRAM規(guī)范。SRAM模塊的數(shù)量和容量因器件而異。有關(guān)詳細(xì)信息,請參見《硬件用戶手冊》。

圖17. RA6M3 SRAM規(guī)范示例

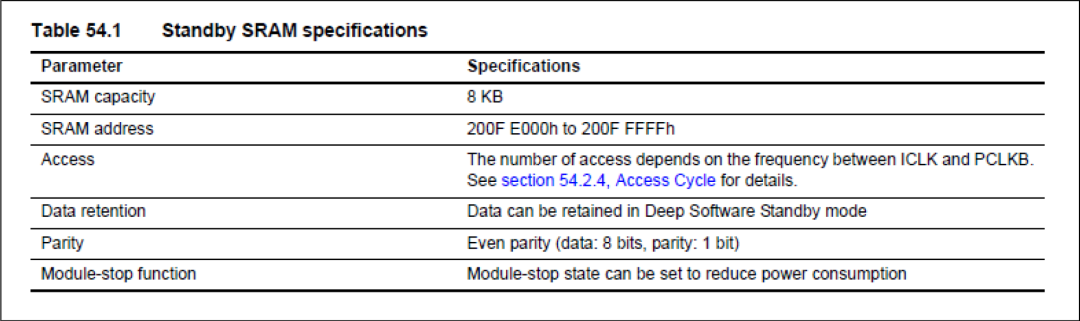

8.2 待機(jī)SRAM

RA6 MCU提供了一個片上SRAM,支持在深度軟件待機(jī)模式下保留數(shù)據(jù)。下表列出了備用SRAM規(guī)范。

在深度軟件待機(jī)模式下,待機(jī)SRAM的電源由DPSBYCR.DEEPCUT[1:0]位使能。如果DPSBYCR.DEEPCUT[1:0]位設(shè)置為00b,則將在深度軟件待機(jī)模式下保留待機(jī)SRAM中的數(shù)據(jù)。有關(guān)DPSBYCR.DEEPCUT[1:0]位的詳細(xì)信息,請參見后文第11節(jié)“低功耗模式”。

圖18. RA6M3待機(jī)SRAM規(guī)范示例

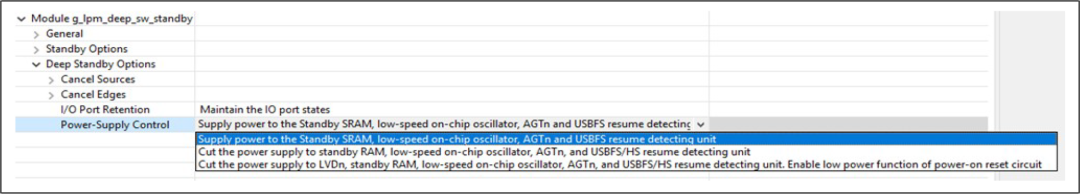

Renesas FSP中的LPM(低功耗模式)驅(qū)動程序提供了一個用于切斷或保持待機(jī)SRAM電源的選項,如下圖所示。仍然需要調(diào)用LPM驅(qū)動程序的API才能將所選設(shè)置寫入MCU寄存器。

圖19. 使用Renesas FSP配置器使能/禁用待機(jī)SRAM的電源

8.3 外設(shè)I/O寄存器

外設(shè)I/O寄存器塊出現(xiàn)在存儲器映射中的不同位置,具體取決于器件和當(dāng)前的工作模式。大多數(shù)外設(shè)I/O寄存器占用的地址范圍為4000 0000h到400F FFFFh。但是,位置和大小可能會因器件而異。有關(guān)詳細(xì)信息,請參見《硬件用戶手冊》。有關(guān)詳細(xì)信息,可參見“I/O寄存器”附錄,也可參見每個外設(shè)功能的寄存器說明。該區(qū)域包含在所有工作模式下始終可用的寄存器。用于控制訪問閃存的閃存I/O寄存器占據(jù)兩個區(qū)域,即407E 0000h至407E FFFFh和407F C000h至407F FFFFh。

Renesas FSP包含采用CMSIS數(shù)據(jù)結(jié)構(gòu)的C語言頭文件,這些文件將特定器件的所有外設(shè)I/O寄存器映射到易于訪問的I/O數(shù)據(jù)結(jié)構(gòu)。

未完待續(xù)

-

mcu

+關(guān)注

關(guān)注

146文章

17019瀏覽量

350373 -

瑞薩

+關(guān)注

關(guān)注

35文章

22294瀏覽量

86098

原文標(biāo)題:RA6快速設(shè)計指南 [9] 存儲器 (1)

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

什么是ROM存儲器的定義

內(nèi)存儲器的分類和特點是什么

內(nèi)存儲器分為隨機(jī)存儲器和什么

ram存儲器和rom存儲器的區(qū)別是什么

內(nèi)存儲器與外存儲器的主要區(qū)別

RA6T2的16位模數(shù)轉(zhuǎn)換器操作 [9] 配置RA6T2 ADC模塊 (6)

![<b class='flag-5'>RA6</b>T2的16位模數(shù)轉(zhuǎn)換<b class='flag-5'>器</b>操作 [<b class='flag-5'>9</b>] 配置<b class='flag-5'>RA6</b>T2 ADC模塊 (<b class='flag-5'>6</b>)](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

RA6T2的16位模數(shù)轉(zhuǎn)換器操作 [4] 配置RA6T2 ADC模塊 (1)

![<b class='flag-5'>RA6</b>T2的16位模數(shù)轉(zhuǎn)換<b class='flag-5'>器</b>操作 [4] 配置<b class='flag-5'>RA6</b>T2 ADC模塊 (<b class='flag-5'>1</b>)](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

淺談存儲器層次結(jié)構(gòu)

CK-RA6M5上的RA AWS云連接,帶蜂窩網(wǎng)絡(luò)-入門指南

如何使用SCR XRAM作為程序存儲器和數(shù)據(jù)存儲器?

CK-RA6M5上的RA AWS云連接(帶以太網(wǎng))入門指南

全面解析存儲器層次結(jié)構(gòu)原理

RA6快速設(shè)計指南 [9] 存儲器 (1)

RA6快速設(shè)計指南 [9] 存儲器 (1)

評論