in_system_ibert IP定制要點(diǎn)

串行收發(fā)器的位置

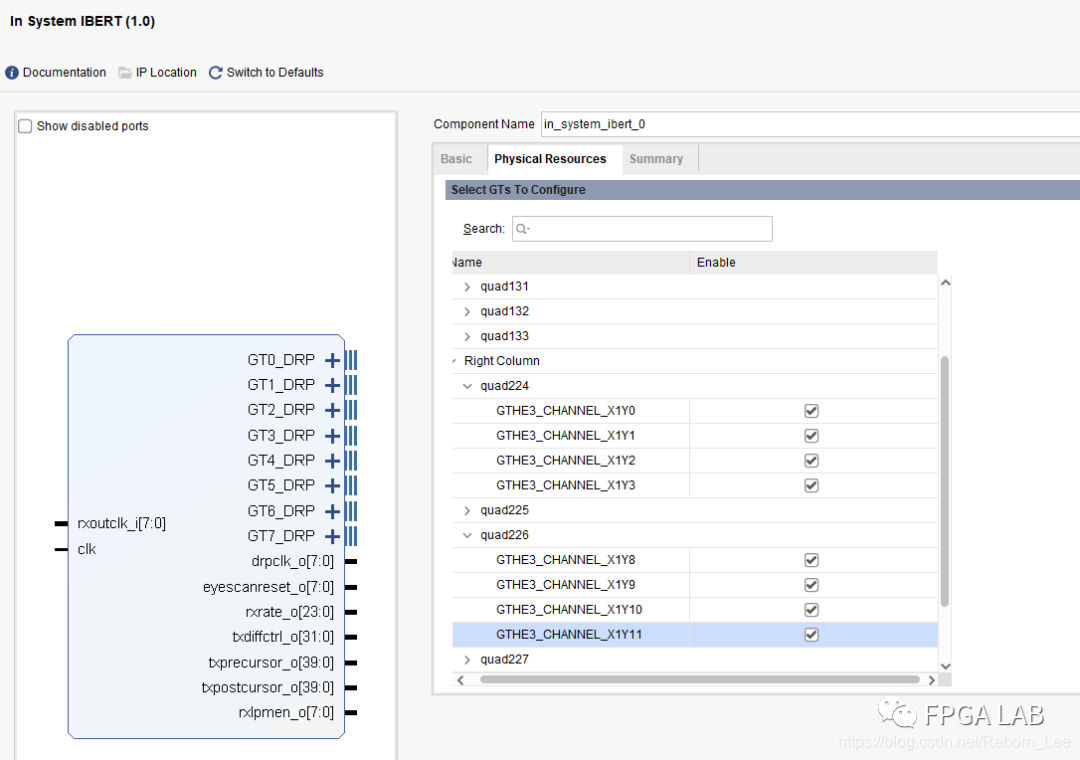

在ISI定制中,需要選擇所使用的串行收發(fā)器的位置,如下:

對(duì)應(yīng)的IP端口處也會(huì)出現(xiàn)相應(yīng)的端口,例如上圖選擇了2個(gè)Quad,也就是8個(gè)通道的串行收發(fā)器,那么對(duì)應(yīng)的drp接口就有8個(gè)。

但這個(gè)對(duì)應(yīng)關(guān)系讓人很迷惑,具體的通道和drp端口信號(hào)是如何對(duì)應(yīng)的呢?

如果有著嚴(yán)格的對(duì)應(yīng)關(guān)系,那么數(shù)據(jù)手冊(cè)或者其他形式有必要給出必要的說明,而不是讓用戶去猜測!人們常常犯著經(jīng)驗(yàn)主義的錯(cuò)誤,認(rèn)為既然讓你選擇了Quad和通道,那么就應(yīng)該對(duì)應(yīng)連接?我在拿不準(zhǔn)的時(shí)候也聽過如此的論調(diào),并信以為然,這花費(fèi)了我很多的時(shí)間去尋找對(duì)應(yīng)關(guān)系,并最終一無所獲,當(dāng)你使用了大量的通道,例如幾十個(gè),那么這種對(duì)應(yīng)關(guān)系的尋找會(huì)更加消耗你的時(shí)間,特別是當(dāng)項(xiàng)目中需要被測眼圖的transceiver一方,有著混亂的通道使用!不管是什么原因,為了原理圖布線方面也好,或者是任性使用,例如:如下定義的rx:

input [31:0] rx;

每4位使用一個(gè)Quad,也就是4個(gè)通道,對(duì)應(yīng)關(guān)系如下:rx[0] 對(duì)應(yīng)通道x1y39 rx[1] 對(duì)應(yīng)通道x1y38 rx[2] 對(duì)應(yīng)通道x1y37 rx[3] 對(duì)應(yīng)通道x1y36

rx[4] 對(duì)應(yīng)通道x1y35 rx[5] 對(duì)應(yīng)通道x1y34 rx[6] 對(duì)應(yīng)通道x1y33 rx[7] 對(duì)應(yīng)通道x1y32

看起來已經(jīng)有點(diǎn)意思了,這種還是倒過來約束的,還行,能接受。如果是下面這種對(duì)應(yīng)關(guān)系:rx[0] 對(duì)應(yīng)通道x1y36 rx[1] 對(duì)應(yīng)通道x1y37 rx[2] 對(duì)應(yīng)通道x1y38 rx[3] 對(duì)應(yīng)通道x1y39

rx[4] 對(duì)應(yīng)通道x1y32 rx[5] 對(duì)應(yīng)通道x1y33 rx[6] 對(duì)應(yīng)通道x1y34 rx[7] 對(duì)應(yīng)通道x1y35

這就必須譴責(zé)了。如果有幾十個(gè)通道,你說怎么玩吧,如果in_system_ibert又需要嚴(yán)格的通道對(duì)應(yīng)關(guān)系,那么信號(hào)的連接將變得十分不直觀,讓接盤開發(fā)者面臨青筋暴裂的危險(xiǎn)。

還是去看數(shù)據(jù)手冊(cè)吧,那么一個(gè)不起眼的IP核,拿不準(zhǔn)的時(shí)候也需要閱讀數(shù)據(jù)手冊(cè)!如果有現(xiàn)場支持工程師,這種問題也不要問了,因?yàn)樗芸赡茏约业臄?shù)據(jù)手冊(cè)都沒有閱讀,就按照慣性思維告訴你,如果不需要嚴(yán)格通道對(duì)應(yīng),人家IP核讓你選擇干嘛,然后你深信不疑,胡亂猜測,呃呃呃,gt1對(duì)應(yīng)x1y39,或者gt1對(duì)應(yīng)x1y0,白白浪費(fèi)時(shí)間,項(xiàng)目做到最后,還對(duì)自己隱隱懷疑。或者最后結(jié)果沒有問題,還以為,自己的運(yùn)氣是好的,選擇是對(duì)的,并輸出文檔,告訴隊(duì)友,就得這樣干,我試過!!!

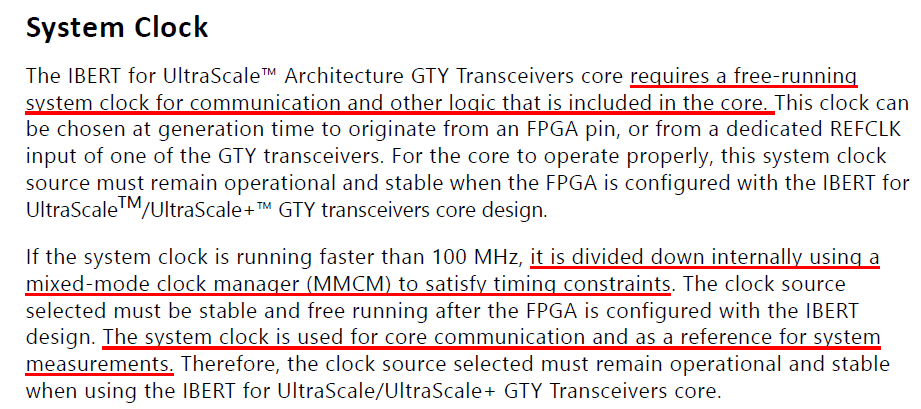

ISI內(nèi)核沒有收發(fā)器位置約束,也沒有為所選收發(fā)器更新任何屬性。所選的收發(fā)器信息僅用于創(chuàng)建ISI模板,并在下載bit文件后在串行IO分析器中分組/顯示所選的收發(fā)器。

很明顯了,沒有位置約束,所選擇的收發(fā)器信息僅僅用于創(chuàng)建例化模板。告訴你有多少個(gè)gt,你接進(jìn)去就完事了。

總結(jié):最接近真理的地方在數(shù)據(jù)手冊(cè)上,我們(除了制定者,設(shè)計(jì)者)外都是閱讀者,各色各樣的閱讀者容易忽略部分信息,或者根據(jù)慣性思維來判斷,因此,帶著問題去數(shù)據(jù)手冊(cè)尋找答案。

如何例化in_system_ibert?

由于這個(gè)IP沒有提供例子程序,所以要正確無誤地使用這個(gè)IP,還有一定的疑惑點(diǎn)?這個(gè)時(shí)候誰也別問,因?yàn)槟憧赡軉柕娜艘仓皇锹犝f過,或者見過,真正手把手體驗(yàn)過,實(shí)踐過的人,也許很難精確遇到。如果你問了,他們會(huì)告訴你,把drp接口連接上去就好了,然后你看看你自己的應(yīng)用場景,已經(jīng)定制好的aurora,或者jesd,srio等等,我了個(gè)去,怎么沒有drp端口,如何和in-system-ibert的drp接口連接? 當(dāng)你找不到drp接口的時(shí)候,他們也許又會(huì)告訴你,在ip核內(nèi)部有,引出來?你若懷疑,甚至還怪你資歷不夠的意思?

我來告訴你,IP核是不要輕易改動(dòng)的,或者說不要改動(dòng),如果你找不到drp接口,可以嘗試看看數(shù)據(jù)手冊(cè),或者試試去掉某些選項(xiàng),或者添加某些選項(xiàng),但我建議還是看看收據(jù)手冊(cè),數(shù)據(jù)手冊(cè)會(huì)有那個(gè)接口的描述,你會(huì)得到答案。

這里就已經(jīng)可能解決很多疑惑了,但是還不夠,沒有個(gè)示例來參考,又沒有例子工程,我會(huì)不放心我連接的對(duì)不對(duì),或者說對(duì)這個(gè)IP核使用的對(duì)不對(duì),因?yàn)槲乙坏├M(jìn)去,并生成bit流,工程大了會(huì)消耗大量的時(shí)間,怎么辦呢?

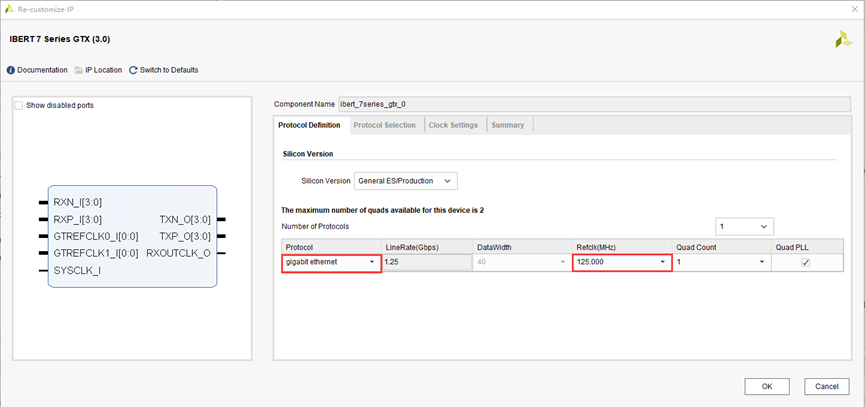

為了提高成功率還是要找到一個(gè)這個(gè)ip核使用的例子程序來研究研究,這里建議可以使用transceiver IP,內(nèi)部有例化in-system-ibert的選項(xiàng),你勾選之后隨便生成一個(gè)例子程序,就可以看到這個(gè)ip核到底怎么使用的,照葫蘆畫瓢,是最直接的方式。

例如:

生成例子程序:

加粗樣式

對(duì)著程序看看如何無誤地使用in-system-ibert,并且如何配合VIO IP核來使用,都可以清晰地看到解決辦法!

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3401瀏覽量

105871 -

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489 -

串行收發(fā)器

+關(guān)注

關(guān)注

0文章

14瀏覽量

9503

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD自適應(yīng)計(jì)算加速平臺(tái)之GTYP收發(fā)器誤碼率測試IBERT實(shí)驗(yàn)(6)

是否有關(guān)于為GTY收發(fā)器發(fā)布IBERT的討論?

為什么工具在沒有IBERT環(huán)回模式的情況下顯示NO LINK

IBERt virtex 6.是否可以在FPGA上同時(shí)運(yùn)行外部時(shí)鐘模塊和IBERT模塊?

怎么在ibert中使用外部時(shí)鐘

加載比特流到device.ibert核心沒有顯示任何鏈接是為什么?

如何使用IBERT生成眼圖

IBERT設(shè)計(jì)如何配置?

如何使用ISE 14.7并且使用斯巴達(dá)6生成了IBERT核心?

IBERT軟件或Artix FPGA存在問題?

利用 IBERT 進(jìn)行 GTX 信號(hào)眼圖測試 精選資料分享

利用IBERT核對(duì)GTX收發(fā)器板級(jí)測試

使用Vivado 2016.3中IBERT調(diào)試的好處及步驟

基于IBERT的GTX數(shù)據(jù)傳輸測試

如何正確使用in_system_ibert呢?

如何正確使用in_system_ibert呢?

評(píng)論