芯熾集團·新品發布

SC6301

低功耗超低噪聲時鐘抖動消除器

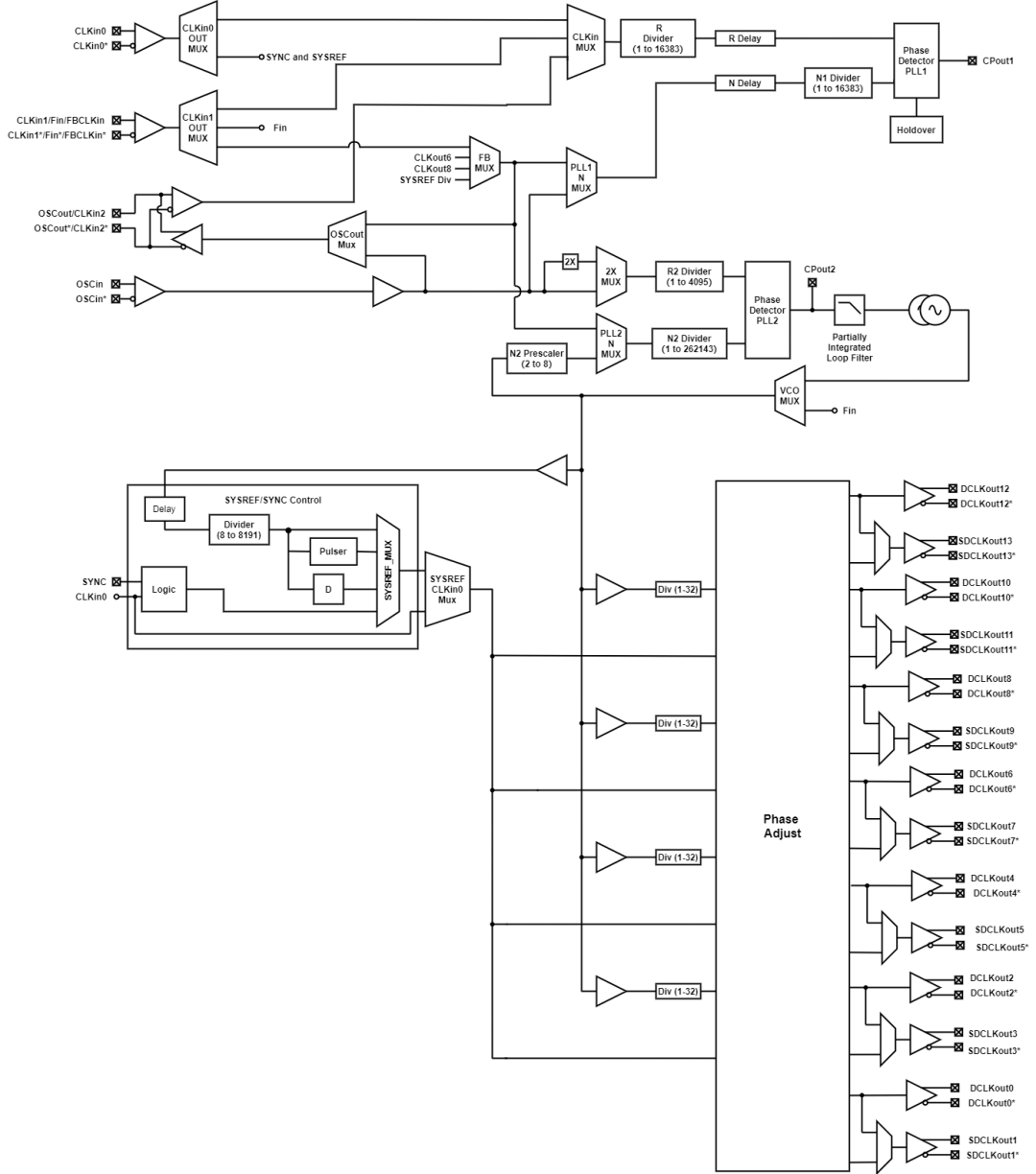

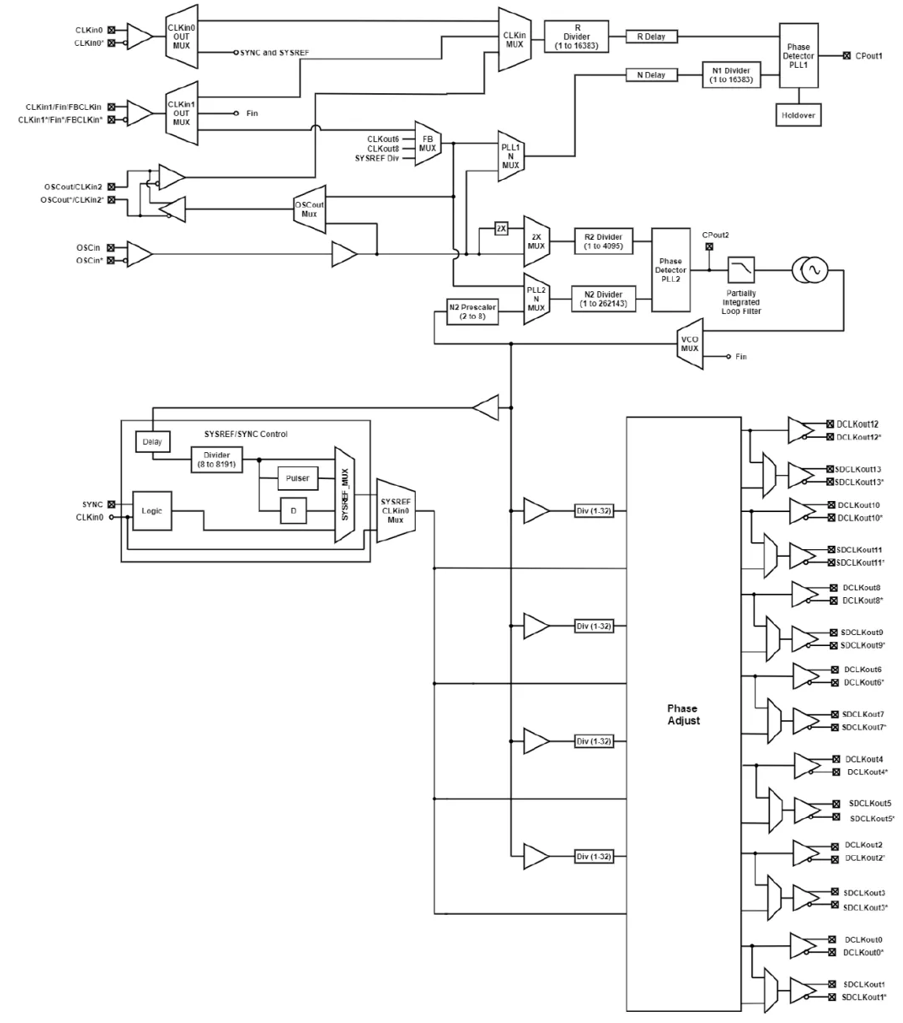

SC6301是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅動7個JESD204B轉換器或其他邏輯設備。SYSREF可以使用直流和交流耦合來提供。不僅限于JESD204B應用,14個輸出均可單獨配置為傳統高性能時鐘系統輸出。

SC6301具有高性能、低功耗、雙VCO、動態數字延遲、信號丟失保持等特性。因此,SC6301是提供靈活的高性能時鐘樹的理想選擇。

新品簡介

01主要性能

支持JEDECJESD204B

超低RMS抖動

76fs RMS Jitter (10kHz到20MHz)

-162dBc/Hz@245.76 MHz

PLL2可提供多達14路差分時鐘

最多7個SYSREF時鐘

時鐘最大輸出頻率3.1GHz

支持LVPECL, LVDS, HSDS, LCPECL等輸出接口

PLL1提供一個VCXO/Crystal緩沖輸出

支持LVPECL, LVDS, 2路LVCMOS等輸出接口

PLL1

3個備用的輸入時鐘

手動切換模式

無中斷切換和LOS

集成低噪聲的晶體振蕩電路

具有輸入時鐘丟失的保持模式

PLL2

相位檢測速率:=<155MHz

2路集成低噪聲VCO

輸出支持1到32整數分頻,占空比50%

高精度數字延遲,可自適應性

23ps步進模擬延遲

模式:雙PLL, 單PLL, 時鐘分布

工作溫度:-40℃到85℃

工作電壓:3.15V到3.45V

QFN-64封裝

02應用場景

無線基礎設施

數據交換時鐘

網絡, SONET/SDH, DSLAM

醫療/視頻

測量

03功能框圖

審核編輯:湯梓紅

-

時鐘抖動

+關注

關注

1文章

62瀏覽量

15917 -

消除器

+關注

關注

0文章

42瀏覽量

8641 -

低噪聲

+關注

關注

0文章

203瀏覽量

22825

原文標題:◣芯熾集團新品發布◥ SC6301 低功耗超低噪聲時鐘抖動消除器

文章出處:【微信號:HaveFunFPGA,微信公眾號:玩兒轉FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于級聯PLL的超低噪聲精密時鐘抖動濾除技術仿真和研究設計

超低功耗嵌入式的隱患怎么消除?

支持204B,輸出頻率高達3.1G,支持14路差分時鐘輸出,超低抖動,首顆正向國產替代時鐘調節器SC6301

LMK0482x超低噪聲JESD204B兼容時鐘抖動消除器數據表

LMK04208具有雙環PLL的低噪聲時鐘抖動消除器數據表

LMK04816具有雙環PLL的三輸入低噪聲時鐘抖動消除器數據表

SC6301低功耗超低噪聲時鐘抖動消除器簡介

SC6301低功耗超低噪聲時鐘抖動消除器簡介

評論