二,差分邏輯電平匹配

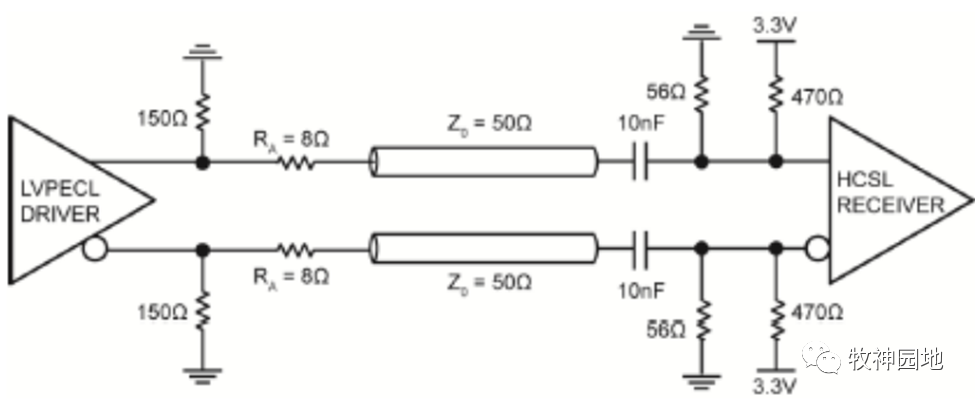

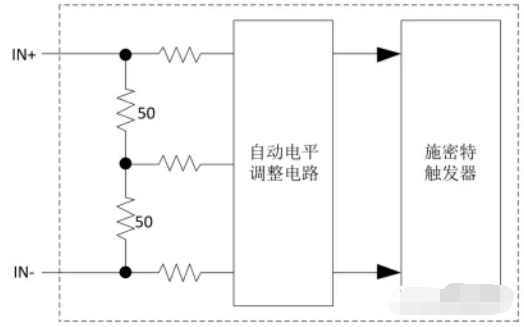

差分邏輯電平之間的匹配,主要應(yīng)用于時(shí)鐘和高速信號(hào)。通過之前章節(jié)關(guān)于差分邏輯電平的電路結(jié)構(gòu)分析,為保證差分信號(hào)輸出與輸入的匹配,則要滿足如下幾個(gè)條件:

- 對于傳輸線來說,要保證傳輸線阻抗匹配(終端并聯(lián)),保證信號(hào)傳輸質(zhì)量。

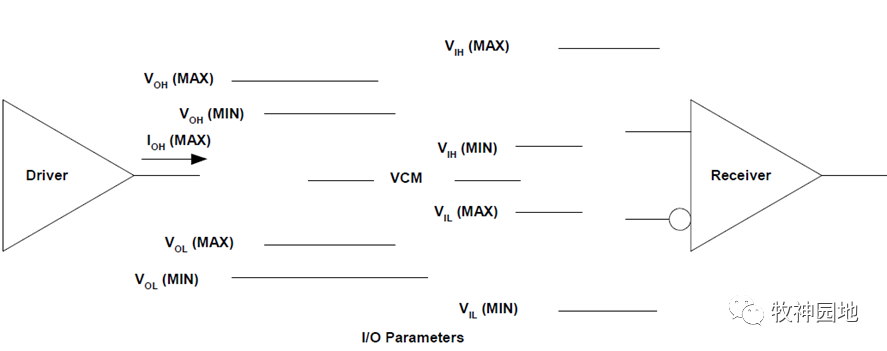

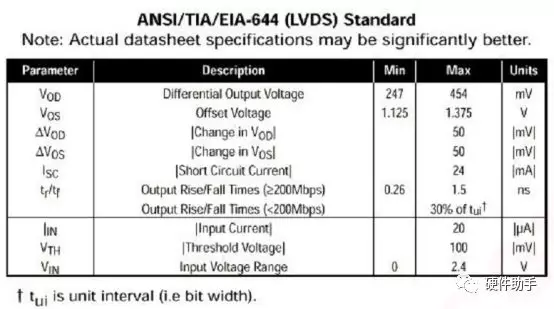

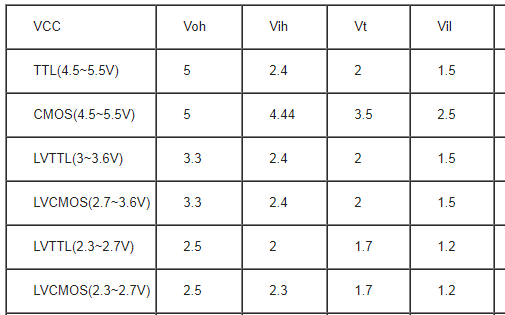

LVPECL,LVDS,HSTL以及CML差分邏輯電平之間的輸出和輸入判斷電平如下圖所示。

1,LVPECL驅(qū)動(dòng)輸出

LVPECL電路邏輯輸出必須要有對地直流偏置通路,作為其共模輸出電壓。

1.1 LVPECL to LVPECL

LVPECL直流耦合輸出的兩種匹配電路如下圖所示。

- 左下圖中終端上下來電阻用于阻抗匹配和共模電壓設(shè)置:

1, 終端上下拉電阻(83Ω和130Ω)用于傳輸線阻抗匹配: 83//130 = 50Ω;

2, 直流耦合方式中終端匹配接至Vcc-2V偏置電壓,達(dá)到Vcc-1.3V = 2V的共模輸入電壓要求(具體原因請參考《ECL電平》章節(jié)相關(guān)內(nèi)容)。

- 右下圖中終端匹配電阻網(wǎng)絡(luò)的設(shè)計(jì),此方案相比于第一個(gè)方案節(jié)省了一個(gè)電阻。

LVPECL交流耦合輸出的兩種匹配電路如下圖所示。

- 左下圖中輸出端采用150Ω下拉,終端上下來電阻用于阻抗匹配和共模電壓設(shè)置:

1, 終端上下拉電阻(83Ω和130Ω)用于傳輸線阻抗匹配:83//130 = 50Ω;并提供LVPECL共模輸入電壓:Vcc -1.3V = 2V;

2, 150Ω下拉電阻用于提供LVPECL輸出直流偏置,以及為輸出電流提供直流電流路徑。

——細(xì)心的胖友們應(yīng)該還記得,在《ECL電平》章節(jié)中推薦設(shè)計(jì)的終端上下拉電阻以及輸出端下拉電阻阻值與本章計(jì)算的電阻值有所不同,這主要是跟器件本身相關(guān),后續(xù)遇到LVPECL相關(guān)設(shè)計(jì),需要根據(jù)器件資料的推薦進(jìn)行設(shè)計(jì)。

- 右下圖中終端匹配電阻網(wǎng)絡(luò)設(shè)計(jì)中,帶電容的終端匹配網(wǎng)絡(luò)主要用于:消除差分信號(hào)抖動(dòng)導(dǎo)致的共模噪聲;VBB一般在接收端器件內(nèi)部提供。

1.2 LVPECL to LVDS

LVPECL直流耦合LVDS,如下左圖所示,當(dāng)LVPECL輸出對于LVDS輸入端電壓太高時(shí),通常需要33Ω串聯(lián)電阻用于減小輸入電壓范圍;但大多數(shù)LVDS接收機(jī)能夠接收LVPECL信號(hào),不需要在LVDS輸入端對LVPECL信號(hào)進(jìn)行衰減,因?yàn)長VDS輸入端的共模范圍很寬。

LVPECL交流耦合LVDS,如下圖所示;在交流耦合時(shí)LVPECL輸出端的150Ω下拉電阻還是需要的,它為輸出端提供了直流偏置通路;終端100Ω差分阻抗匹配電阻,用于提供足夠的信號(hào)擺幅來驅(qū)動(dòng)LVDS輸入端,兩個(gè)10kΩ電阻將LVDS共模輸入電壓設(shè)置為1.65V,在LVDS接收機(jī)共模電壓范圍內(nèi)。

——很多LVDS輸入端已經(jīng)集成了100Ω電阻,那么外部的100Ω電阻可以去掉。

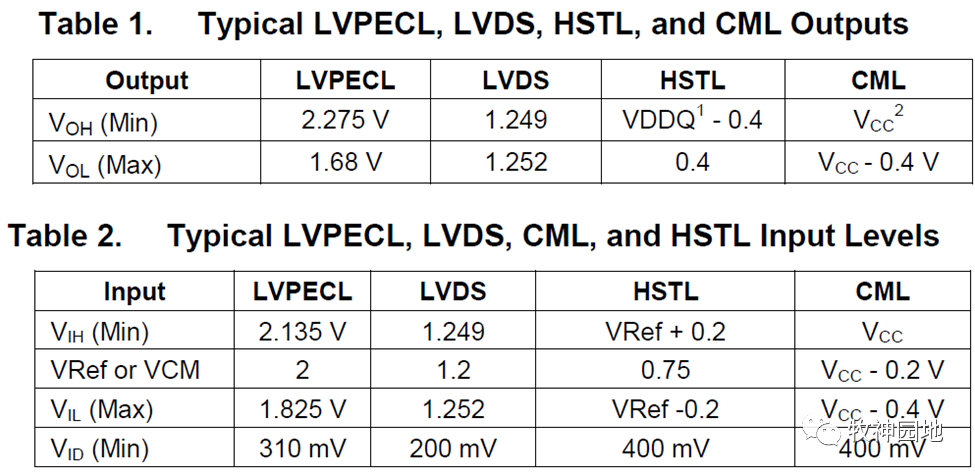

1.3 LVPECL to CML

如下左圖所示為直流耦合電路,為了匹配CML的輸入,需要做復(fù)雜的電路匹配設(shè)計(jì);所以交流耦合設(shè)計(jì)更加簡潔、方便,推薦使用交流耦合匹配的方式。交流耦合LVPECL在輸出端設(shè)計(jì)150Ω下拉電阻,用于提供直流偏置回路;LVPECL輸出擺幅是750mv而CML要求輸入擺幅是400mV(68%),那么如下圖所示需要進(jìn)行分壓:50/(50+23) = 0.68,所以串聯(lián)電阻Ra = 23Ω,實(shí)際設(shè)計(jì)選擇Ra = 25Ω。

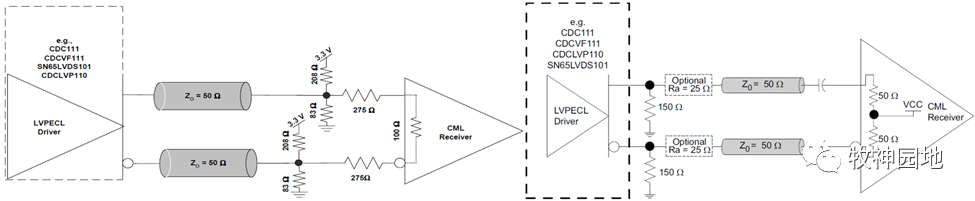

1.4 LVPECL to HCSL

如下圖所示,在LVPECL交流耦合HSCL,輸出端150Ω電阻下拉提供直流偏置;為了將800mV的LVPECL擺幅衰減到700mV的HCSL擺幅時(shí),必須在150Ω電阻之后放置一個(gè)衰減電阻(Ra =8Ω);HCSL輸入端需要重新偏置,可以通過將470Ω電阻連接3.3V和56Ω電阻到GND上來實(shí)現(xiàn)HCSL輸入端350 mV的共模偏置電壓。

2,LVDS驅(qū)動(dòng)輸出

2.1 LVDS to LVPECL

如下圖所示,LVDS輸出直流耦合LVPECL輸入,83Ω與130Ω并聯(lián)匹配提供LVPECL輸入共模電壓:2V;同時(shí)提供了差分線的阻抗匹配:83Ω//130Ω = 50Ω。

如下圖為交流耦合匹配電路,LVDS輸出端不需要提供直流偏置回路,所以我們只需設(shè)計(jì)LVPECL輸入端的共模偏置電壓(Vcc – 1.3V = 2V),和終端阻抗匹配(差分:100Ω,單端:50Ω)。

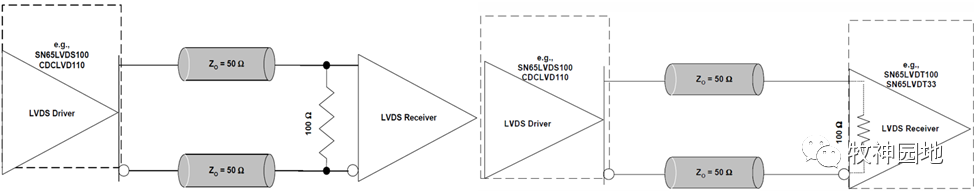

2.2 LVDS to LVDS

LVDS輸出直流耦合LVDS輸入,如下圖所示;電路匹配非常簡單,只需在終端跨接100Ω電阻,如果輸入端已集成100Ω終端電阻,那么可以去掉外部電阻;共模偏置電壓直接由輸出端提供。

LVDS輸出交流耦合LVDS輸入,同樣只需要跨接100Ω作為終端端接;但此時(shí)輸入端共模偏置電壓需要外部提供,具體如下圖所示。如果器件內(nèi)部集成了100Ω終端電阻以及內(nèi)部偏置,那么交流耦合直連即可,具體需要看器件規(guī)格書,再?zèng)Q定采用直流還是交流耦合更加方便。

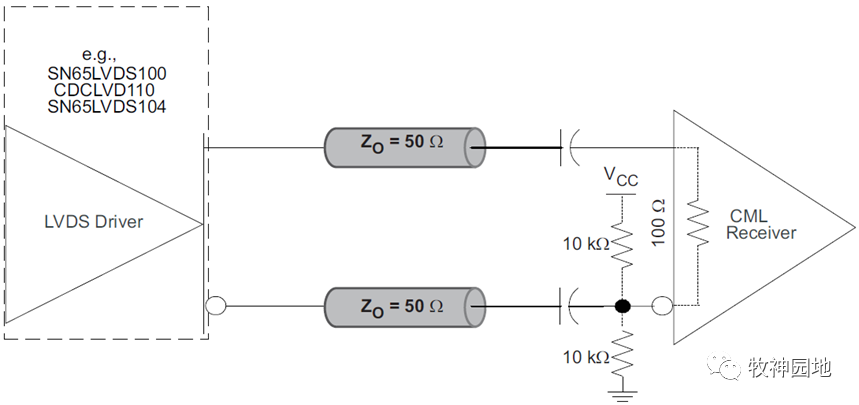

2.3 LVDS to CML

大多數(shù)CML接收器有片上終端匹配(100Ω),不需要額外電阻。而且只有當(dāng)CML輸入端不提供偏置電壓時(shí),才需要兩個(gè)10KΩ電阻。但這些都需要根據(jù)實(shí)際的器件規(guī)格書來確定具體的匹配方式。

3,CML驅(qū)動(dòng)輸出

3.1 CML to LVPECL

如下圖所示,CML輸出到LVPECL輸入一般推薦使用交流耦合的方式;50Ω上拉電阻用于CML輸出的直流偏置,并提供一個(gè)源端匹配(這個(gè)50Ω電阻本來是在CML輸入端上拉的,需要外部匹配,具體參考《LVDS&CML 電平》相關(guān)章節(jié)內(nèi)容);如下左圖所示,LVPECL輸入端器件內(nèi)置了匹配電路。

如下右圖交流耦合匹配電路,R1應(yīng)大于50Ω以防止CML輸出損耗和PCB損耗過大,無法滿足LVPECL輸入端的最小差分輸入電壓擺幅要求。

3.2 CML to LVDS

一般來說CML輸出到LVDS輸入,建議采用AC耦合的方式;原理同上,輸出端需要50Ω上拉電阻已提供CML輸出直流偏置和匹配;LVDS輸入端則需提供共模偏置電壓和100Ω電阻以提供差模電壓擺幅。如果輸入端LVDS已經(jīng)集成了100Ω電阻和共模偏置電壓,那么可以直接通過交流耦合接至輸入端。

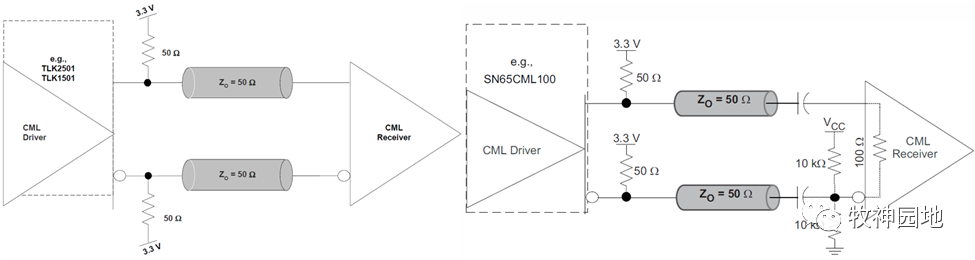

3.3 CML to CML

如果CML輸出端和接收端都有相同的VCC電源電壓和片上上拉電阻(50Ω),那么可以直接連接,無需外部元件;如果輸出端不提供一個(gè)內(nèi)部50Ω的上拉電阻,那么50Ω上拉電阻需要放置在輸出端或接收端。而對于交流耦合方式,如下右圖所示;只有當(dāng)CML接收端不提供共模偏置電壓,才需要兩個(gè)10kΩ的電阻。匹配連接的方式需具體根據(jù)器件規(guī)格書再確定。

4,HCSL驅(qū)動(dòng)輸出

3.1 HCSL to LVDS

如下圖所示, HCSL輸出端電流在0和14mA之間切換:當(dāng)一個(gè)輸出管腳為低電平(0)時(shí),另一個(gè)為高電平(驅(qū)動(dòng)14mA)。HCSL驅(qū)動(dòng)器的等效負(fù)載電阻為43Ω,與50Ω阻抗并聯(lián)后相當(dāng)于23.11Ω,計(jì)算可得LVDS輸入的擺幅為14mA * 23.11Ω= 323mV。LVDS輸入需要重新偏置,可以通過將一個(gè)8.7KΩ電阻連接到3.3V和5KΩ電阻連接到GND來實(shí)現(xiàn)LVDS接收器輸入共模的1.2V 直流電平;如果LVDS接收器差分輸入端上已內(nèi)置100Ω電阻和共模偏置電壓,則不需要外部100Ω電阻和共模偏置電阻。

寫在最后

電平匹配設(shè)計(jì)并不是一成不變的,首先需要根據(jù)器件規(guī)格書從理論上對輸出端和輸入端的電路結(jié)構(gòu),高電平范圍,擺幅等進(jìn)行理論分析;然后進(jìn)行電路匹配的設(shè)計(jì),一般交流耦合更加簡單方便(除非是相同電平標(biāo)準(zhǔn),而且輸出與輸入規(guī)格相匹配的情況);最后單板回來后需要進(jìn)行實(shí)際測試,確定匹配設(shè)計(jì)能夠滿足輸入端的信號(hào)質(zhì)量要求。

-

上拉電阻

+關(guān)注

關(guān)注

5文章

359瀏覽量

30574 -

接收器

+關(guān)注

關(guān)注

14文章

2458瀏覽量

71806 -

電源電壓

+關(guān)注

關(guān)注

2文章

987瀏覽量

23946 -

邏輯電平

+關(guān)注

關(guān)注

0文章

151瀏覽量

14403 -

lvds接口

+關(guān)注

關(guān)注

1文章

128瀏覽量

17390

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

電平設(shè)計(jì)基礎(chǔ):電平匹配設(shè)計(jì)

差分邏輯電平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

信號(hào)邏輯電平標(biāo)準(zhǔn)的詳細(xì)說明

邏輯電平的一些基本概念詳細(xì)說明

常用的差分邏輯電平詳細(xì)介紹

LVDS和CML與LVPECL的同種差分邏輯電平之間的互連教程

邏輯電平--差分信號(hào)(PECL、LVDS、CML)電平匹配

什么是邏輯電平?如何實(shí)現(xiàn)電平轉(zhuǎn)換?(原理講解+電路圖)

電平設(shè)計(jì)基礎(chǔ):差分邏輯電平匹配

電平設(shè)計(jì)基礎(chǔ):差分邏輯電平匹配

評(píng)論