引言

之前在《一文讓你理解DC綜合全過程!》中,和大家分享了DC映射和優化流程,接下來本文針對如何寫DC綜合腳本提出五點建議。如果您是DC新手,那么您會發現這幾點建議很是實用;如果您是DC老手,由于工具版本的更新,可能增加了您未曾注意的功能,希望本文的分享能對您有所幫助。

一 、使用set_auto_disable_drc_nets命令使時鐘網絡免于設計規則檢查

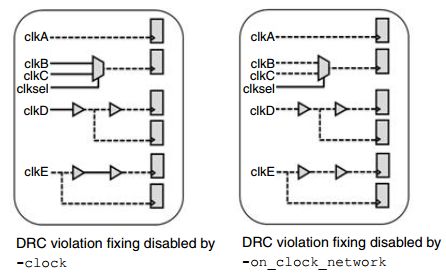

DC會自動通過插入 buffer或者 resizing單元的方式進行設計規則違例修正,不過時鐘常值和scan是比較特殊的net,綜合人員可以使用set_auto_disable_drc_nets命令來聲明不對這些特殊nets進行設計規則違例修正。-default為默認選項,默認情況下時鐘和常值是被disable的,不過scan并未disable,可以使用該命令帶-all選項,將三者都 disable,或者分別帶-on_clock_network、-constant和-scan來分別設置。需要說明的是-clock和-on_clock_network 有些差別,建議使用-on_clock_network,具體差別如圖1所示,虛線是被disable的時鐘線,-clock保證了對連接到觸發器的時鐘線,不會進行DRC檢查,-on_clock_network是對時鐘網絡disable DRC,經過組合邏輯再供給到觸發的時鐘也不會被DRC檢查

圖 1

二 、使用set_clock_groups命令來約束多時鐘設計

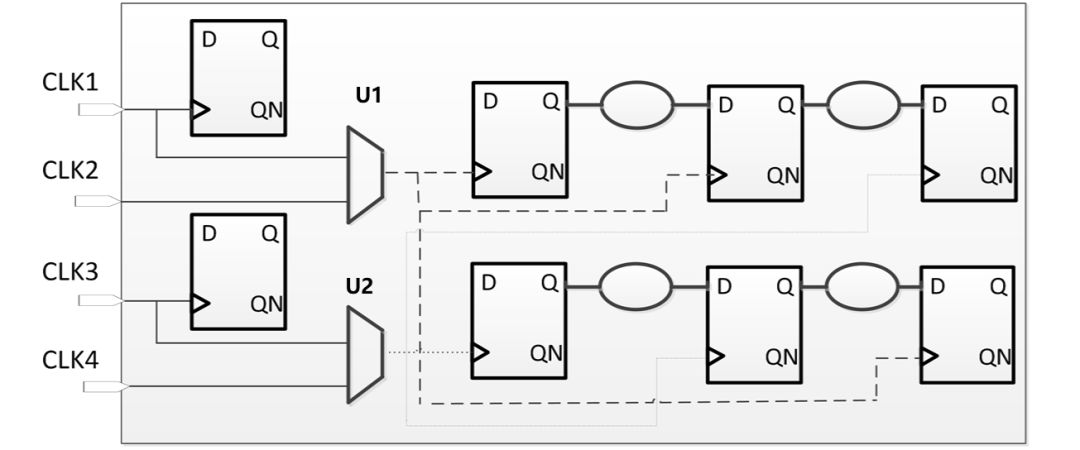

基本所有的多時鐘設計中都有時鐘切換電路,兩個或者多個時鐘輸入到時鐘切換模塊,輸出被選擇的一個時鐘。時鐘切換電路的電路結構在《你不可不知的——時鐘切換電路》中做了詳細介紹,需知DC中時鐘屬性是可以穿過任何組合邏輯的,假設在時鐘切換模塊前已經用create_clock聲明了兩個時鐘,這兩個時鐘經過時鐘切換模塊時穿過的都是組合單元,那么該模塊的輸出端口也是有兩個時鐘穿過的。面對這種情況,傳統的做法是使用set_case_analysis來做功能選擇,比如用于測試的掃描時鐘和功能時鐘間的切換,這一命令就很有效。但是面對如圖2所示的情況,使用set_case_analysis命令,便人為的選定了自認為時序最緊的情況,比如在CLK1和CLK2中選擇了頻率更高的CLK1,在CLK3和CLK4中選擇了頻率更高的CLK3,但是可能實際上CLK1到CLK4比CLK1到CLK3時序更緊張。這時,使用如下命令,只告訴DC時鐘間的關系,讓DC自己分析更穩妥。

方式一:

create_clock -name CLK1 -period 5[get_ports CLK1]

create_clock-name CLK2 -period 10 [get_ports CLK2]

create_clock-name CLK3 -period 15 [get_ports CLK3]

create_clock -nameCLK4 -period 20 [get_ports CLK4]

set_false_path –from [get_clocksCLK1] –to [get_clocks CLK2]

set_false_path–from [get_clocks CLK2] –to [get_clocks CLK1]

set_false_path–from [get_clocks CLK3] –to [get_clocks CLK4]

set_false_path–from [get_clocks CLK4] –to [get_clocks CLK3]

方式二:

create_clock -name CLK1-period 5 [get_ports CLK1]

create_clock-name CLK2 -period 10 [get_ports CLK2]

create_clock-name CLK3 -period 15 [get_ports CLK3]

create_clock -nameCLK4 -period 20 [get_ports CLK4]

set_clock_groups –logically_exclusive–group CLK1 –group CLK2

set_clock_groups–logically_exclusive –group CLK3 –group CLK4

方式一和方式二的作用等價,但顯然,使用set_clock_groups命令來描述時鐘關系的方式二更簡便。其實,除了選項–logically_exclusive,該命令還可以帶-phsically_exclusive和-asynchronous選項,這三個選項都可以表述聲明的時鐘組間的時序路徑間是沒有約束檢查的。不同點在于: 1)-asynchronous選項表示聲明的時鐘組的組間關系是異步的,異步關系的時鐘在芯片正常工作時物理上是可以同時存在的; 2)–logically_exclusive和-phsically_exclusive選項在DC中作用是相同的,–logically_exclusive選項表示的是聲明的時鐘組的組間關系是邏輯獨立、物理可共存的,而-phsically_exclusive選項表示的是聲明的時鐘組的組間關系是物理獨立的,如圖2所示,沒有信號是跨CLK1傳遞到CLK2域的,但是CLK1和CLK2是在電路中共存的。這點不同在PT做信號完整性分析時是有影響的,-phsically_exclusive較–logically_exclusive樂觀,而-asynchronous最悲觀。

圖2

另外,set_clock_groups只帶一個-group選項的用法也很常見,比如:set_clock_groups–phsically_exclusive –group scan_clk,這表示DFT掃描測試時鐘scan_clk與其他所有時鐘物理上不共存。其實掃描時鐘和功能時鐘的關系也是異步的,而使用-asynchronous選項對PT的影響要比實際悲觀,故而對于既是物理互斥也是異步的情況,應使用選項-phsically_exclusive。事實上,圖2示例的時鐘數目少、電路結構簡單,而實際電路中時鐘選擇和電路結構復雜的多,這時候使用命令set_clock_groups描述時鐘關系,優勢更為明顯。事實上,掃描模式與功能模式不同時存在,且時鐘頻率差距甚大,掃描時鐘與功能時鐘的切換使用命令 set case analysis足以。

對圖2進一步分析,時鐘切換電路U1前有兩個時鐘CLK1和CLK2,圖中沒有信號跨越這兩個時鐘域,那么這兩個時鐘是邏輯獨立、物理共存的。那如果有信號跨越這兩個時鐘域傳輸的話,CLK1和CLK2便不再是邏輯獨立的了,可是U1的輸出端口Z后的時鐘,仍然是物理獨立的,事實上,這種情況更為普遍。下面的約束也更為合適:

create_clock -name CLK1 -period 5[get_ports CLK1]

create_clock-name CLK2 -period 10 [get_ports CLK2]

create_clock-name CLK3 -period 15 [get_ports CLK3]

create_clock -nameCLK4 -period 20 [get_ports CLK4]

create_generated_clock–name G_CLK1 divide_by 1 –source [get_pins U1/A] [get_pins U1/Z] –combinational

create_generated_clock–name G_CLK2 divide_by 1 –source [get_pins U1/B] [get_pins U1/Z] –combinational–add

set_clock_groups –phisically_exclusive –group G_CLK1 –group G_CLK2

create_generated_clock–name G_CLK3] divide_by 1 –source [get_pins U2/A] [get_pins U2/Z]-combinational

create_generated_clock–name G_CLK4] divide_by 1 –source [get_pins U1/B] [get_pins U2/Z] –combinational–add

set_clock_groups –phisically_exclusive –group G_CLK3 –group G_CLK4

還有一種常見的情況是,時鐘經過分頻模塊分出多個分頻時鐘,然后多個分頻時鐘經過時鐘切換電路選擇輸出,而且分頻電路中常有小數分頻,比如1.5分頻,且如果有信號從1.5分頻時鐘域傳到未分頻的時鐘域,這時候最緊的時鐘約束應是半個時鐘周期,那么綜合人員需要跟設計人員確認電路中絕無這種工作情況的可能,才能使用set_case_analysis來選擇未分頻時鐘對后續電路約束。而電路是多個設計人員分別對各自模塊設計的,假設和溝通常常容易出錯,這時候如果在分頻模塊的輸出端口產生兩個物理獨立的generated時鐘,那么DC工具會給出分析結果。善用命令 set_clock_groups描述時鐘關系,優勢確實很明顯。

三 、面對pad-limitted設計,可調節變量placer_max_cell_density_threshold進行迭代

現在 synopsys建議使用SPG流程,該流程和后端有更好的匹配和關聯。如果綜合人員所面臨的設計是 pad-limitted,那么在第二次綜合流程中可以聲明一個最小單元密度,這讓 core有更好的利用率百分比,也就是讓DC圍繞著核更密集的排布單元和連線。 set_app_var placer_max_cell_density_threshold0. 7; # In DC/ICC set_app_options -nameplace.coarse. max _density -value 0.7; # In ICC ll 注意:如果在non-spg流程中,DC使用了上訴命令需要在ICC中也使用,在spg流程中ICC 會略過這一步驟,可以不在ICC中做同樣的命令設置。如果不對placer_ max_cell_density_threshold設置,DC默認其為50%,在執行了compile_ultra命令后,DC會對這個值重新計算,并將重新計算的值覆蓋默認值。綜合人員可以查看這個值,并可以將這個值設置為重新計算值和1之間的中間值,進而指導DC下一次綜合。

四、盡量使用高閾值電壓庫綜合,時序實在無法收斂時,使用多閾值電壓庫來綜合

泄露功耗與工藝和閾值電壓有關,閾值電壓越大,泄露功耗越低,但是器件速度越慢。DC EXPERT 需要通過命令set_leakage_optimization true 聲明,而DC Ultra會自動進行泄露功耗優化,為了不影響時序性能,DC會默認對非關鍵路徑進行功耗優化。若采用了多閾值電壓庫,DC 會自動對非關鍵時序路徑,用高閾值電壓單元替換低閾值電壓單元;綜合人員可以使用set_multi_vth_constraint 命令來聲明設計所允許使用的低閾值電壓單元的百分比,并通過從5%到10%,開始逐步提升低閾值電壓單元所占百分比,直到時序符合要求為止。在使用命令set_multi_vth_constraint時,帶-type soft選項,DC會在保證時序的前提下,進行功行功耗優化;另外,在計算低閾值電壓單元所占百分比的時候,并沒有算進黑盒子,如果欲將黑盒子也算進來,使用-include_blackboxes選項。 一般工藝廠提供的工藝庫都是已經根據閾值電壓的不同對庫單元進行了分組的,如果沒有分組的話,多閾值電壓庫可以使用set_attribute命令對庫屬性進行設置,從而將多閾值電壓庫中的不同單元根據閾值電壓的不同進行分組。

Library-level attribute: defaultthreshold voltage_group:string; Library-cell-level attributestring; 綜合人員可以使用analyze_library–multi_vth 命令來獲得各個閾值電壓組的時序和泄露功耗信息。綜合完成后,可以使用report_threshhold_voltage_group 命令,報告設計中低閾值電壓單元占比情況。

五、使用set_app_var compile_timing_high_effort true 命令獲得更好的時序QoR

在第二次綜合時使用compile_ultra –timing_high_effort_script 是大家很熟悉的方式了,不過其中的開關選項-timing_high_effort_script目前在DC 優化過程中已經不起作用了,若希望DC 花費更多資源在時序優化上,那么可使用命令set_app_var compile_timing_high_effort true來獲得更好的時序QoR。需要說明的是,該變量的設置只在Design compiler topographical模式下有效,即需要用compile_ultra -spg 命令進行綜合優化。

以上幾點純是個人建議,寫DC腳本的最終目的是設置合理的約束來指導DC更好的優化電路,每個人都有自己的習慣和綜合策略,歡迎大家多多交流心得體會。

審核編輯:湯梓紅

-

時鐘

+關注

關注

10文章

1721瀏覽量

131378 -

DC

+關注

關注

9文章

3644瀏覽量

679376 -

觸發器

+關注

關注

14文章

1996瀏覽量

61057 -

切換電路

+關注

關注

0文章

29瀏覽量

9401

原文標題:五點Tips助你DC應用進階

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

五點技巧助你DC應用進階

五點技巧助你DC應用進階

評論