【摘要】

信號的AC耦合方式具有屏蔽發(fā)送端和接收端直流偏置不一致的好處,但并不是所有信號都適合使用這種方式傳輸,即只有直流平衡信號(數(shù)據(jù)流中的1與0的數(shù)量相等的狀態(tài))才可以。本文試圖從電容充放電的角度,解釋非直流平衡信號不適用于AC耦合方式傳輸?shù)脑颉?/p>

一、問題的提出

在某系統(tǒng)研發(fā)過程中,出現(xiàn)了2次串行數(shù)據(jù)在接收端不能正常接收的情形,均為AC耦合時傳輸了非直流平衡信號。一次是發(fā)送固定碼型64個連0然后一個1的變化,在接收端不能正確解碼;另外一次為PRBS的數(shù)據(jù)源經過ADC采樣后,每個采樣點量化的8bit分別由8個通道傳輸,每個通道的0,1不均衡,使用AC耦合傳輸后不能正常接收。為何非直流平衡信號不能通過AC耦合電路,本文試圖解釋這一問題。

二、解決思路

1.電容的基本概念

電容的定義如公式1所示。

Q為電容的電荷量,U為電容兩極間電壓。

根據(jù)這個定義可以知道,電容可以儲存電荷,儲存的電荷量與加在電容上的電壓有關。電容在存儲或者釋放電荷時,必然會有電荷的流動,形成電流。電流的大小如公式2所示。

比如電容在充電時,正極板積聚更多正電荷,負極板積聚更多負電荷,電荷的遷徙必將產生電流。這個公式說明,對于同一個電容來說,充放電時電流大小與電容極板間電壓的變化快慢有關,變化越快,電流越大。

2.電容的充電和放電

通俗的解釋電容的充電和放電,可以有如下描述。

電容充電:兩極板的壓差變大,積聚更多電荷;

電容放電:兩極板的壓差變小,釋放更多電荷;

設電容初始電壓為V0,最終電壓為V∞,則任意時刻t的充電/放電電壓為

圖 1 電容充放電電壓曲線

一般情況下,在大約3~5RC后,電容的充放電過程就基本完成了。因此時間常數(shù)RC直接決定了電容充放電的快慢。根據(jù)公式2,對于同一個電路來說(充放電時間一樣),充放電前后的壓差越大(電容壓差定義為|V∞- V0|),那么充放電的電流也就越大。

電容的隔直流,通交流特性,也由電容的充放電來解釋。如果電容兩極的電壓不變化,則沒有電流和電荷的流動。如果電壓發(fā)生變化,電路中就會產生電流,電流在電容的另一端就會引起電壓的變化。也就是說,直流信號相當于極板間電壓無變化,沒有電流流過;交流信號,電容在不停的充放電,有電流流過,則相應的電壓變化也傳遞到電容的另外一端。

3.電容兩端電壓不能突變

不論電荷聚集到電容極板還是從電容極板釋放,都需要一個過程,也就是電容上的電荷值不會突變,根據(jù)公式1電容兩端的電壓也不會突變,而是隨著電荷Q的聚集/釋放過程而逐漸變化。比如電容兩側目前電壓分別為V1=1.2V,V2=0.8V,電容充電完成到達穩(wěn)態(tài),電容兩側壓差為0.4V,左側極板積聚正電荷,右側極板積聚負電荷,如圖 2所示。

圖 2 電容充電穩(wěn)定圖

如果電容V1側電壓瞬間增大到1.4V,電容啟動充電過程。根據(jù)電容兩端電壓不能突變原理,此時V2處的電壓會先升高到1.0V。由于電容為充電過程,V1積聚更多正電荷,V2積聚更多負電荷,釋放更多正電荷,致使V2的電壓下降,一直到0.8V。這時電容充電過程完成,再次進入平衡狀態(tài),此時電容兩側壓差達到0.6V。

圖 3 電容充電時的動態(tài)電壓變化

如果電容V1側電壓瞬間降低到1.0V,電容啟動放電過程。根據(jù)電容兩端電壓不能突變原理,此時V2處的電壓會先降低到0.6V。由于電容為放電過程,V1釋放更多正電荷,V2釋放更多負電荷,聚集更多正電荷,致使V2的電壓上升,一直到0.8V。這時電容放電過程完成,再次進入平衡狀態(tài),此時電容兩側壓差達到0.2V。

圖 4 電容放電時的動態(tài)電壓變化

通過上面的實例分析,可以看到交流信號可以通過電容的原因:如果V1為交流信號,在1.4V和1.0V之間不停的交替變化,那么只要電容充放電的時間足夠大,換句話說就是信號周期遠小于充放電時間,就可以把這種變化帶到V2側,V2就會在1.0V和0.6V之間不停的交替變化,從而實現(xiàn)了交流信號通過電容。這個在后續(xù)章節(jié)中有更詳盡的分析。

本質上,還是由于電路中不停的有電流(電荷的遷徙)流過,最終表現(xiàn)為電壓的變化。下面通過對于不同信號的分析,說明交流信號通過電容傳輸?shù)淖兓闆r。

假設一個交流信號V1,經過電容進行AC耦合傳輸。V1信號的直流偏置為1.2V,擺幅0.4V。經過電容傳輸后,得到信號V2。V2的直流偏置為V2offset=0.8V。

圖 5 AC耦合電路示意圖

4.信號從非直流平衡變?yōu)橹绷髌胶?/strong>

V1從常低變?yōu)榻涣?/p>

圖6 從常低電平到平衡信號的轉換

t1時刻:V0=1.0-0.8=0.2,V∞=1.4-0.8=0.6,電容壓差變化|V∞-V0|=0.4V。到達t2時,電容完成了時間為?t的充電過程,由于充電導致的V2電壓變化?V,即t2時刻V2=1.2-?V。

t2時刻:V0=1.4-(1.2-?V)=0.2+?V,V∞=1.0-0.8=0.2,電容壓差變化|V∞-V0|=?V。到達t3時,電容完成相同時間?t的放電過程,由于放電導致的V2電壓變化?V’,到t3時刻V2=0.8-?V+?V’。

結合第2小節(jié)中電容充放電時間的解釋,對于同一個電路,電容壓差變化(|V∞-V0|)越大,充放電的時間越短,或者說相同的時間內電容壓差變化(|V∞-V0|)越大,極板電壓變化(V2)越大。結合本例,在第一個?t間隔內,電容壓差變化0.4V,而第二個?t間隔內電容壓差變化?V,0.4>>?V,因此在相同的時間間隔?t內,?V大于?V’,也就是說充電量大于放電量。這就解釋了中的V2曲線的平均值不斷下降的原因。

V1從常高變?yōu)榻涣?/p>

圖 7 從常高電平到平衡信號的轉換

圖 7 從常高電平到平衡信號的轉換

t1時刻:V0=1.4-0.8=0.6,V∞=1.0-0.8=0.2,電容壓差變化|V∞-V0|=0.4V。到達t2時,電容完成了時間為?t的放電過程,由于放電導致的V2電壓變化?V,即t2時刻V2=0.4+?V。

t2時刻:V0=1.0-(0.4+?V)=0.6-?V,V∞=1.4-0.8=0.6,電容壓差變化|V∞-V0|=?V。到達t3時,電容完成相同時間?t的充電過程,由于充電導致的V2電壓變化?V’,到t3時刻V2=0.8+?V-?V’。

結合第2小節(jié)中電容充放電時間的解釋,對于同一個電路,電容壓差變化(|V∞-V0|)越大,充放電的時間越短,或者說相同的時間內電容壓差變化(|V∞-V0|)越大,極板電壓變化(V2)越大。結合本例,在第一個?t間隔內,電容壓差將變化0.4V,而第二個?t間隔內電容壓差變化?V,前者電容壓差變化遠大于后者,因此在相同的時間間隔?t內,?V大于?V’,也就是說放電量大于充電量。這就解釋了中的V2曲線的平均值不斷上升的原因。

5.信號為穩(wěn)定的直流平衡

第4小節(jié)中的信號,經過長時間的變化,總會有一個時刻在一個?t間隔內的充電量與放電量達到平衡,如圖 8所示。

圖 8 AC耦合傳輸直流平衡信號波形圖

t1時刻,由于前一個時間間隔內電容放電,V2=0.6+?V,則V0=1.0-(0.6+?V)=0.4-?V,V∞=1.4-0.8=0.6,電容壓差變化|V∞-V0|=0.2V+?V。到達t2時,電容完成了時間為?t的充電過程,由于充電導致的V2變化為?V’,則在t2時刻V2=1.0V+?V-?V’。

T2時刻:V0=1.4-(1.0V+?V-?V’),V∞=1.0-0.8=0.2V,電容壓差變化|V∞-V0|=0.2-?V+?V’,到達t3時,電容完成了時間為?t的放電過程,由于放電導致的V2變化為?V’(充電和放電達到平衡,在相同時間內電壓變化也相同),則在t3時刻V2=1.0-V0=0.6+?V-?V’+?V’=0.6+?V。

由于充電和放電達到平衡,因此在t1和t2時刻計算的電容壓差變化應該相等,即0.2V+?V=0.2-?V+?V’,即?V’=2?V。如果放大這個時間片段的話(夸張的畫),應該如圖 9所示。也就是說,在V1的每次升高或者降低變化時,電容都在進行充電或者放電過程,只不過充放電的時間與信號變化的時間比擬起來很長,以至于幾乎看不到充放電對V2信號電平的影響。

圖 9 AC耦合直流平衡信號局部放大

6.信號從直流平衡變?yōu)榉侵绷髌胶?/strong>

V1從交流變?yōu)槌5汀8鶕?jù)前兩節(jié)的分析,一旦V1變?yōu)榈碗娖剑娙菥蜁_始放電,由于V1沒有再變高的過程,放電會一直持續(xù),一直到電容重新達到平衡狀態(tài),也就是電容壓差最終穩(wěn)定在0.2V。

圖 10 V1變?yōu)槌5秃骎2的變化圖

V1從交流變?yōu)槌8摺8鶕?jù)前兩節(jié)的分析,一旦V1變?yōu)楦唠娖剑娙菥蜁_始充電,由于V1沒有再變低的過程,充電會一直持續(xù),一直到電容重新達到平衡狀態(tài),也就是電容壓差最終穩(wěn)定在0.6V。

圖 11 V1變?yōu)槌8吆骎2的變化圖

7.單端信號到差分信號

事實上,經常使用AC耦合的情形多為差分信號傳輸,那是由于不同標準電平的差分信號直流偏置會有差別,通常需要使用AC耦合進行直流偏置的隔離。對于差分信號,如果發(fā)送端直流不平衡時,在接收端又會是什么現(xiàn)象呢?

根據(jù)前面各小節(jié)的分析,得到差分信號的傳輸波形就是很簡單的了。章節(jié)4和章節(jié)6中均分析了兩種數(shù)據(jù)的波形,將這兩種數(shù)據(jù)分別定義為VP和VN,那么兩者相減就得到差分信號的波形了,分別如圖 12和圖 13所示。僅從波形上看,與單端信號差別不大,僅信號的擺幅比單端信號大了一倍而已。

圖 12 差分信號從交變電平到常電平

圖 13 差分信號從常電平到交變電平

8.信號非直流平衡時的問題

綜合上面的分析,如果信號出現(xiàn)非直流平衡,即常連0或者常連1的數(shù)量過多時,可能會造成兩個方面的問題:

(1)超過信號的判決門限而造成誤判

任何信號在接收端都會有一個判決門限,比如LVDS信號會有±100mV的門限要求,即Vdiff落在0±100mV內,接收端無法判斷接收數(shù)據(jù)位邏輯0還是邏輯1,可能造成誤判。從圖 12可以看出,如果發(fā)送端出現(xiàn)常連0或者常連1時,電容會過度充電或者過度放電,使接收端的電壓可能降低到判決門限(比如LVDS信號的±100mV)以內,造成誤判;從圖 13可以看出,發(fā)送端在常連0或者常連1后,如果出現(xiàn)變化bit,最開始的幾個周期這些信號在接收端有擺幅很小的時刻,如果同樣落在判決門限(比如LVDS信號的±100mV)以內,也會造成誤判。

(2)超過器件能承受的最大電壓損壞器件

從章節(jié)4可以看出,V1在常連0或者常連1后出現(xiàn)一個變化bit,V2會出現(xiàn)較大的上擺或者下擺(會到達1.2V或者0.4V),有可能會超過接收器件承受的最大電壓,造成器件的損害。

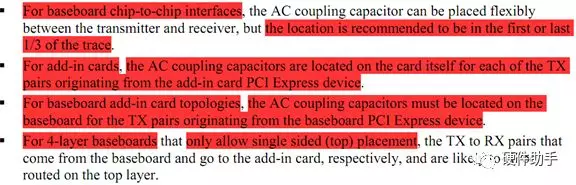

基于上述兩個問題的分析,得到AC耦合電路需要使用直流平衡的信號。當然直流平衡并不是要求信號如前面章節(jié)分析的0和1交替反轉的那樣,本文中使用這樣的信號僅為分析方便。實際使用中只要0和1的數(shù)量相等或者近似相等就可以了,出現(xiàn)連續(xù)的0或者連續(xù)的1不可避免,但只要不太多就可以了。比如8B/10B編碼,連續(xù)的“1”或“0”不超過5位,即每5個連續(xù)的“1”或“0”后必須插入一位“0”或“1”。

三、實踐情況

針對上述的理論分析,進行相應仿真。為了能夠更好的理解數(shù)字序列經過AC耦合通路后的波形,首先仿真脈沖信號經過電容后的波形變化,

1.脈沖信號

根據(jù)圖 5建立如圖 14所示仿真模型,信號源為階躍函數(shù),上升沿1ps,擺幅0.2V,經過一個電容得到信號out1。由于電容電壓的不可突變特性,在信號源in1的階躍過程中都會出現(xiàn)out1電壓先上升后下降到0.8V的過程,但如果電容值選擇不同,out1的變化速度也不同。下面仿真了三種不同電容值時階躍響應曲線。

圖 14 階躍仿真模型

1.1充電時間短(15ps)

選擇電容C=0.1pF,計算電容的充電時間約為3RC=15ps,而信號的上升沿為1ps,這兩個時間相差不多。根據(jù)仿真波形圖 15所示,由于充電時間很短,導致out1的電平在瞬間沒有上升到1.0V。

圖 15 C=0.1pF仿真波形

1.2充電時間中等(15ns)

選擇電容C為0.1nF,此時電容的充電時間約為3RC=15ns。而信號的上升沿為1ps,相差不多。在階躍信號開始時,out1可以到達1.0V,并且在維持較短的一段時間開始下降,仿真波形分別如圖 16和圖 17所示。

圖 16 C=0.1nF仿真波形(仿真時間500ps)

圖 17 C=0.1nF仿真波形(仿真時間15ns)

1.3充電時間長(15us)

選擇電容C為0.1uF,此時電容的充電時間約為3RC=15us,而信號的上升沿為1ps,相差非常大。由于充電時間過長,在很長一段時間內(比如15ns內)out1沒有明顯變化,仿真波形分別如圖 18和圖 19所示。

圖 18 C=0.1uF仿真波形(仿真時間15us)

圖 19 C=0.1uF仿真波形(仿真時間15ns)

2.DC平衡數(shù)字序列

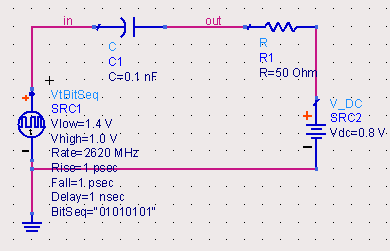

將仿真模型的信號源更換為DC平衡的bit序列,序列頻率為2620MHz(周期380ps),擺幅0.4V,直流偏置1.2V,同樣針對三種電容值進行仿真。

圖 20 DC平衡數(shù)據(jù)源仿真模型

2.1充放電時間短

仿真模型的電容C為0.1pF,充放電時間15ps。而bit序列的周期為380ps,半個周期為190ps,也就是說在信號的半個周期內,電容很快完成了充電/放電過程,out波形不能維持在固定的高電平或者低電平。最終仿真波形如圖 21所示,這個電容值不適合DC平衡信號的傳輸。

圖 21 C=0.1pF仿真波形

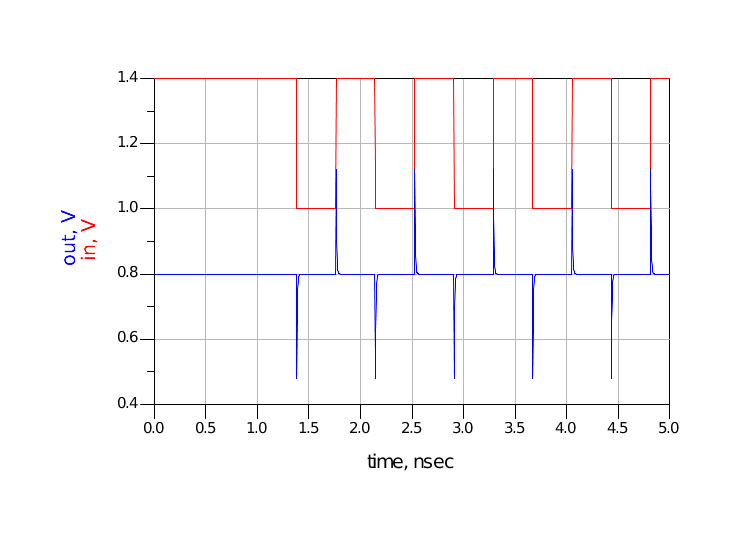

2.2充放電時間中等

仿真模型的電容C為0.1nF,充放電時間15ns。而bit序列半個周期為190ps,這個時間差距中等,最終仿真波形如圖 22所示。out波形到達正常(直流偏置為0.8V)大約花了15ns的時間。

圖 22 C=0.1nF仿真波形

2.3充放電時間長

仿真模型的電容C為0.1uF,充放電時間15us。而bit序列半個周期為190ps,這個時間差距還是非常大的,也就是說在信號半個周期內,電容充電/放電過程進行的非常緩慢,最終仿真波形如圖 23所示。out波形到達正常(直流偏置為0.8V)大約花了15us的時間,在這三種情形中是最長的一個。

圖 23 C=0.1uF仿真波形

3.DC非平衡數(shù)字序列

仍然使用上一節(jié)中的仿真模型,將發(fā)送bit序列更改為“11111111111111111111111111111111111111111111111111111111111111110”形式的非DC平衡序列,電容選擇0.1nF。由于“0”的數(shù)量較少,導致電容放電時間短,形成圖 24所示的波形,與第二章中的分析一致。這種信號在接收端就可能造成器件損壞或者接收判決錯誤。

圖 24 非DC平衡信號仿真波形a

將發(fā)送bit序列更改為“11111111111111111111111111111111111111111111111111111111111111110101010101010101010101”形式的非DC平衡序列,電容仍選擇0.1nF,out的波形如圖 25所示。

圖 25 非DC平衡信號仿真波形b

四、總結

通過本文的分析和仿真,從電容充放電的角度,比較直觀的解釋了非DC平衡信號不能使用AC耦合傳輸?shù)脑颉M瑫r在分析過程中,我們可以得到以下進一步引申的結論:

1.隔直電容的選擇與信號頻率有關。如果信號的頻率較低,隔直電容不能選擇的太小(充放電時間太小),以防止出現(xiàn)圖 15所示的情形,使傳輸波形失真;

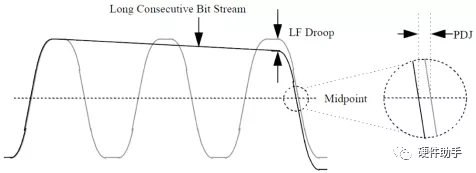

2.非DC平衡信號,經過AC耦合傳輸,信號眼圖一般不會閉合,但眼圖的中心電平會有偏移,眼皮變厚,眼高也會變小。

結論1根據(jù)上述章節(jié)的分析以及仿真波形顯而易見;結論2進一步闡述如下:

結合第二章中的分析以及圖 24和圖 25的仿真波形,可以看到AC耦合后的信號會經歷一個擺動調整的過程,從最原始的波形向偏置為0.8V調整。如果信號一直在這個區(qū)間內調整,那么輸出信號眼圖將如圖 26所示,其中紅框為非DC平衡信號經過AC耦合后的眼圖(最壞情況),藍色為DC平衡信號經過AC耦合后的眼圖(眼高為擺幅,眼中心為直流偏置V offset )。如果信號源為圖 24使用的源,那么AC耦合后的眼圖與圖 26中的黑色框類似,眼圖中心會達到V L ;如果信號源為圖 25使用的源,那么AC耦合后的眼圖將介于黑框和紅框之間。

圖 26 非DC平衡信號經過AC耦合后的眼圖分析

-

接收器

+關注

關注

14文章

2458瀏覽量

71800 -

仿真器

+關注

關注

14文章

1016瀏覽量

83644 -

耦合器

+關注

關注

8文章

718瀏覽量

59636 -

電容充放電

+關注

關注

0文章

94瀏覽量

5829 -

PRBS

+關注

關注

0文章

10瀏覽量

2593

發(fā)布評論請先 登錄

相關推薦

lcd驅動程序,分頻電路為何必須是分好多次才可以

AC耦合電容的選取

關于交流耦合和直流恢復知識解析

邏輯電平中邏輯互連的AC耦合電容

頻率計的交流耦合和直流耦合的區(qū)別_示波器DC/AC耦合設置及影響

AC耦合為何必須使用直流均衡信號?

AC耦合為何必須使用直流均衡信號?

評論