?

雖然RISC-V 架構還不完善,在諸如安全、虛擬化架構、IOMMU/SMMU、中斷控制架構、RAS(Reliability,Availability and Serviceability)等方面還剛起步,在代碼密度(code size)、虛擬內存管理、原子操作效率等方面也還存在一些缺陷,但這不會妨礙 RISC-V 架構的長遠向好發展,因為其開源的本質不曾改變。 回顧Linux 內核的發展歷史,在 Linux 內核之前,IBM 的 Unix 收費操作系統無論在穩定性和用戶體驗上都是非常成功的,而相比之下剛出道的 Linux 內核無論在穩定性以及用戶體驗上都比較糟糕,但是由于 Linux 內核的開源屬性迅速在 5 年時間內(1991 年到 1996 年)吸引了超過 350 萬開發者的使用。 經過30年的發展,Linux 操作系統(基于 Linux 內核開發的各種操作系統)已經成為世界上最主流的操作系統之一(Windows 主要在桌面機,IOS/安卓主要在智能手機和平板電腦),無論在服務器、云計算以及嵌入式領域基本已是 Linux 內核的天下。 RISC-V 和 X86、ARM 的競爭完全是不同維度的競爭,他們三個分別是全球處理器技術演進在不同階段的產物,而基本可以確定的是未來三種架構會長期共存,只是應用的側重領域有所不同罷了。

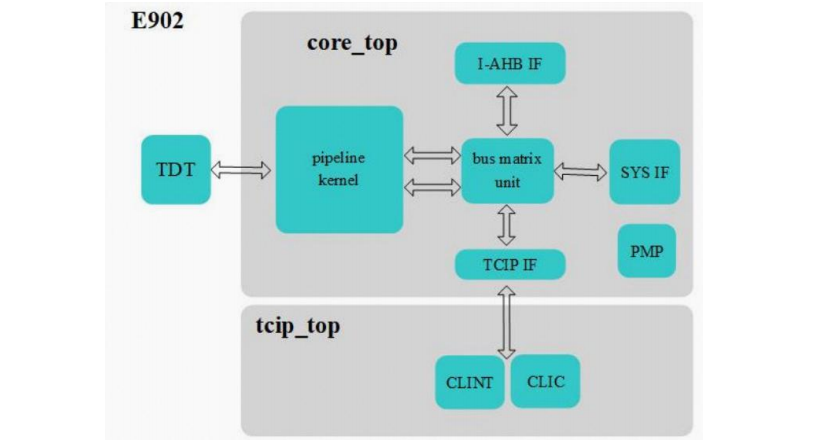

入門級微控制器:E902

玄鐵 E902 采用 2 級極簡流水線并對執行效率進行了增強,典型工作頻率>150MHz,是首款支持硬件安全擴展技術的 RISC-V 處理器。可以應用在對功耗和成本極其敏感的IoT、MCU 等場景。

E902 處理器采用 2 級流水線結構:取指和執行。指令取指階段主要負責從內存中獲取指令;指令執行階段主要負責指令譯碼、執行和回寫。

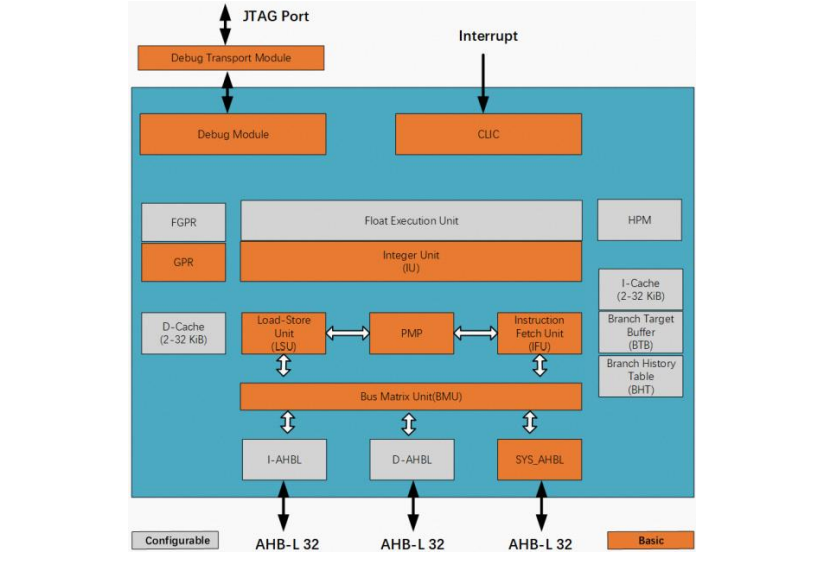

高能效微控制器:E906

玄鐵 E906 采用 5 級按序流水線,典型工作頻率>1GHz,可選性能優異的單精度浮點單元以及標量 DSP 計算單元。可以應用在無線接入、音頻、中高端 MCU、導航等場景。

E906 處理器采用 5 級流水線結構:取指、譯碼、執行、內存訪問、寫回。 ●取指階段,訪問指令 Cache 或者總線,獲取指令,同時訪問 BTB,發起 0 延時跳轉。 ●譯碼階段,訪問動態分支預測器和返回棧,發起分支的預測跳轉,同時進行指令譯碼,讀取寄存器堆,處理數據相關性和數據前饋。 ●執行階段,完成單周期整型計算指令和多周期乘除法指令的執行、存儲/加載指令地址計算和跳轉指令處理。其中,整型計算包括普通的算術指令和邏輯指令。 ●內存訪問階段,利用執行階段產生的存儲/載入指令的目標地址訪問數據 Cache 或者總線。 ●寫回階段,將指令執行結果寫回寄存器堆。 E906 設計有片上緊耦合的 IP 接口和多條 AHB-Lite 的總線接口。片上緊耦合的 IP 接口集成矢量中斷控制器(CLIC),支持中斷嵌套。外部中斷源數量最高可配置 240 個,中斷優先級支持 4/8/16/32 級可配置。

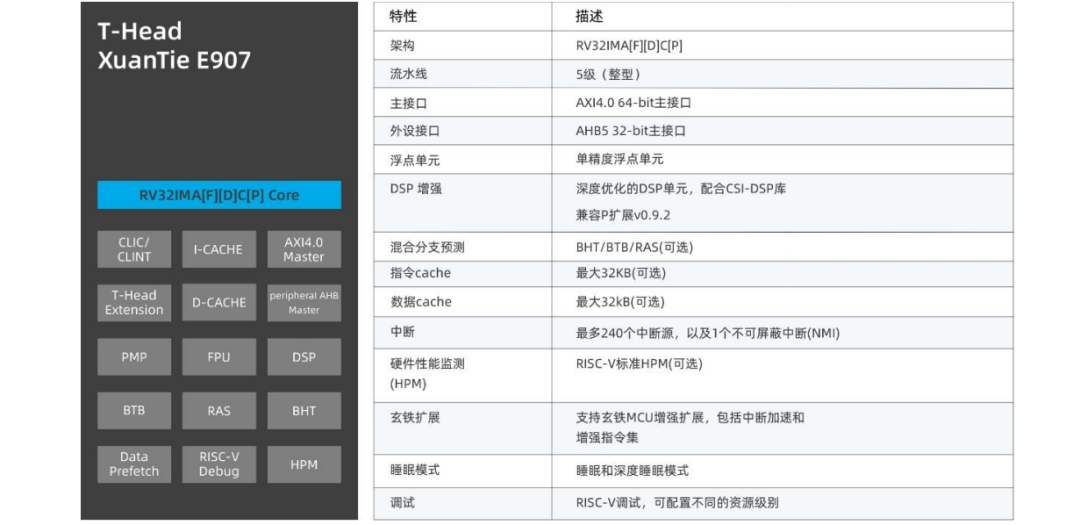

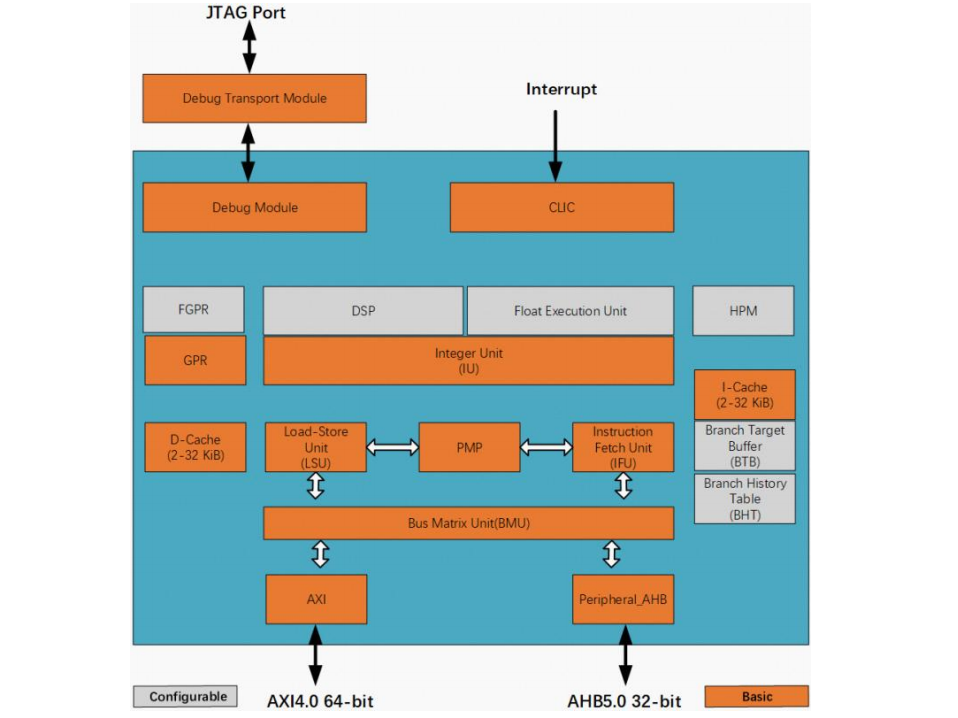

計算增強型微控制器:E907

玄鐵 E907 采用 5 級按序流水線,典型工作頻率>1GHz,是玄鐵 MCU 處理器中的性能最高的處理器核,可選配高性能浮點以及 DSP 計算單元,同時支持 TCM 擴展以及中斷加速技術以進一步提升實時性。可以應用在語音入口 MCU、TWS、MPU、多模無線接入等場景。

E907 處理器采用 5 級流水線結構:取指、譯碼、執行、內存訪問、寫回。 ●取指階段,訪問指令 Cache 或者外部總線,獲取指令,同時訪問 BTB,發起 0 延時跳轉。 ●譯碼階段,訪問動態分支預測器和返回棧,發起分支的預測跳轉,同時進行指令譯碼,讀取寄存器堆,處理數據相關性和數據前饋。 ●執行階段,完成單周期整型計算指令和多周期乘除法指令的執行、存儲/加載指令地址計算和跳轉指令處理。其中,整型計算包括普通的算術指令和邏輯指令。 ●內存訪問階段,利用執行階段產生的存儲/載入指令的目標地址訪問數據 Cache 或者外部總線。 ●寫回階段,將指令執行結果寫回寄存器堆。 E907 設計有片上緊耦合的 IP 接口和兩條主設備總線接口。片上緊耦合的 IP 接口集成矢量中斷控制器(CLIC),支持中斷嵌套。外部中斷源數量最高可配置 240 個,中斷優先級支持 4/8/16/32 級可配置。

高能效應用處理:C906

玄鐵 C906 采用 5-8 級變長流水線,典型工作頻率>1GHz,標配內存管理單元,可運行 Linux 等操作系統,并可選性能優異的單精度浮點和矢量運算單元。可以應用在消費類 IPC、多媒體、消費類電子等場景。

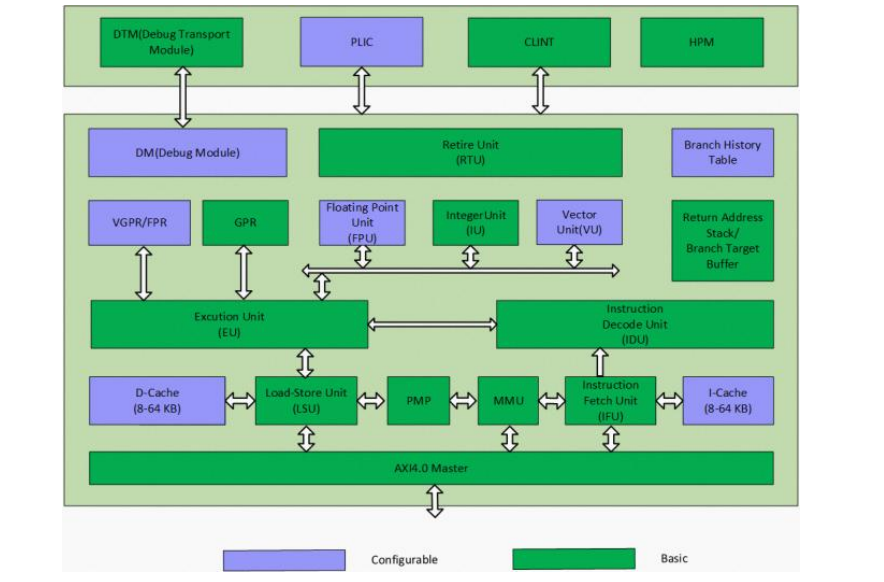

C906 核內子系統主要包含:指令提取單元(IFU)、指令譯碼單元(IDU)、整型執行單元(IU)、浮點單元(FPU)、可配的矢量執行單元(VPU)、存儲載入單元(LSU)、指令退休單元(RTU)、虛擬內存管理單元(MMU)、物理內存保護單元(PMP)、主設備接口單元(AXI Master IF)等。

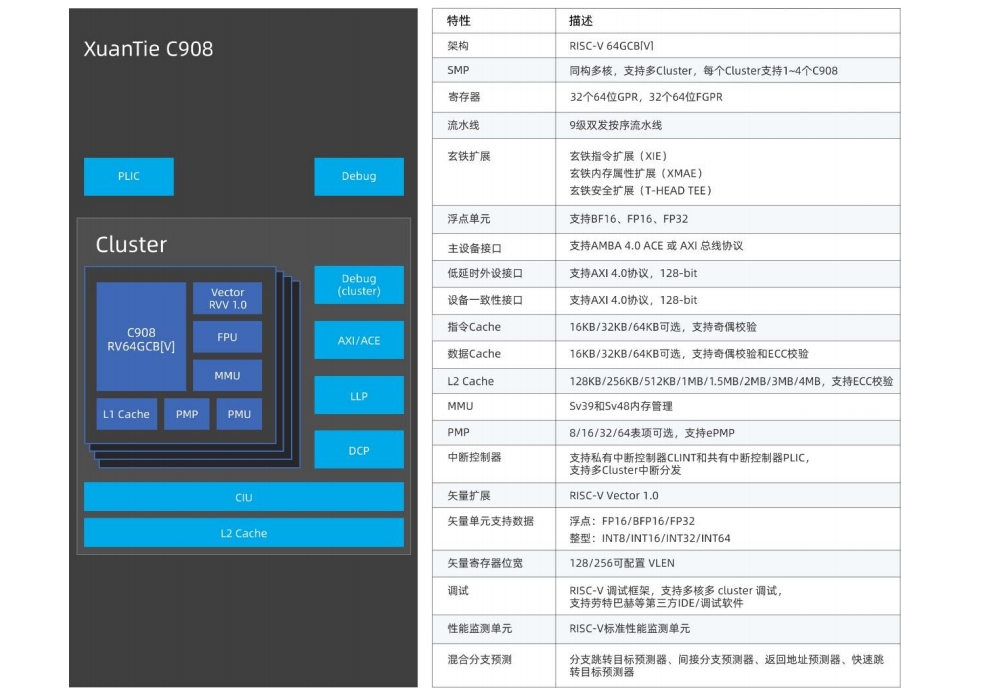

兼容 64 位高能效處理:C908

玄鐵 C908 采用 9 級雙發按序流水線,典型工作頻率>2GHz,通過指令融合技術進一步提升流水線效率,實現了卓越的能效比。兼容 RVA22 標準,同時兼容 RISC-V 最新Vector1.0 標準以進一步提升 AI 算力。

C908 核內子系統主要包含:指令提取單元(IFU)、指令執行單元(IEU)、矢量浮點執行單元(VFPU)、存儲載入單元(LSU)、虛擬內存管理單元(MMU)和物理內存保護單元(PMP)。

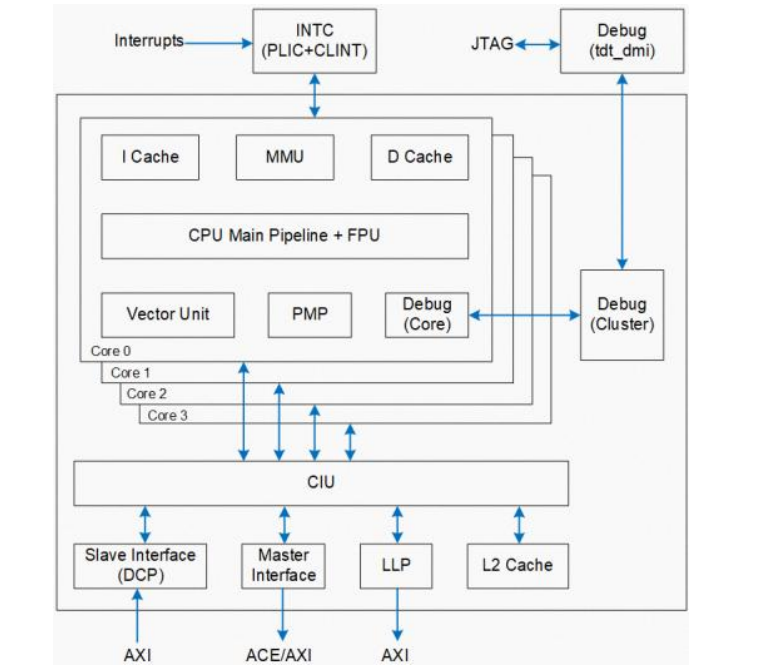

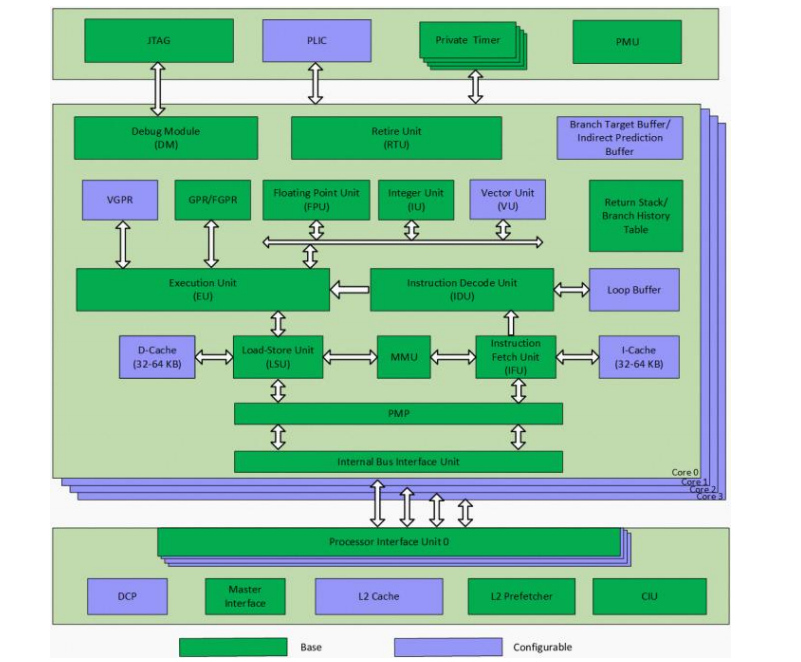

高性能應用處理:C910

玄鐵 C910 采用 12 級多發亂序流水線,典型工作頻率>2.5GHz,是首款實現規模化量產的高性能亂序 RISC-V 處理器。采用 3 發射、8 執行的深度亂序執行架構,針對算術運算、內存訪問以及多核同步等方面進行了增強。

C910 核內子系統主要包含:指令提取單元(IFU)、指令譯碼單元(IDU)、整型執行單元(IU)、浮點單元(FPU)、存儲載入單元(LSU)、指令退休單元(RTU)、虛擬內存管理單元(MMU)和物理內存保護單元(PMP)。 C910 多核子系統包含:數據一致性接口單元(CIU)、二級高速緩存、主設備接口單元、可配置的 AXI4.0 設備一致性接口(DCP,Device Coherence Port)、平臺級中斷控制器(PLIC)、計時器和自定義多核單端口調試框架。

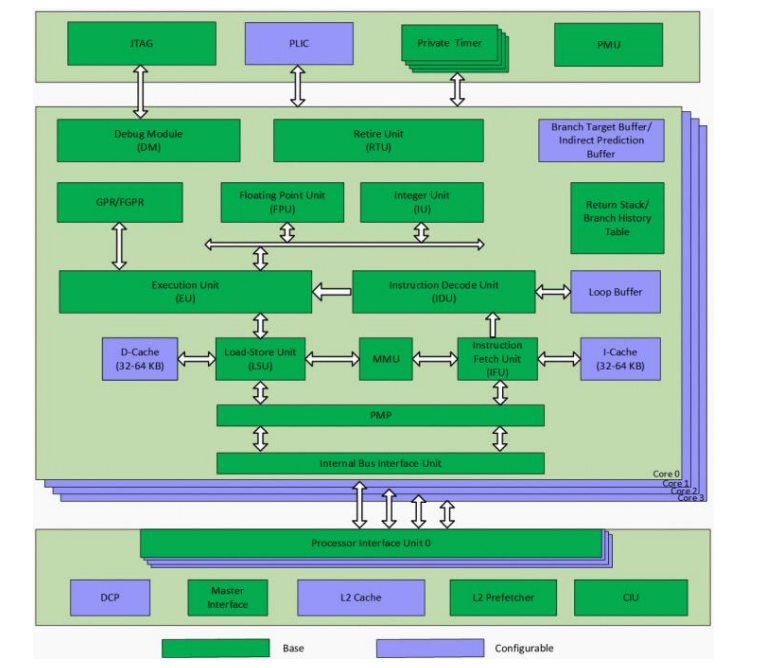

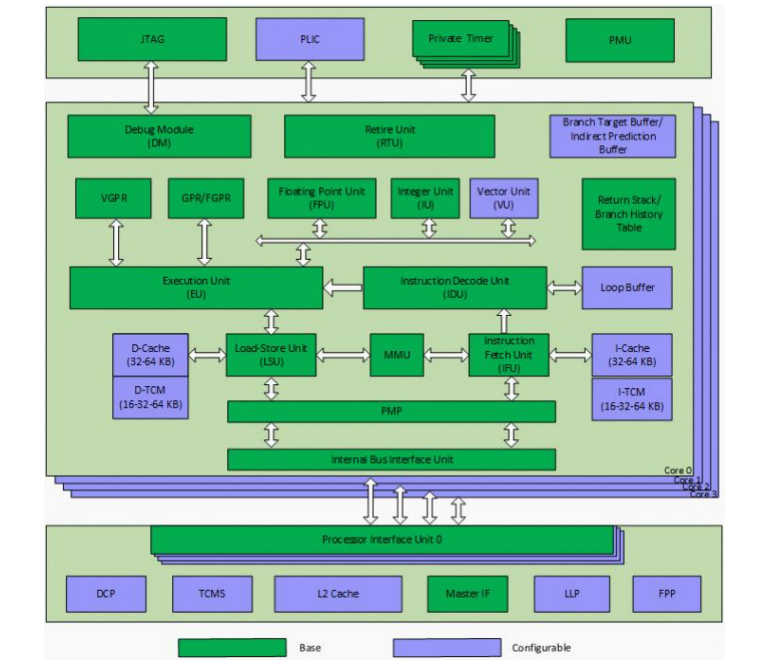

AI 加速引擎:C920

玄鐵 C920 采用 12 級多發亂序流水線,典型工作頻率>2.5GHz,標配單精度浮點單元,并可進一步選配高性能亂序矢量運算單元。同時具備出色的訪存能力,支持高性能數據預取技術。可以應用在有高并發算力要求的人工智能、自動駕駛等場景。

C920 核內子系統主要包含:指令提取單元(IFU)、指令譯碼單元(IDU)、整型執行單元(IU)、浮點單元(FPU)、矢量執行單元(VU)、存儲載入單元(LSU)、指令退休單元(RTU)、虛擬內存管理單元(MMU)和物理內存保護單元(PMP)。 C920 多核子系統包含:數據一致性接口單元(CIU)、二級高速緩存、主設備接口單元、可配置的 AXI4.0 設備一致性接口(DCP,Device Coherence Port)、平臺級中斷控制器(PLIC)、計時器和自定義多核單端口調試框架。

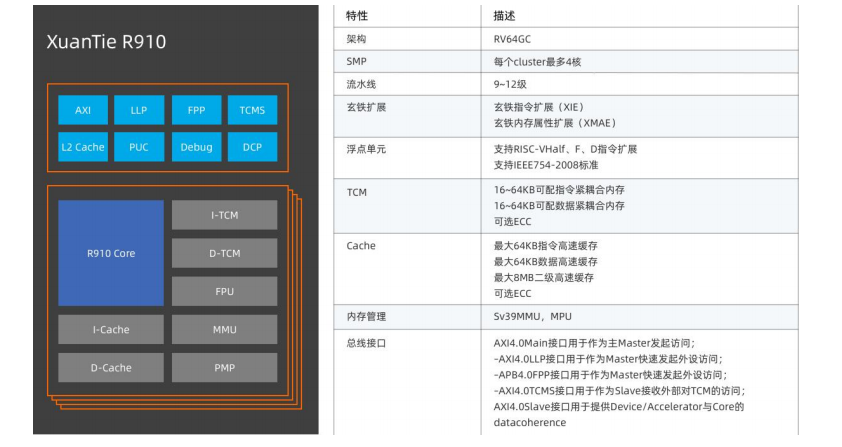

可靠實時增強:R910

玄鐵 R910 用 12 級多發亂序流水線,典型工作頻率>2.5GHz,同時支持 Cache 以及TCM 存儲架構,各級片上存儲支持校驗糾錯以提升可靠性,可進一步選配快速外設接口以及一致性外設接口,從而大幅提升系統實時性。可以應用在對實時性及算力有高要求的企業級 SSD,網絡通信等場景。

R910 核內子系統主要包含:指令提取單元(IFU)、指令譯碼單元(IDU)、整型執行單元(IU)、浮點單元(FPU)、存儲載入單元(LSU)、指令退休單元(RTU)、虛擬內存管理單元(MMU)和物理內存保護單元(PMP)。 R910 多核子系統包含:數據一致性接口單元(CIU)、二級高速緩存、主設備接口單元、可配置的快速外設訪問接口(LLP)、可配置的 APB 主設備接口(FPP)、可配置的緊耦合內存訪問接口(TCMSP)、可配置的 AXI4.0 設備一致性接口(DCP,Device Coherence Port)、平臺級中斷控制器(PLIC)、計時器和自定義多核單端口調試框架。

-

操作系統

+關注

關注

37文章

6737瀏覽量

123190 -

硬件

+關注

關注

11文章

3252瀏覽量

66111 -

RISC-V處理器

+關注

關注

0文章

80瀏覽量

9991

原文標題:玄鐵RISC-V處理器入門及實戰

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RISC-V處理器生態建設的實踐

RISC-V處理器生態建設的實踐

評論