通過將吸電流負LDO配置為正電壓灌電流,可以構建一個低壓電源(1.3V)來端接PECL邏輯線路。

高速電信中使用的正發射極耦合邏輯(PECL)需要奇數電源電壓:正VCC為+3.3V,終止電壓(VTT)等于VCC -2V = +1.3V。VTT 電源相對于 VCC 進行調節,并且必須能夠吸收電流。

大多數正低壓差(LDO)穩壓器不能吸收電流。負LDO是為此目的而設計的,但通常提供負電壓。

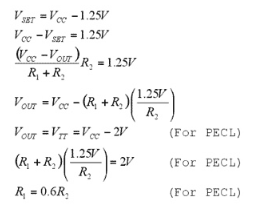

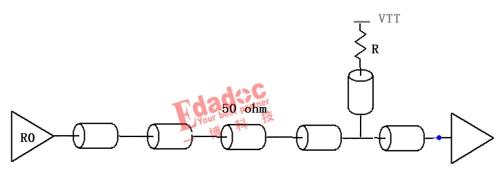

圖1所示為針對正電壓操作而修改的吸電流負LDO。GND 引腳連接到 VCC,IN 連接到地。這些連接允許負LDO作為正電壓吸收器工作,其中VSET上的電壓等于VCC -1.25V:

圖1.所示連接使負輸出LDO(具有固有的電流吸收能力)能夠產生正輸出電壓。

輸出電壓相對于VCC進行調節。該特性非常適合PECL端接應用,因為它需要輸出電壓來跟蹤VCC電源。最大輸出電流受內部保護電路(約400mA)和封裝功耗額定值(約550mW)的限制。對于需要更高輸出電壓或更高電流(或兩者兼而有之)的應用,您可以添加串聯二極管來耗散部分功率(圖 2)。您可以根據需要添加任意數量的二極管來耗散功率,但OUT(引腳5)處的電壓必須保持至少高于地電位300mV(IN,引腳2)。

圖2.要在超過IC1內部或封裝功耗額定值的電壓或電流下工作圖1電路,請如圖所示添加功耗二極管。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17003瀏覽量

247209 -

穩壓器

+關注

關注

24文章

4140瀏覽量

92797 -

ldo

+關注

關注

35文章

1811瀏覽量

152524 -

PECL

+關注

關注

0文章

321瀏覽量

14275

發布評論請先 登錄

相關推薦

端接電阻沒選對,DDR顆粒白費?

用兩個LDO分別做數字模擬電源的隔離,LDO的輸出端接電壓會對其輸入端有影響嗎?

高速PCB的終端端接

讓你徹底擺脫抖動和時鐘質量變低的4種端接方式

不加端接電阻的快樂,你們絕對想象不到!

不加端接電阻的快樂,你們絕對想象不到

DDR存儲器端接電源靈活適用于2.5V和1.8V存儲器系統

改進的LDO吸收PECL端接電流

改進的LDO吸收PECL端接電流

評論