引言

CMOS和MEMS制造技術,允許相對于其他薄膜選擇性地去除薄膜,在器件集成中一直具有很高的實用性。這種化學性質非常有用,但是當存在其他材料并且也已知在HF中蝕刻時,這就成了問題。由于器件的靜摩擦、緩慢的蝕刻速率以及橫向或分層膜的蝕刻速率降低,濕法化學也會有問題。

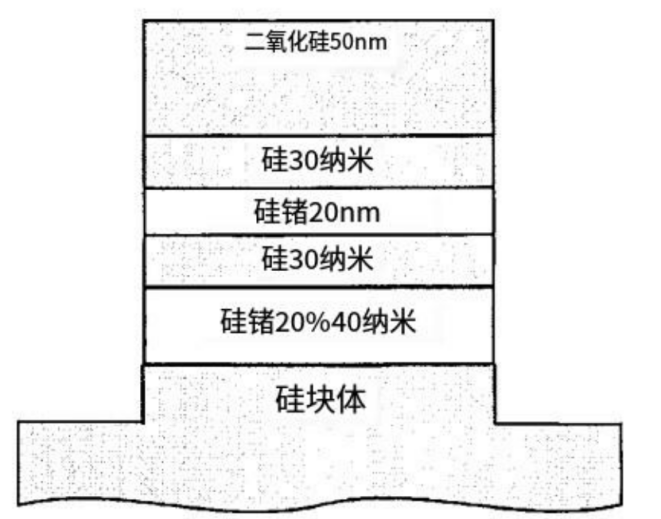

通過具有各向同性氣相蝕刻化學的附加優點,可以實現硅層的高蝕刻率。這種技術要求在氟中可蝕刻的材料不使用高選擇性薄膜,如二氧化硅,或光刻膠,或植入不可蝕刻的摻雜劑。

英思特通過使用NF3和NO的更簡單的蝕刻化學來研究CDE中Ge和Si之間的蝕刻選擇性,目的是將Ge用作光學或MEMS器件的釋放層。通過利用上游等離子體中的NF3和Ar,可以產生大量的氟自由基,從而用于ge和Si蝕刻,而不會增加碳化學的復雜性。

實驗與討論

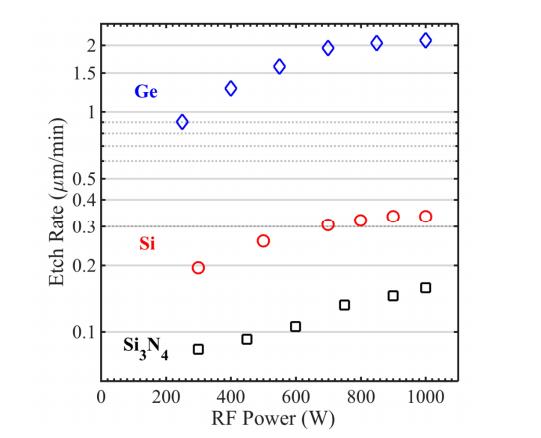

英思特通過改變RF等離子體功率來進行CDE蝕刻的初始表征。在CDE中用400sccm的Ar、75sccm的NF3、70Pa的壓力在不同的RF功率下進行各向同性蝕刻;硅晶片和硅晶片上的氮化硅被蝕刻30秒,硅晶片上的鍺被蝕刻8秒(圖1)。接近1000W時,氟自由基出現飽和狀態,鍺、硅和氮化物的蝕刻速率分別達到2.1μm/min、320納米/分鐘和158納米/分鐘。

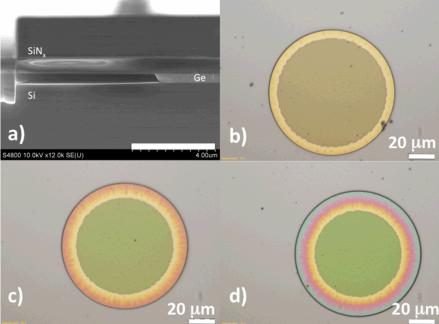

在覆蓋蝕刻速率測量之后,我們利用結構ICP RIE刻蝕到硅中的晶圓來研究CDE中Ge的橫向蝕刻特性。其結構由SiNx(400nm)/Ge(400nm)/Si的薄膜堆制成,并蝕刻1.7μm,總柱高度為2.5μm。然后在CDE中橫向蝕刻15、30和45秒,在直徑100m的柱上光學測量后蝕刻Ge(圖2)。

圖2:夾在SiNx和晶體硅襯底之間的橫向蝕刻的光學測量

結論

干法蝕刻釋放層是集成光子學和MEMS應用的基本工具,這項工作詳細說明了在硅和氮化硅存在下鍺薄膜的各向同性干法刻蝕。英思特通過使用三氟化氮和Ar的化學方法,將Ge、Si、SiNx和晶體硅的覆蓋層以及圖案CVD層進行各向同性蝕刻。

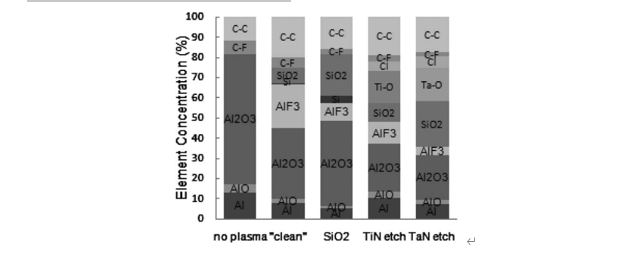

隨著等離子體功率的增加,蝕刻速率增加;使用O2降低,氧化暴露的Ge和Si受到抑制,但不阻止GeF4和四氟化硅的形成。這項工作不是將N2和O2注入等離子體,而是通過將NO直接注入處理室,來產生基本的N和O自由基。

英思特研究發現,Si和SiNx的蝕刻速率增加,但由于氧-氮化物或氮化物鍺的形成,導致蝕刻發生延遲。在純氟蝕刻化學存在的情況下,我們幾乎沒有觀察到α-Si、Si襯底或氮化硅的蝕刻,并且Ge蝕刻顯著高于覆蓋Ge薄膜蝕刻速率。對于暴露的硅和氮化硅,除了輕微延遲蝕刻前部和輕微增加蝕刻速率外,添加NO在蝕刻方面沒有任何優勢。

江蘇英思特半導體科技有限公司主要從事濕法制程設備,晶圓清潔設備,RCA清洗機,KOH腐殖清洗機等設備的設計、生產和維護。

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27011瀏覽量

216285 -

等離子體

+關注

關注

0文章

114瀏覽量

14207 -

蝕刻

+關注

關注

9文章

413瀏覽量

15346

發布評論請先 登錄

相關推薦

金屬蝕刻殘留物對對等離子體成分和均勻性的影響

等離子體蝕刻和沉積問題的解決方案

雷尼紹測頭為什么具有各向同性

PCB電路板等離子體切割機蝕孔工藝技術

PCB板制作工藝中的等離子體加工技術

微波標量反射計可測量大范圍的等離子體密度

TDK|低溫等離子體技術的應用

等離子體應用

常見的各向同性濕法刻蝕的實際應用

真空等離子清洗機的制造商正在引入氧和氫等離子體來蝕刻石墨烯

鋁等離子體蝕刻率的限制

鍺化硅(SiGe)和硅(Si)之間的各向同性和選擇性蝕刻機制

鍺、硅、SiNx薄膜的各向同性等離子體蝕刻

鍺、硅、SiNx薄膜的各向同性等離子體蝕刻

評論