(1)異步復位同步釋放的優勢

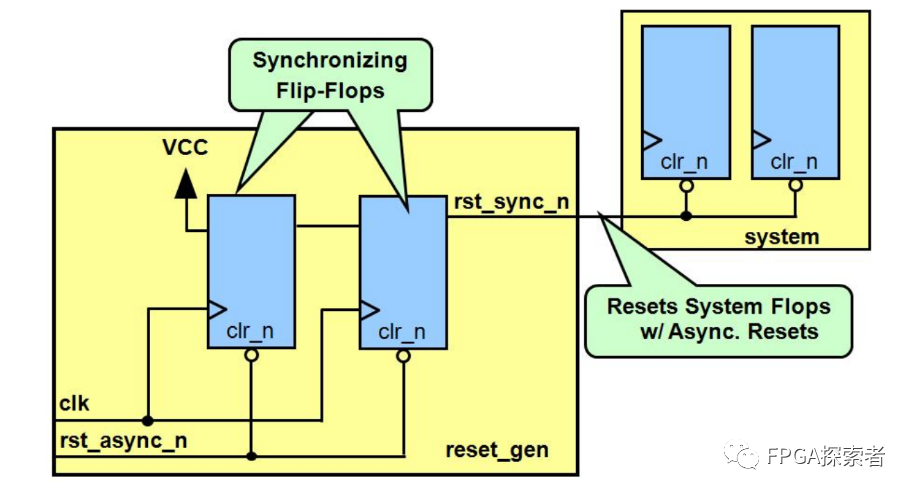

(2)D 觸發器搭建電路

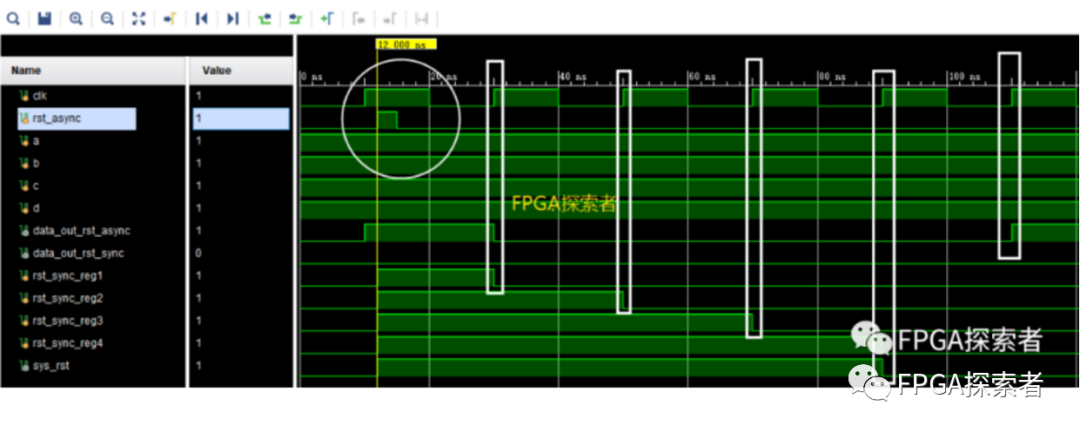

使用 2 個帶異步復位的寄存器,D端輸入邏輯 1(VCC)。

當異步復位無效(rst_async_n = 1)時,同步后的復位信號 rst_sync_n 也為 1;

當異步復位有效(rst_async_n = 0)時,同步后的復位信號 rst_sync_n 立刻為 0,即實現了“異步復位”,但是會在時鐘上升沿來臨時恢復為 1,實現“同步釋放”;

第一級觸發器的輸入 D 接電源,即高電平1’b1。

第一級觸發器的輸出,很可能存在亞穩態,使用兩級觸發器做同步。

(3)Verilog 代碼

reg rst_n_1 = 1'b1;

reg rst_n_2 = 1'b1;

always @ (posedge clk or negedge rst_async_n)

begin

if( !rst_async_n ) begin

rst_n_1 <= 1'b0;

rst_n_2 <= 1'b0;

end

else begin

rst_n_1 <= 1'b1;

rst_n_2 <= rst_n_1;

end

end

assign rst_sync_n = rst_n_2;

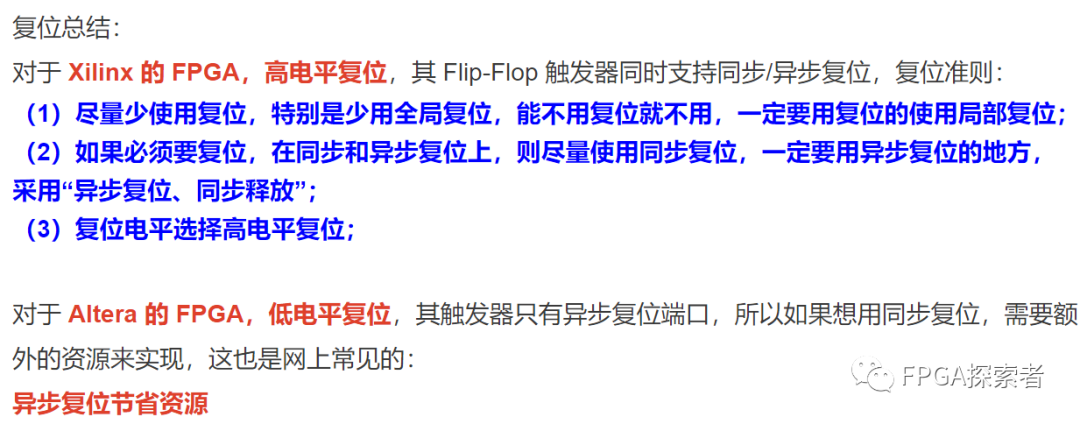

總結

針對 Altera 的 FPGA ,沒有做其他資源消耗時的具體考證,僅從上述來看,確實能夠節省一些資源。

針對 Xilinx 的 FPGA :

(1)對于同一個觸發器邏輯,因為同時支持異步和同步復位,所以異步復位并不會節省資源;

(2)對于其他的資源,比如 DSP48 等,同步復位更加節省資源。

首先,對于 DSP48,其內部還帶有一些寄存器(只支持同步復位),如果使用異步復位,則會額外使用外部 Slice 中帶異步復位的寄存器,而使用同步復位時,可以利用 DSP48 內部的寄存器;

Xilinx 的 FPGA,對于 DSP48、BRAM 資源,使用同步復位比異步復位更節省資源。

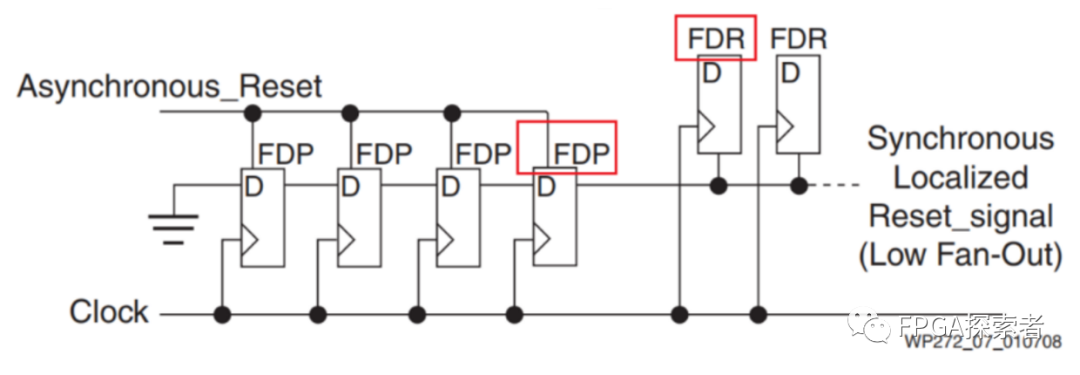

對于【高電平復位】,使用異步復位同步釋放,則第一個寄存器的 D 輸入是 0,這里使用了 4 個觸發器打拍同步。

(參考 Xilinx 白皮書 WP272,【FPGA探索者】公眾號回復【wp272】獲取)。

異步復位同步釋放,既能很快的檢測到復位信號,不需要復位保持超過一個時鐘周期,又能解決釋放時的亞穩態問題(降低亞穩態發生的概率)。

-

寄存器

+關注

關注

31文章

5322瀏覽量

120019 -

D觸發器

+關注

關注

3文章

164瀏覽量

47863 -

Vcc

+關注

關注

2文章

305瀏覽量

35855 -

異步復位

+關注

關注

0文章

47瀏覽量

13300 -

FPGA開發板

+關注

關注

10文章

122瀏覽量

31485

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

異步復位異步釋放會有什么問題?FPGA異步復位為什么要同步釋放呢?

異步復位同步釋放問題解析

異步復位同步釋放問題解析

評論