在時鐘電路的設計中,存在 jitter 和 skew 問題。請解釋下:

- 什么是 jitter,什么是 skew?

- 在 pre-CTS 的時序約束中,setup 和 hold 的 clock uncertainty 分別由什么組成。

解析:

(1)名詞解釋

jitter,時鐘抖動;

skew,時鐘偏斜;

uncertainty,時鐘不確定性,包括 jitter 和 skew;

Clock Tree Synthesis,時鐘樹綜合,簡稱CTS;

(2)具體分析

clock 時鐘有不確定性(clock uncertainty),其中包括 clock jitter(時鐘抖動)和 clock skew(時鐘偏斜)。

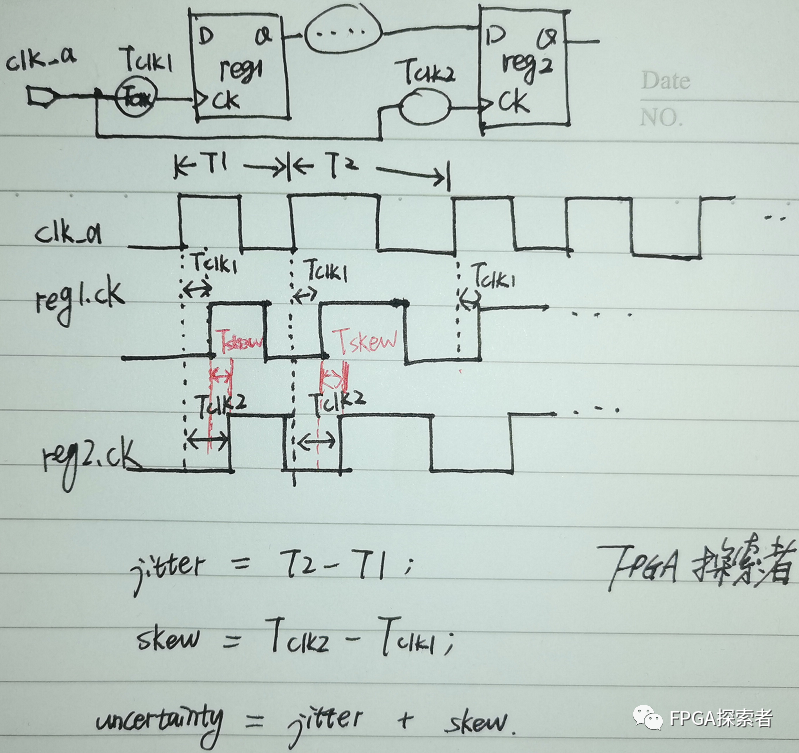

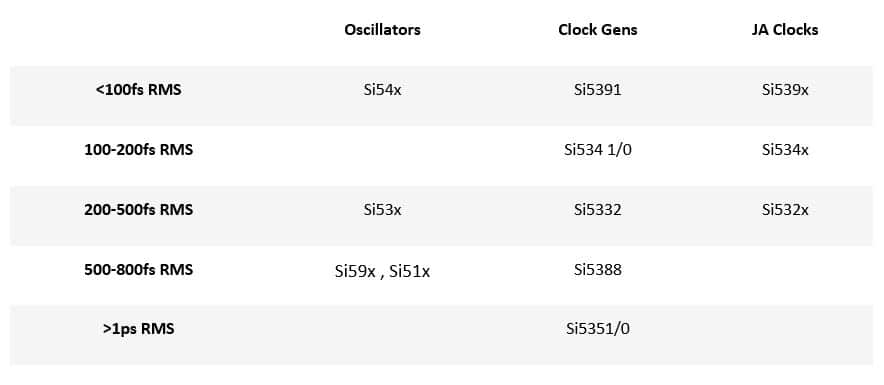

clock jitter ,抖動來自時鐘的產生源,比如晶振、PLL,可以理解為 PLL jitter, 是頻率上的不確定性,是頻偏,即針對這一個時鐘,前后周期在變 ,jitter = T2 - T1(或者也存在占空比上的不確定性);

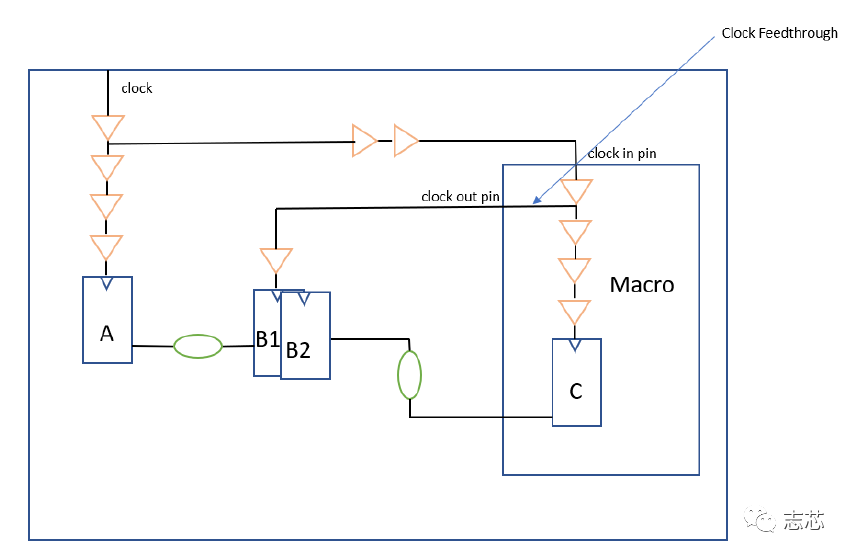

clock skew ,偏斜來自時鐘樹的延遲,是 一個時鐘到達不同時序邏輯單元的時刻不同 ,但是周期是不變的, 存在相位差,是相偏 ,可以理解為 clock tree skew, 是相位上的不確定性 ;

對于 jitter,是晶振本身或者 PLL 電路帶來的,受到溫度等影響,有一定的振蕩頻率偏移,設計者可以更換穩定性更好的晶振來降低 jitter;

對于 skew,是時鐘樹上的延遲,可以通過插入 buffer 來改變,時鐘樹綜合布線后,skew 值確定;

對于同****一個時鐘到達不同的時序邏輯單元 :

pre-CTS 預布局階段 ,時鐘樹 clock tree 還沒有綜合,所以 clock tree 的 skew 還不確定,在分析 setup 和 hold 的時候都需要考慮 skew;

對于 setup ,由于發射沿和捕獲沿是相鄰的兩個沿,所以 要考慮 skew,也要考慮 jitter ;

對于 hold ,由于發射沿和捕獲沿是同一個沿,所以 只要考慮 skew,不需要要考慮 jitter ;

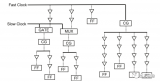

如下圖所示:

post-CTS 后布局階段 ,時鐘樹 clock tree 已經綜合,所以 clock tree 的 skew 已經確定 ,在分析 setup 和 hold 時的clock uncertainty 不確定性時,不需要將 skew 作為時鐘不確定性的一部分(clock uncertainty);

對于 setup ,由于發射沿和捕獲沿是相鄰的兩個沿,所以不確定性要 考慮 jitter ;

對于 hold ,由于發射沿和捕獲沿是同一個沿,不需要要考慮 jitter, 沒有時鐘不確定性 。

-

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16528 -

時鐘電路

+關注

關注

10文章

236瀏覽量

50701 -

PLL電路

+關注

關注

0文章

92瀏覽量

6397 -

CTS

+關注

關注

0文章

35瀏覽量

14063

發布評論請先 登錄

相關推薦

射頻識別芯片設計中時鐘樹功耗的優化與實現

時鐘網格與時鐘樹設計方法對比研究

!大量收購/回收CTS60綜合測試儀CTS60 孫峰/何S:13549469921

STM32F10X-時鐘樹詳細介紹

STM32時鐘樹

CTS時鐘樹綜合對uncertainty的影響

CTS時鐘樹綜合對uncertainty的影響

評論