對于物理驗證中的LVS,需要對各種物理器件進行SpiceVsGDS的比對,基于現在流行的std-cell的庫的設計方法,LVS需要對CMOS器件多相應的處理,這里會涉及到一些具體的物理庫的知識和小的技巧,這里結合具體的物理設計和CDL形態,一起探討一下std-cell的在LVS的特殊處理,ICer GO!

標準單元庫一瞥

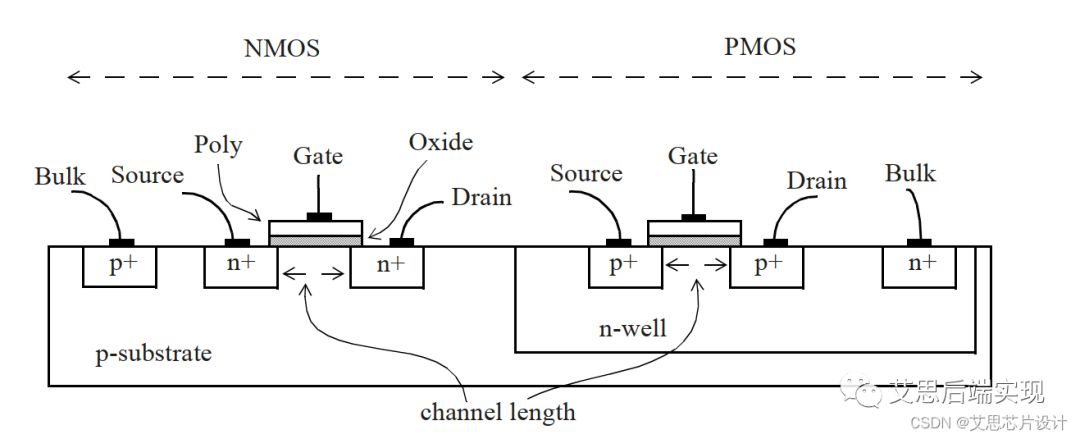

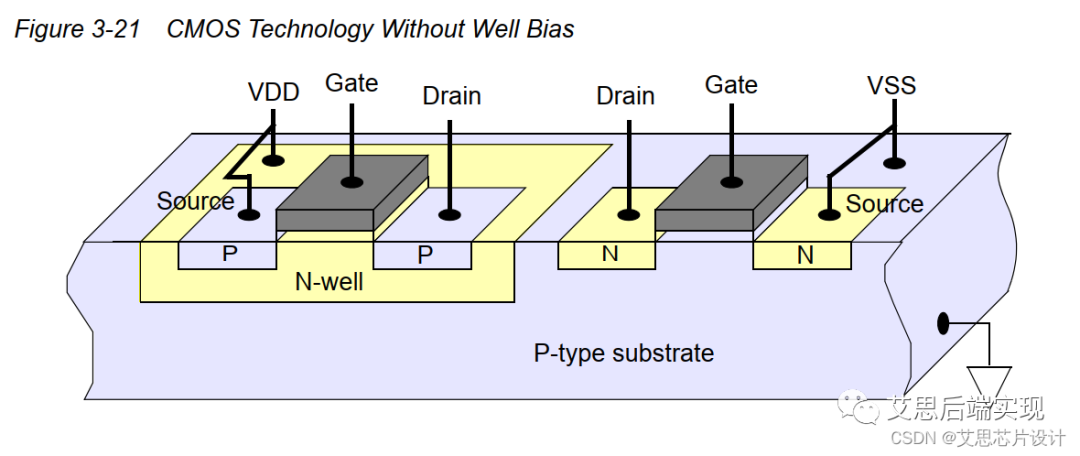

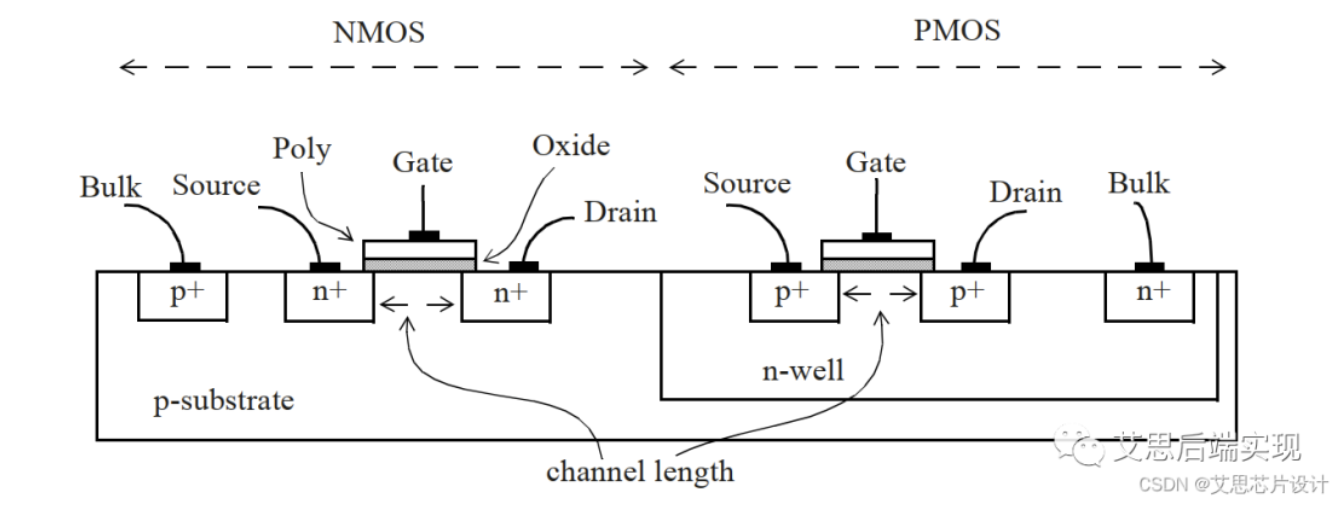

常規的標準單元庫(std-cell)是標準的CMOS設計,由于采用P襯底的設計出來的CMOS器件的速度優勢,目前業界流行的做法就是采用P型襯底(P substrate)來實現的

NMOS 直接坐在P-sub上

PMOS 則做在P-sub上的NWELL

譬如下面的一個簡單的工藝刨面圖

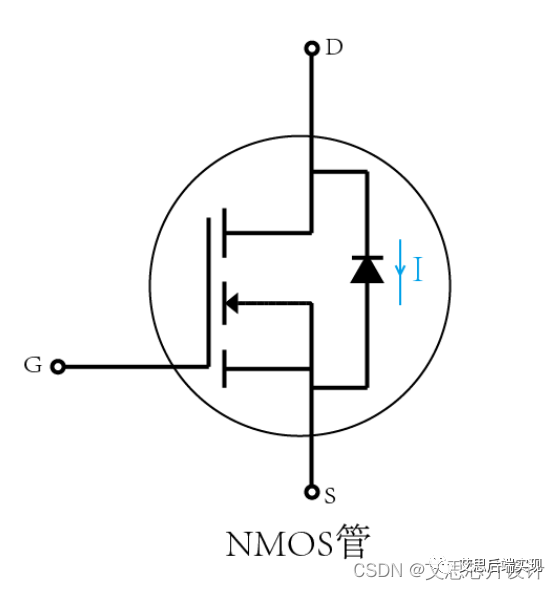

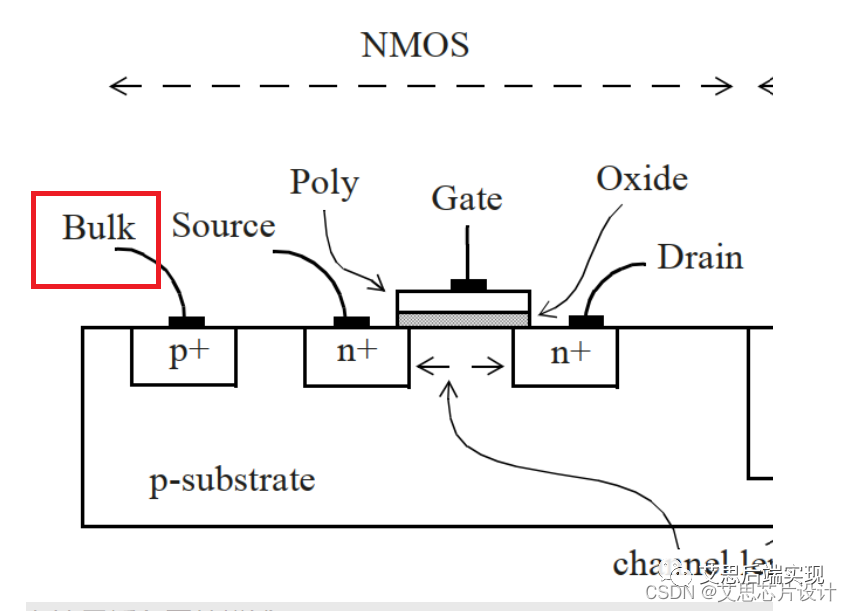

以上邊的NMOS為例,通常有更為常見的是下面的一個示意圖

比較上述兩個圖,可以看到,每一個NMOS都會有一個bulk(體)的連接(有些場合也被稱作body)

在NMOS里邊,這個bulk的作用就是將當前NMOS的P-sub做一個連接,通常P-sub是連接到VSS上的。

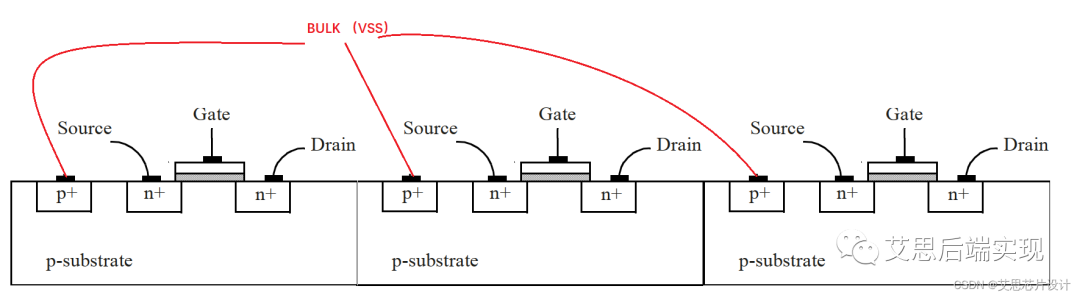

如果芯片里邊有非常多的std-cell連續分布(這個也是常規做法),那么在版圖里邊就會有類似下列的一個刨面圖:

由于所有的NMOS都是做在一片完整的P-sub上,自然NMOS的BULK需要連接到同樣的電位VSS上,這里就是模擬設計里邊常說的TAP 結構了。

可以看到,這個TAP結構完全是一個通用結構,為了節省std-cell的面積,目前業界比較流行的做法就是設計tapless(免TAP)的std-cell,然后使用公用的TAP cell將bulk連接到VSS上,這樣對于節省std-cell的面積很有好處,但是考慮到TAP的電位對于std-cell的bulk的影響,工藝會給出具體的TAP的間距(目前流行的做法是checkerBoard/stagger的做法),APR工具為也提供了具體的命令和參數,支持std-cell的這種設計結構。

通過學習std-cell的形態,可以明確下列要點

**- std-cell都是tapless的結構

bulk需要使用TAP cell 分別將同列的std-cell的P-sub和NWELL分別連接到VSS和VDD上**

LVS的挑戰

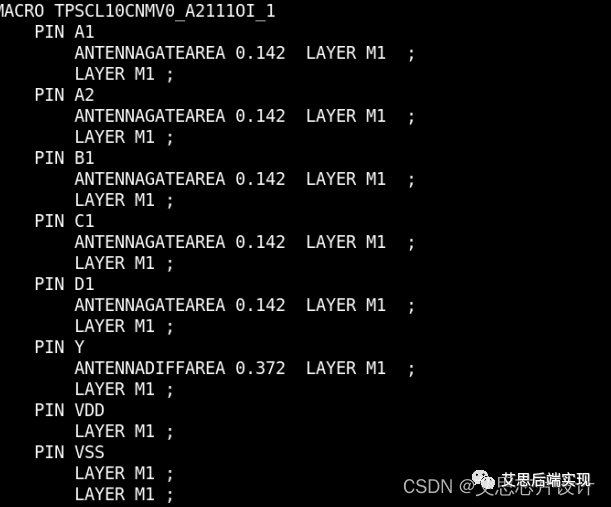

由于bulk在std-cell上PG和信號連接上是沒有明顯貢獻的,對于使用none-bias的流程的std-cell,通常是無法在std-cell看到這個bulk的管腳的,譬如下面LEF的示例:

可以看到,這里有PG管腳的聲明,但是沒有聲明bulk的管腳。

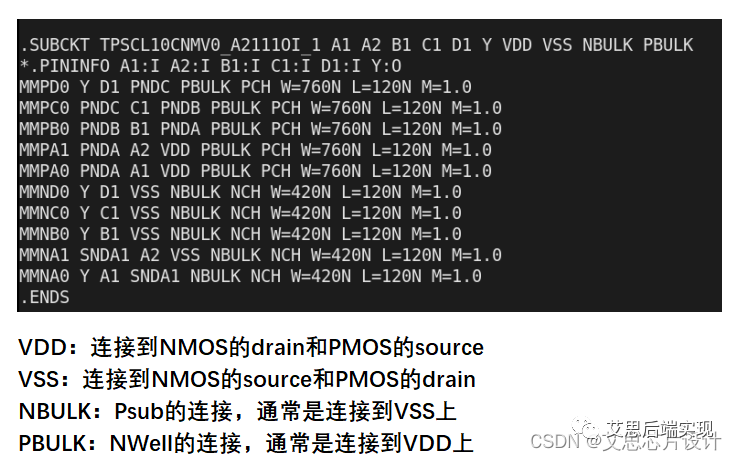

但是對于LVS而言,CMOS是一個四端器件,在驗證柵源漏的同時,也需要完成對bulk的連接驗證,這個也是符合APR的TAP的布局連接的。所以,這里需要打開CDL來一看究竟,見下圖

可以看到,相較LEF而言,最后做LVS的CDL里邊,會有bulk的連接描述。對于none-bias的std-cell而言,bulk的物理連接可以簡單的連接到PG上,基本如下圖

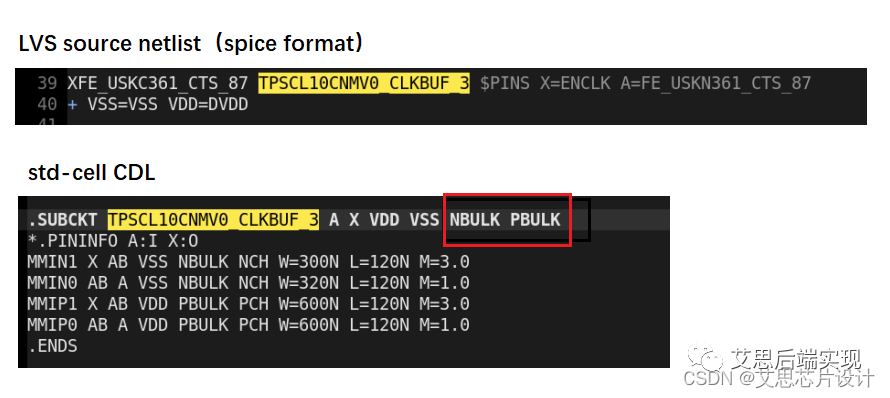

通常的LVS里邊的source netlist是來自于APR工具,APR對于PG netlist的抽取,又是依賴于UPF和LEF的,所以綜上,用戶會遇到一種情形,LVS PG netlist對std-cell的描述會和最終的std-cell CDL出現分歧:source nelist的std-cell會缺失bulk連接聲明,

很明顯,同樣的cell在LVS的source netlist缺失了bulk的連接,這樣的LVS的比對,會發生大面積的std-cell port mismatch error,是無法進行的

v2lvs的高階用法

但是這個問題看起來有一些奇怪,既然LEF里邊沒有聲明bulk,同時在none-bias的flow下,bulk也無法被引用,這樣的LVS是不是就走到死胡同了嗎?當然不是,這里還是要回歸問題本真。

std-cell的bulk僅僅是需要一個連接聲明,具體說來就是兩類

P-sub的bulk連接到VSS上

NWell的bulk連接到VDD上

這個需要在LVS的source netlist處理一下就好(當然APR是沒有這個魔法的)。

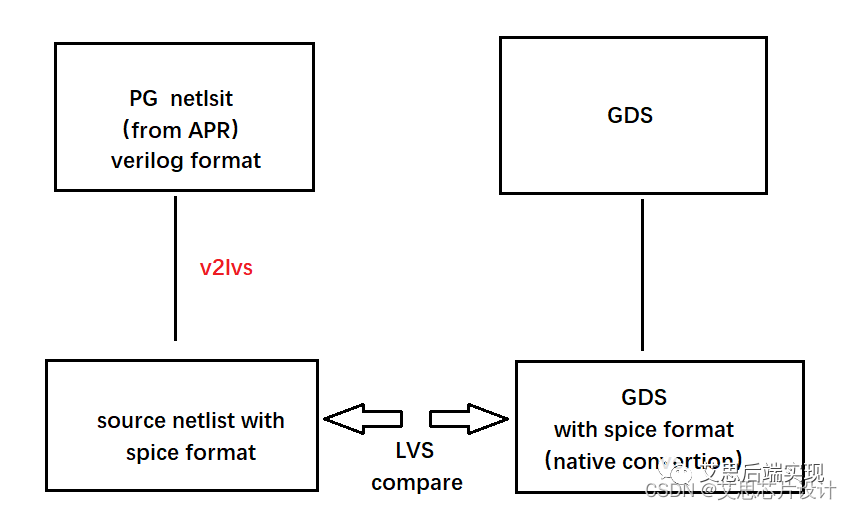

LVS的source netlist 通常是從APR的PG netlist得到的,但是由于LVS是基于spiec比對的,所以一個簡單示意如下:

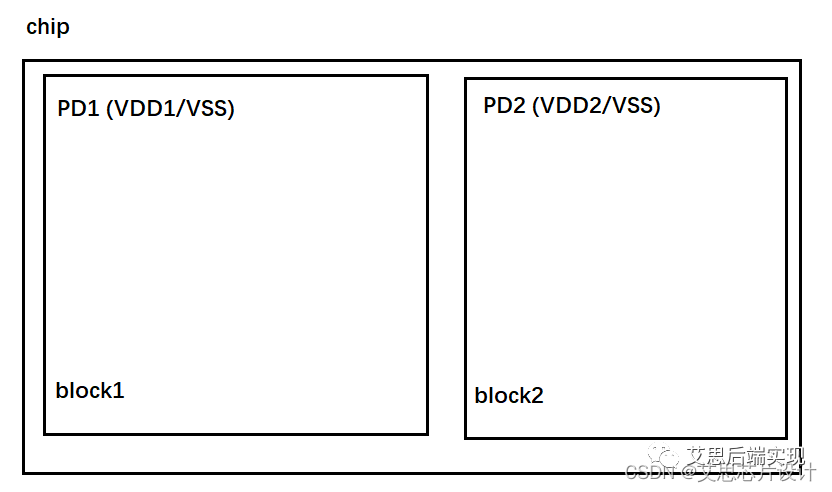

通常而言v2lvs就是簡單的把verilog 轉換成spice格式,但是bulk的處理需要一些高級的用法,尤其是當設計中使用了多個power domain的時候,譬如下面這個示例:

所以,對于處于不同層次/block的std-cell的PG連接就會不太一樣,類似的bulk連接也會不一樣,具體描述如下表

| block | PD | power | ground | NWell | P-sub |

|---|---|---|---|---|---|

| block1 | PD1 | VDD1 | VSS | VDD1 | VSS |

| block2 | PD2 | VDD2 | VSS | VDD2 | VSS |

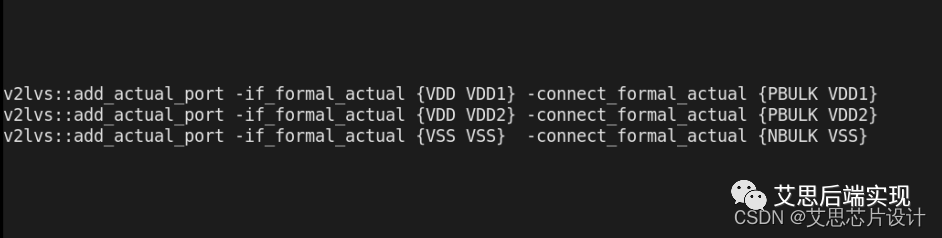

這種情形需要使用v2lvs的tcl模式進行細化處理,才能很好的將處于不同block的std-cell的 bulk連接處理完美

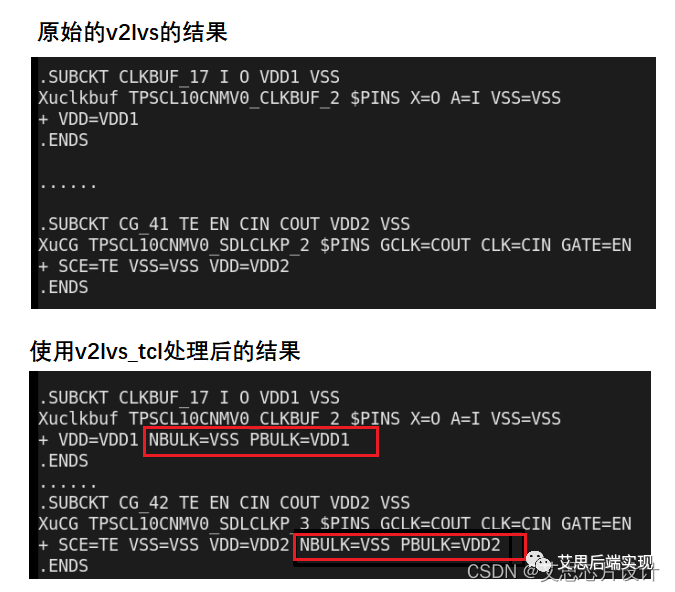

上述命令可以在基于當前std-cell 的PG連接關系,衍生出對應的bulk的連接,會變成下面的情形

這樣處理以后,LVS的std-cell的port mismatch也就完美解決了。

審核編輯:劉清

-

CMOS

+關注

關注

58文章

5689瀏覽量

235170 -

LVS

+關注

關注

1文章

35瀏覽量

9922 -

VDD

+關注

關注

1文章

311瀏覽量

33123 -

VSS

+關注

關注

1文章

31瀏覽量

21423 -

NMOS管

+關注

關注

2文章

120瀏覽量

5398

原文標題:物理驗證LVS對bulk(體)的理解和處理技巧.

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

探討一下,CRC校驗的優勢

一起探討一下這個可行?

探討一下關于STM32中的中斷系統

探討一下深度學習在嵌入式設備上的應用

探討一下Vector架構在AI領域的應用前景

非規則矩形電阻在Calibre LVS中阻值提取

LVS盒處理可幫助設計師迅速完成出色設計

探討一下三星的自動智能充電小車

探討一下關于貼片機在使用過程中會遇到的問題

分享一個cell在layout做LVS時被忽略掉的方法

在 ARIB STD-T108 下使用 AX-SFJK/AX-SFJK-API

物理驗證LVS對bulk(體)的理解和處理技巧

探討一下std-cell在LVS的特殊處理

探討一下std-cell在LVS的特殊處理

評論