看到文章的標題,我猜您也許會覺得反相器很簡單,但其實反相器是所有數(shù)字設計的基本核心單元。下面就來考考您能回答到第幾層問題。

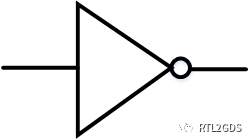

第一層:您能畫出反相器的symbol嗎?

肯定沒問題,否則請出門左轉(zhuǎn),一定是走錯場子了...

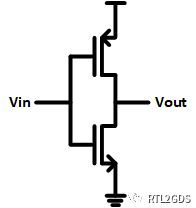

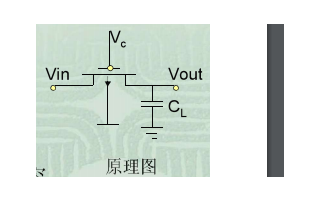

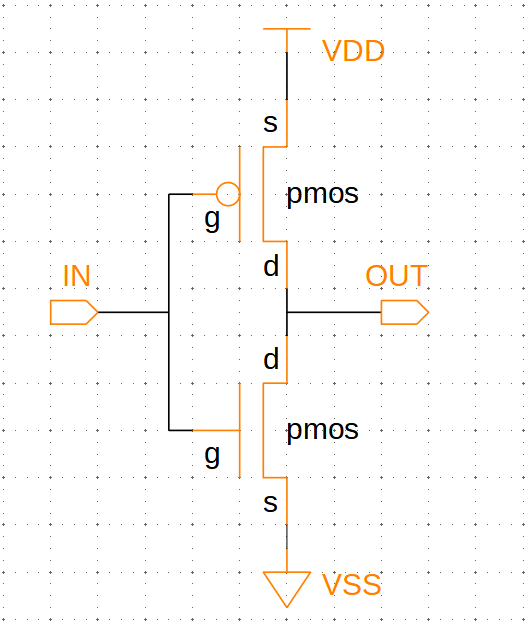

第二層:您能畫出反相器的晶體管級電路圖嗎?

應該沒問題,否則同上...

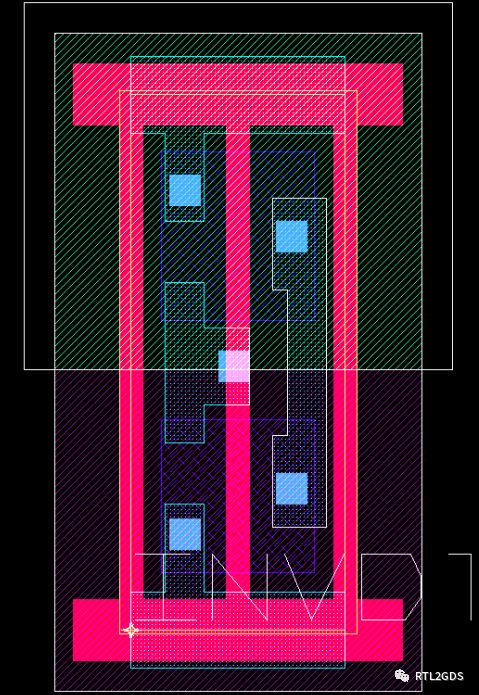

第三層:您能畫出反相器的版圖嗎?

下圖是量產(chǎn)工藝庫里面一個最小反相器真實的版圖:

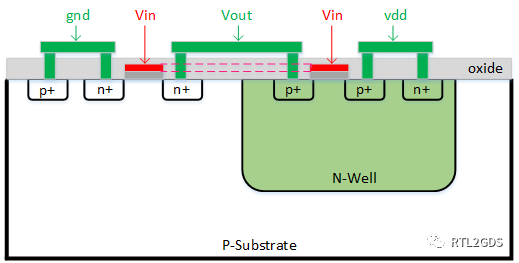

第四層:您能畫出反相器的工藝橫截面圖嗎?

橫截面示意圖如下,應屆生面試時特別容易考這個問題,而且會擴展出讓你畫閂鎖效應等效電路圖等進一步問題,需要仔細了解。下圖顯示的是:在P型襯底中有一塊N阱,PMOS管長在N阱中,NMOS管長在P襯底中,紅色為poly層,綠色為VIA0或者M1層繞線。

第五層:您知道反相器的傳輸延時在STA中是如何得到的嗎?

這些傳輸延時(簡稱delay)都是通過庫里面的查找表得到的,這些查找表是通過對標準單元進行建模,然后利用模型進行掃描仿真得到一個查找表,方便STA時使用。對于標準單元延遲時間的建模模型,需要特別了解的有兩類,一類是基于電壓源的NLDM(Non-Linear Delay Model),另一類是基于電流源的CCS模型(Composite Current Source)。

NLDM模型

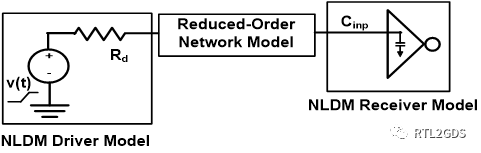

NLDM模型的驅(qū)動端和接收端的模型如下:

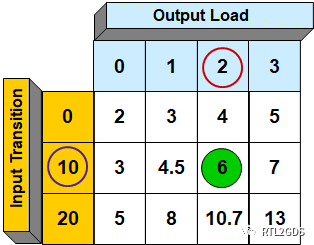

通過改變輸入信號轉(zhuǎn)化時間(Input Transition)和輸出負載(Output Load),仿真得到標準單元(簡稱stdcell)delay值的查找表,存在標準單元庫(.lib)中,如下圖所示,查找表中一般有index1(Input Transition或者slew)和index2 (Output Load)兩個維度,其中:index1是縱坐標,index2是橫坐標。那如果Input Transition的值,或者Output Load的值不在查找表中,工具會通過插值運算來計算出delay值。

NLDM模型的前提假設是接收端負責為純電容性負載,但是隨著集成電路尺寸的縮小,繞線電阻變得不容忽視,這種模型的誤差也會變大。另外一點是因為在深亞微米工藝,繞線串擾引起的噪聲影響越來越大,需要新的模型來更精確地來模擬噪聲。CCS模型就是因此而引入的。

CCS模型

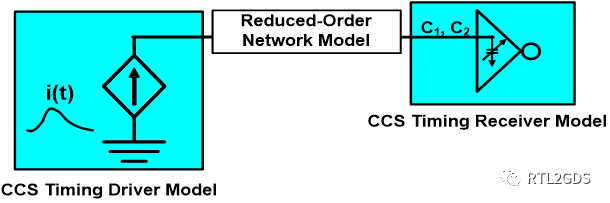

CCS模型的驅(qū)動端和接收端的模型如下,與NLDM不同的是,在驅(qū)動端采用電流源代替了電壓源,在接收端采用兩個電容,其中一個模擬近端的負載電容(C1),它的充放電速度快,另一個模擬的是遠端的電容(C2),它的充放電速度慢,這樣能夠進一步提高上升和下降波形的精確度。

CCS模型在.lib中是以離散波形的形式存在的,如下圖所示 :

從精度上來說,NLDM模型跟SPICE模型的誤差在正負5%左右,而CCS模型跟SPICE模型的誤差能達到正負2%。

第六層:您知道反相器的延時的計算公式嗎?

一般反相器可以等效為下面的開關電阻電容模型,當輸入為低電平時,NMOS管斷開,PMOS管等效為一個電阻Rp,而當輸入為高電平時,PMOS斷開,NMOS等效為一個電阻Rn。

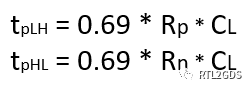

為了簡化運算,我們暫時假設輸入信號高低轉(zhuǎn)換的時間為零,即為一個階躍響應(實際上不可能,所以才需要考慮Input Transition),那么對于輸出Vout來說,它從低到高的傳輸延時tpLH其實是電源VDD經(jīng)過Rp對輸出電容CL的充電時間。類似地,從高到低的傳輸延時tpHL其實是電容CL經(jīng)過Rn對地的放電時間。公式如下:(如果對公式中0.69這個值不解,可以在公眾號發(fā)消息給我)

那么問題又來了,怎樣才能盡量保證下降和上升延遲一樣呢?這一點對于時鐘樹上的clock inverter 和clock buffer尤為重要。通過上面的公式可以知道,方法就是讓Rp和Rn盡量一致,由于PMOS管是利用空穴傳輸電流,而NMOS是利用電子傳輸電流,它們的遷移率是不同的,為了讓Rp = Rn, 一般需要PMOS管的寬長比(Wp/Lp)是NMOS管(Wn/Ln)的2-3倍。

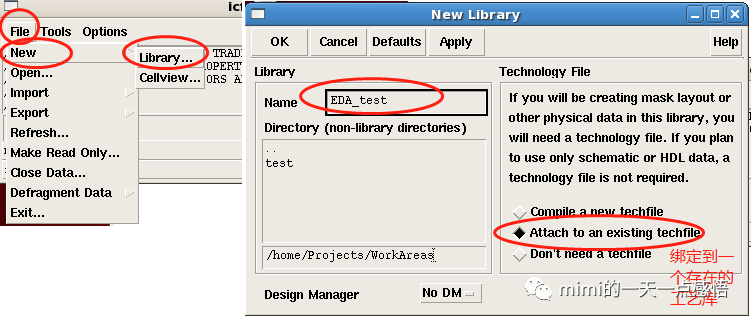

第七層:您知道反相器的SPICE模型嗎?

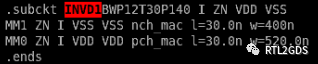

從前面的內(nèi)容可以看出,衡量stdcell delay模型的好壞,其中一個指標是與SPICE模型的誤差,那我們來看看一個標準單元庫中最小尺寸反相器的SPICE模型:

它僅僅由一個NMOS管(nch_mac)和一個PMOS管(pch_mac)組成,它們的溝道長度都為30nm,寬度分別為400nm和520nm,容易看出,這個反相器在上升下降延遲上可能會有一定差別。那具體nch_mac和pch_mac的模型就更復雜了,模擬電路設計工程師需要特別關注,但是作為數(shù)字電路設計,不必深究,不過需要知道MOS管大致工作的幾個區(qū)域,比如線性區(qū)(resistive,功能等效為電阻),飽和區(qū)(saturated),以及截止區(qū)(off)。下圖中的反相器輸入輸出傳輸特性曲線上標出了不同輸入電壓下NMOS和PMOS的工作狀態(tài),有興趣可以深究,在這里就不繼續(xù)挖了。

總結(jié)

一個簡單的反相器能體現(xiàn)出數(shù)字前端和后端設計中很多方面的知識,遠遠不止上面七個問題而已。這篇文章想重點介紹的是,STA所用到的標準單元庫中stdcell delay值是怎么計算出來的,以及兩種stdcell delay模型(NLDM和CCS)相關概念。

-

反相器

+關注

關注

6文章

308瀏覽量

43049 -

晶體管

+關注

關注

77文章

9502瀏覽量

136950 -

電容充放電

+關注

關注

0文章

94瀏覽量

5784 -

NMOS管

+關注

關注

2文章

118瀏覽量

5337 -

PMOS管

+關注

關注

0文章

82瀏覽量

6565

發(fā)布評論請先 登錄

相關推薦

振蕩電路中加反相器的作用是什么?

反相器,反相器是什么意思

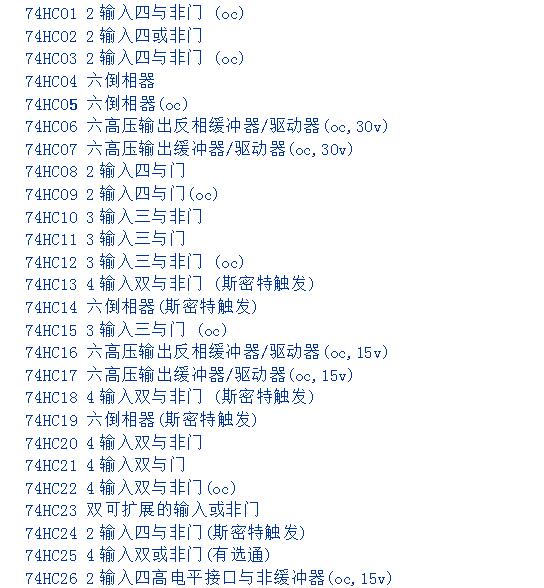

反相器芯片有哪些

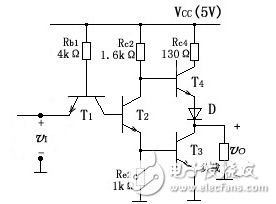

TTL反相器的基本電路(六款TTL反相器的基本電路設計原理圖詳解)

cmos反相器設計電路圖

反相器的作用

MOS反相器和CMOS反相器的詳細資料說明

從一個反相器開始說時序

從一個反相器開始說時序

評論