我們將探討快速精密DAC的關(guān)鍵參數(shù)以及先進(jìn)AD35xxR系列實(shí)現(xiàn)的性能。該系列包含 6 個(gè)部分:

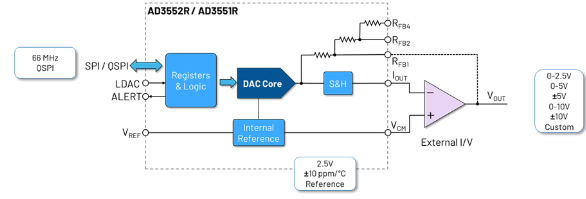

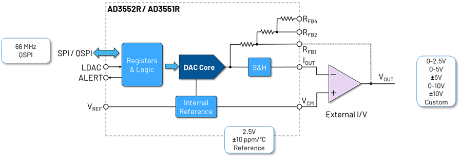

AD3552R / AD3551R:雙通道和單通道、16位DAC,具有外部跨阻放大器(TIA)和四通道SPI(QSPI)接口(圖1)。

圖1.AD355xR原理框圖

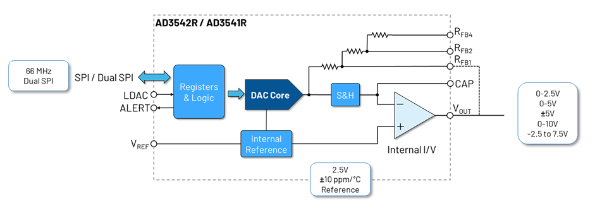

AD3542R / AD3541R:具有內(nèi)部 TIA 和雙 SPI 接口的雙通道和單通道 16 位 DAC(圖 2)。

AD3542R-12 / AD3541R-12:具有內(nèi)部 TIA 和雙 SPI 接口的雙通道和單通道 12 位 DAC(圖 2)。

圖2.AD354xR原理框圖

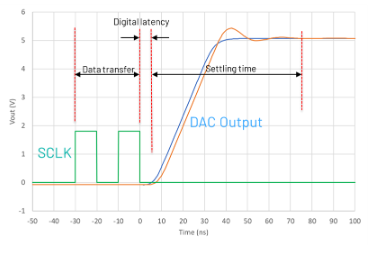

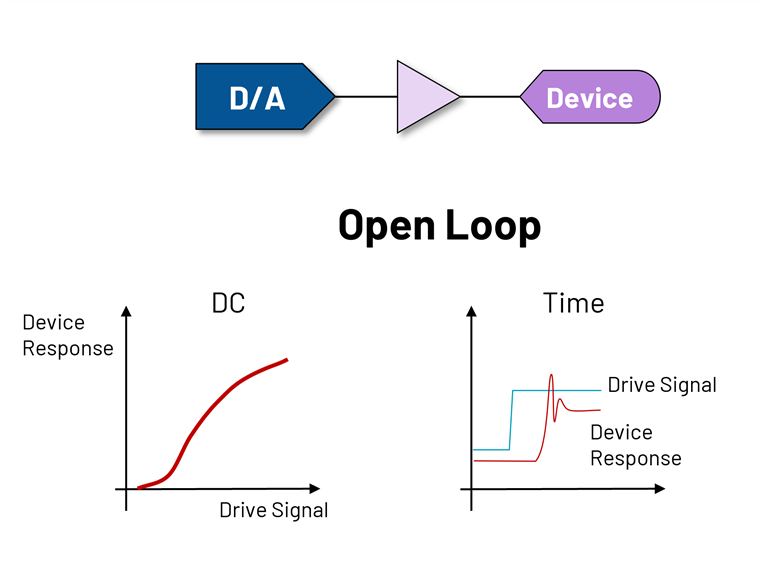

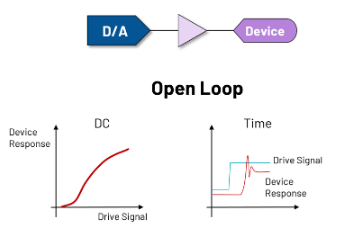

與傳統(tǒng)精密DAC相比,快速精密DAC最相關(guān)的改進(jìn)是更新時(shí)間。更新時(shí)間考慮了將數(shù)據(jù)從控制器傳輸?shù)紻AC的時(shí)間、在DAC中處理數(shù)據(jù)的時(shí)間以及將輸出建立到所需電壓的時(shí)間。已盡一切努力縮短AD35xxR系列的更新時(shí)間。通過(guò)縮短更新時(shí)間,該器件更適合延遲限制反應(yīng)時(shí)間的閉環(huán),例如硬件在環(huán)(HiL)。

圖3.數(shù)據(jù)傳輸和建立時(shí)間

AD355xR具有雙倍數(shù)據(jù)速率(DDR)的四通道SPI接口,允許在兩個(gè)時(shí)鐘周期內(nèi)傳輸16位字。時(shí)鐘速度高達(dá)66 MHz時(shí),傳輸時(shí)間低至30 ns,如圖3所示。AD354xR具有雙通道SPI DDR接口,允許在16個(gè)時(shí)鐘周期(即60 ns)內(nèi)傳輸<>位字。通過(guò)使用流模式,數(shù)據(jù)傳輸開銷最小化,該模式允許在同一事務(wù)中發(fā)送無(wú)限的樣本流,只需發(fā)出一個(gè)寄存器地址。

AD35xxR系列通過(guò)在位鎖定時(shí)動(dòng)態(tài)執(zhí)行所有數(shù)字運(yùn)算來(lái)降低處理開銷。因此,當(dāng)輸入最后一個(gè)數(shù)據(jù)位時(shí),在DAC開始驅(qū)動(dòng)新值之前只有一個(gè)組合延遲。

建立時(shí)間通常是一個(gè)緩慢的操作,其中細(xì)晶收斂到最終值可能需要比兩個(gè)代碼之間的粗粒度回轉(zhuǎn)更長(zhǎng)的時(shí)間。AD35xxR系列可以執(zhí)行大階躍轉(zhuǎn)換,并在0 ns內(nèi)建立至1.100%精度。AD355xR采用外部TIA,允許用戶根據(jù)應(yīng)用要求滿足帶寬、噪聲和壓擺率要求。

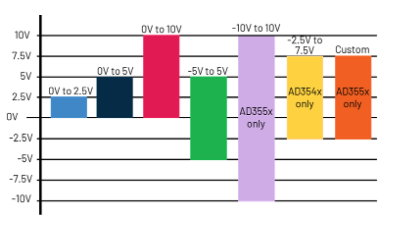

AD35xxR系列還具有可配置的輸出電壓范圍,如圖4所示。

AD355xR具有最大的靈活性,除了5個(gè)預(yù)定義范圍外,它還允許自定義配置幅度和失調(diào)。使用外部 TIA 允許選擇合適的放大器來(lái)驅(qū)動(dòng)預(yù)期負(fù)載。

AD354xR僅允許使用5個(gè)預(yù)定義范圍之一。具有內(nèi)部 TIA 允許將更小的封裝用于不需要驅(qū)動(dòng)重負(fù)載的空間受限應(yīng)用。

圖4.AD355xR原理框圖

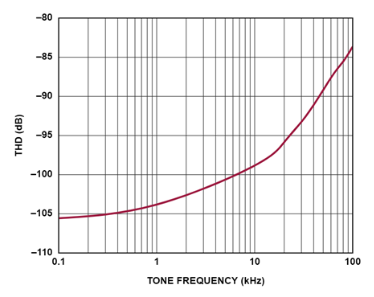

AD35xxR系列不僅專為高斯信號(hào)和HiL而設(shè)計(jì)。它還非常適合諧波應(yīng)用,例如精密波形生成。高采樣率允許在更寬的帶寬上生成非常干凈的音調(diào),從而減少了切換濾波器的需要。圖5顯示了AD35xxR系列的THD。

圖5.AD35xxR 系列總諧波失真

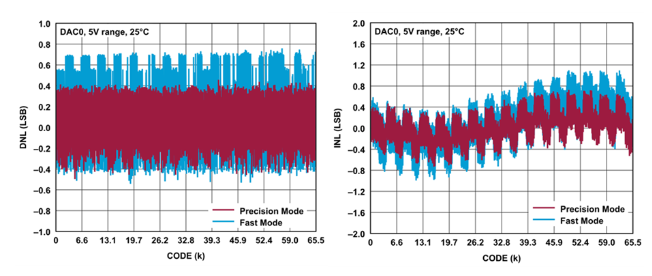

AD35xxR系列提供兩種精密模式,無(wú)需重新配置即可交替使用。快速模式允許使用 16 位數(shù)據(jù)字以最大限度地提高更新速率,而精確模式使用 24 位數(shù)據(jù)字提供更高的精度。兩種模式在DNL和INL方面的比較如圖6所示。

圖6.AD35xxR DNL 和 INL 比較快速模式和精密模式

16 位和 24 位樣本可以交錯(cuò),以享受每個(gè)樣本的好處。例如,16位采樣可用于在兩個(gè)電平之間產(chǎn)生快速轉(zhuǎn)換,然后可以使用24位采樣產(chǎn)生更慢但更精確的電壓。

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

112文章

16203瀏覽量

177413 -

濾波器

+關(guān)注

關(guān)注

160文章

7728瀏覽量

177684 -

dac

+關(guān)注

關(guān)注

43文章

2271瀏覽量

190839

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何改進(jìn)精密ADC信號(hào)鏈設(shè)計(jì)

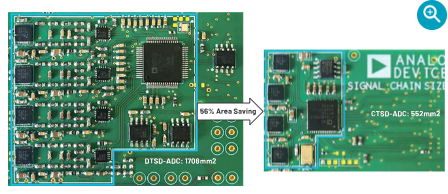

CTSD ADC:如何改進(jìn)精密ADC信號(hào)鏈設(shè)計(jì)

DAC設(shè)計(jì)導(dǎo)入精密10 V工業(yè)應(yīng)用

精密數(shù)據(jù)采集信號(hào)鏈的噪聲分析探討

精密數(shù)據(jù)采集信號(hào)鏈噪聲研究

精密數(shù)據(jù)采集信號(hào)鏈的噪聲有什么意義?

怎么為精密模擬電路供電?

精密數(shù)據(jù)采集信號(hào)鏈的噪聲分析

精密DAC如何快速為您的精密驅(qū)動(dòng)信號(hào)鏈增加價(jià)值

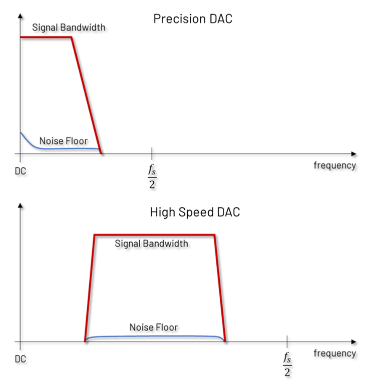

快速精密DAC與高速DAC:異同

精密寬帶寬輸出信號(hào)鏈

如何改進(jìn)精密ADC信號(hào)鏈設(shè)計(jì)

快速精密DAC與高速DAC:異同

讓精密信號(hào)鏈設(shè)計(jì)更容易

精密DAC如何快速為您的精密驅(qū)動(dòng)信號(hào)鏈增加價(jià)值

精密DAC如何快速為您的精密驅(qū)動(dòng)信號(hào)鏈增加價(jià)值

評(píng)論