SDC中的各式各樣的Exception,大體上可以分為“加嚴”和“放松”兩種類型,如下面幾個命令:

##更嚴格##

set_max_delay

set_min_delay

set_data_check

...

##更放松##

set_false_path

set_multicycle_path

set_case_analysis

set_disable_timing

...

需要強調的是需要加嚴的部分,對于異步路徑,往往需要通過set_max_delay來約束,防止路徑過長。而且有些跨時鐘域(CDC)的路徑,為了保證握手時的數據一致性,需要用到格雷碼(Gray Code),約束時更加需要注意。

多周期路徑

之前的文章有提到多半周期路徑,是為了加快數據的處理速度。這里的多周期路徑則是針對那些不需要太快的處理速度,一定程度上節省面積和功耗。多周期路徑常常發生在memory讀寫路徑,某些復位路徑,從慢時鐘域到快時鐘域的路徑等等。

當然,多周期路徑是需要電路結構配合實現的,但總體思路有兩個:

(1)通過Enable信號控制Clock的采樣時刻

(2)通過Enable信號控制Data的變化時刻

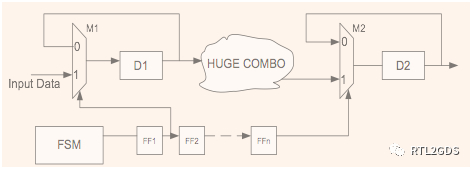

下面舉一個通過方法(2)實現n-1個周期路徑的例子:

上圖主體上是從D1寄存器到D2寄存器的一條路徑,中間經過了很長的組合邏輯。特殊之處在于D1/D2的數據變化是受FSM狀態機控制的,其中D1數據變化發生在第1個時鐘周期后(FF1的輸出信號使能),D2數據變化發生在第n的時鐘周期后(FFn的輸出信號使能)。從下面的波形圖可以看出,D1_OUT到D2_OUT經過了n-1個周期。

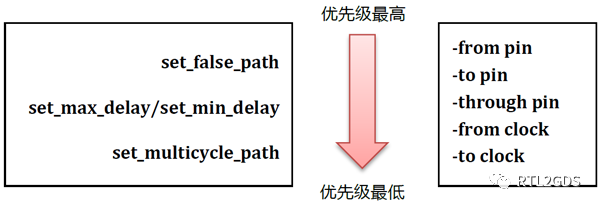

優先級順序

對于幾個常見的exception命令,使用時要特別注意優先級順序,避免出現想要的約束不起作用的情況。

假設有一條從UFF1(CLKA)到UFF2(CLKB)的路徑,想通過以下命令進行約束,最終的效果是怎樣的呢?

# CMD1

set_multicycle_path 2 -from CLKA -to CLKB

# CMD2, 優先級比CMD1高,覆蓋

set_multicycle_path 3 -from UFF1/CP

# CMD3,優先級更高,覆蓋

set_max_delay 6.6 -from UFF1/CP -to UFF2/D

# CMD4,優先級比CMD3低,忽略

set_max_delay 5 -from CLKA -to CLKB

# CMD5,優先級最高,覆蓋

set_false_path -to UFF2/D

可以看出,最終的效果還是false path,設置的max_delay不起作用。

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

CDC

+關注

關注

0文章

57瀏覽量

17774 -

狀態機

+關注

關注

2文章

492瀏覽量

27486 -

SDC

+關注

關注

0文章

48瀏覽量

15528

發布評論請先 登錄

相關推薦

RTOS應用中的優先級反轉問題

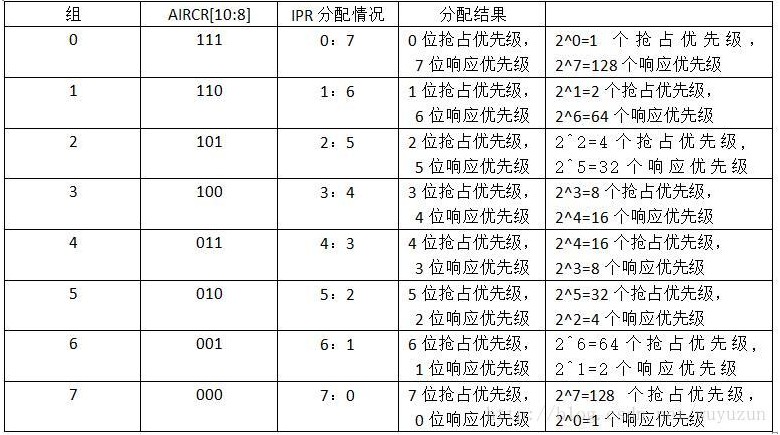

STM32單片機優先級的定義

STM32實例:中斷和優先級概念資料下載

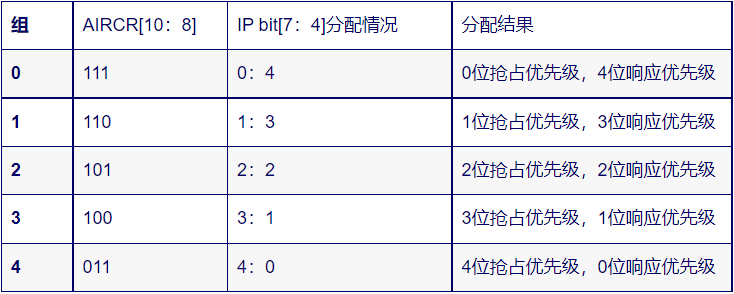

cortex M內核優先級設置

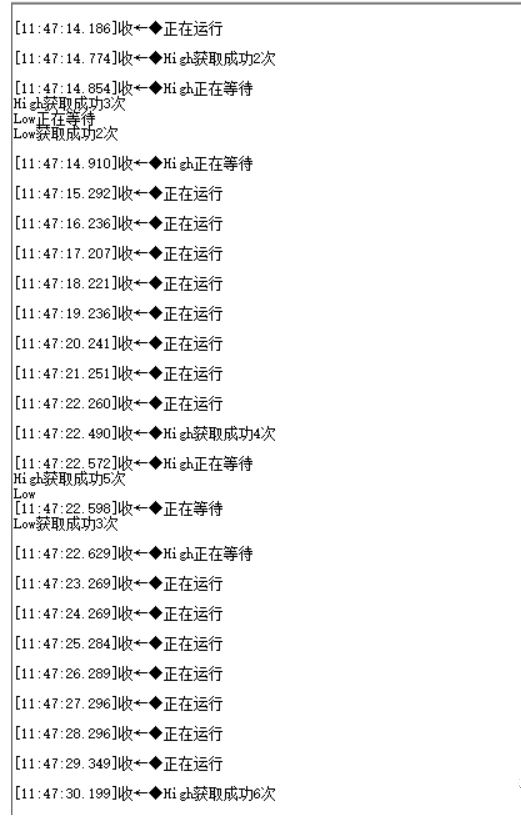

2.FreeRTOS中斷優先級和任務優先級

STM32F103芯片中斷優先級以及FreeRTOS優先級設置

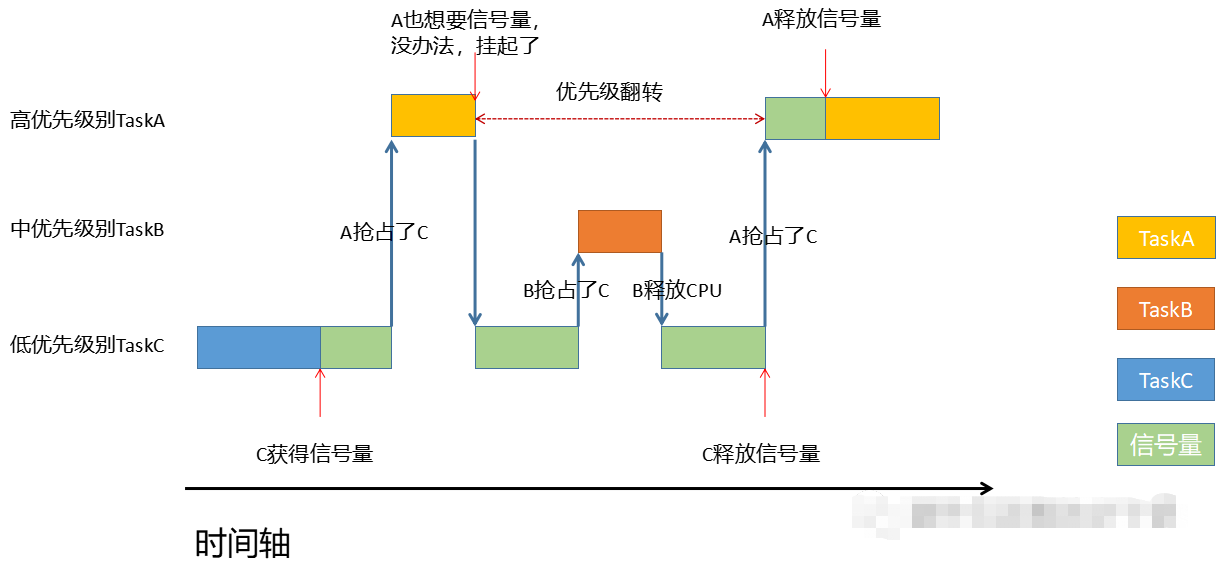

uC/OS-II學習筆記——優先級反轉與優先級繼承機制

什么是優先級反轉

MCP電路實現方法及命令優先級實例

MCP電路實現方法及命令優先級實例

評論