頻率的產生有兩種方法:DDS和PLL,但是為什么射頻工程師一般用PLL多,很少用DDS呢?

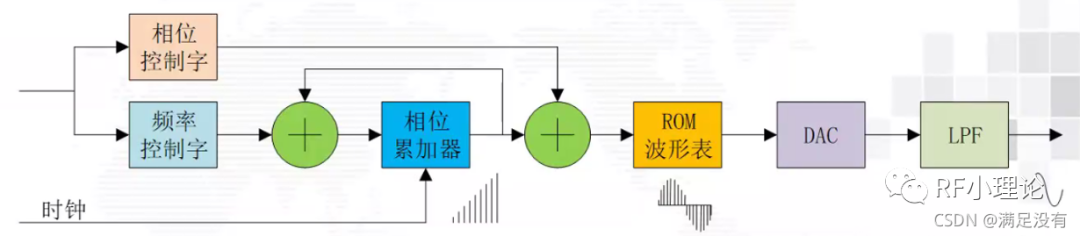

DDS:直接數字式頻率合成器DDS(Direct Digital Synthesizer)。

實際上是一種分頻器:通過編程頻率控制字來分頻系統時鐘(SYSTEM CLOCK)以產生所需要的頻率。

DDS 有兩個突出的特點一方面,DDS工作在數字域,一旦更新頻率控制字,輸出的頻率就相應改變,其跳頻速率高,另一方面,由于頻率控制字的寬度寬(48bit 或者更高),頻率分辨率高。

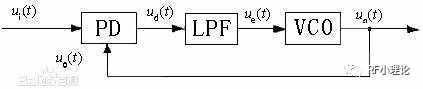

PLL(Phase Locked Loop):為鎖相回路或鎖相環,用來統一整合時鐘信號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。

許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。一般的晶振由于工藝與成本原因,做不到很高的頻率,而在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路就可以實現穩定且高頻的時鐘信號。

從兩個頻率合成器的介紹中我們可以得出:

1.DDS輸出頻率上限取決于參考時鐘,并且由于ADC變換的原因最多只能達到參考的一半。

PLL輸出頻率的上限取決于VCO的上限。

2.DDS頻率切換在數字域實現,時間非常快,可以達到ns級;

PLL鎖定時間取決的硬件時間,時間為us級;

3.DDS的實現不要額外的模擬器件,所以功耗低。

鎖相環由于頻率的實現全部在模擬器件實現,相對而言功耗較高。

上面講了DDS的優點,下面講一下DDS的缺點,為什么射頻工程師很少用的原因。

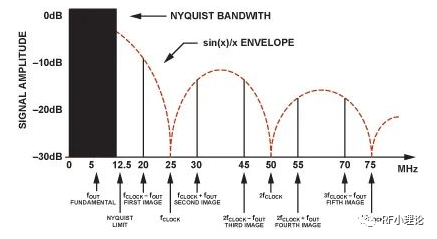

DDS的輸出是DAC輸出,DAC我們都知道,輸出的并不是連續的正玄波,而是帶有正弦時間包絡的一系列脈沖。對應的頻譜是一系列圖像和混疊信號。圖像沿sin(x)/x 包絡分布。有必要進行濾波,以抑制目標頻帶之外的頻率,但是不能抑制通帶中出現的高階混疊

因此,DDS的輸出相位噪聲存在較多的小數雜散,并且很難濾除。對于設計高要求的接收機與發射機,雜散的控制是一個很嚴的指標,基于雜散的可控制性,DDS對射頻工程師來說并不是一個很好的選擇。

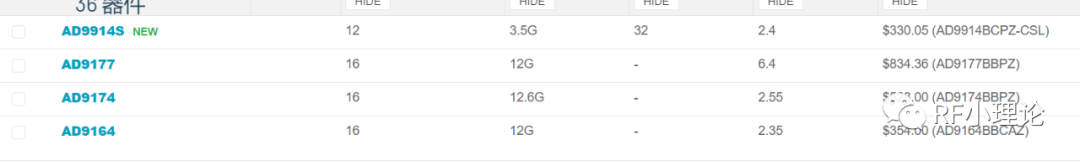

同時由于DDS的輸出頻率最多只到達DAC的一半,目前DAC速率最高也就在12G左右,射頻輸出頻率最高不到6G,對于很多設計來說這個頻率上限可能不滿足設計。同樣的頻率相對功耗而言,雖然沒有很多的模擬器件,但是為了滿足高速采樣,DDS的接口功耗非常高。

綜上所述,在跳頻速率滿足的情況下,基于雜散,整體功耗等考慮,PLL指標與性能更能滿足射頻工程師的需求。

審核編輯:劉清

-

振蕩器

+關注

關注

28文章

3814瀏覽量

138912 -

接收機

+關注

關注

8文章

1180瀏覽量

53413 -

DDS

+關注

關注

21文章

632瀏覽量

152556 -

數字頻率合成器

+關注

關注

0文章

8瀏覽量

6439 -

PLL電路

+關注

關注

0文章

92瀏覽量

6397

原文標題:DDS與PLL的區別對比

文章出處:【微信號:CloudBrain-TT,微信公眾號:云腦智庫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

以DDS為參考的PLL在電臺設計中的應用

DDS芯片選型,請問DDS專用芯片與基于FPGA的DDS的區別是什么?

關于DDS+PLL雷達發射源芯片選型問題請教

DDS與PLL的細微差別

PLL相比于DDS所擁有的典型優勢分享

DDS與PLL的細微差別

DDS還是PLL?

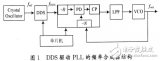

改進型DDS驅動PLL的原理及測試結果

DDS PLL短波頻率合成器設計

基于FPGA 的新的DDS+PLL時鐘發生器

基于DDS+PLL在電臺設計中的應用

基于DDS驅動PLL結構的寬帶頻率合成器的設計與實現

DDS與PLL的區別解析

DDS與PLL的區別解析

評論