用敲兩級DFF的辦法(兩級DFF同步器)可以實現單比特信號跨時鐘域處理。但你或許會有疑問,是所有的單比特信號跨時鐘域都可以這么處理嗎?

NO!兩級DFF同步器,是對信號有一定的要求的。

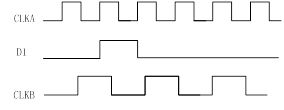

想象一下,如果頻率較高的時鐘域A中的信號D1 要傳到頻率較低的時鐘域B,但是D1只有一個時鐘脈沖寬度(1T),clkb 就有幾率采不到D1了,如圖1。

圖1 快時鐘域信號傳遞到慢時鐘域

因此只有當D1 在很長一段時間內為1或0,確保一定可以被clkb采樣到,才能用兩級DFF同步器處理。

如果信號D1 只有1T或幾個T的脈寬,又需要傳到時鐘頻率較低甚至或快或慢不確定的時鐘域B,這種情況該怎么如何處理呢?

1

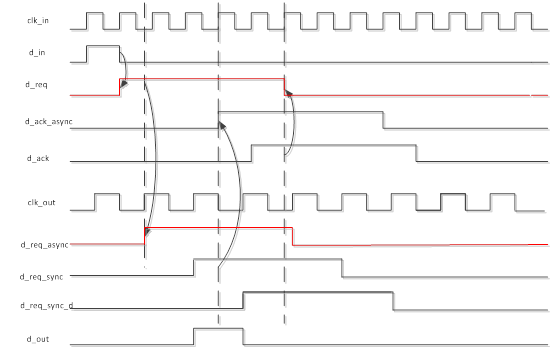

握手協議(handshake)異步信號處理是一種常見的異步信號處理方法。常見的握手協議異步信號處理行為波形圖大致如下圖2:

圖2 一種handshake電路波形

圖2 一種handshake電路波形

信號d_in 所處時鐘域是clk_in,且d_in只有1T 的寬度,想要傳送到clk_out 時鐘域(clk_out 跟clk_in不相關)。

因為clk_out 和 clk_in相位關系不確定,時鐘周期大小關系不確定,無法保證一定能采樣到d_in。

因此需要把d_in展寬,產生d_req 信號;

d_req 信號一直拉高,經過clk_out時鐘域兩級DFF 同步器后,得到d_reg_sync;

取d_req_sync 上升沿1T,即可得到傳送到clk_out 時鐘域的d_out。

此時,d_in 從clk_in 傳送到clk_out 的任務就算是結束了。

但對于handshake 電路來說,任務還沒結束,因為d_req 還一直是高電平。

因此,需要把d_req_sync 信號再用兩級DFF同步器,傳回clk_in 時鐘域,得到d_ack信號;

當clk_in 看到d_ack拉高后,就可以把d_req 信號拉低,到這里一個handshake電路行為才算是結束了。

2

根據上面的波形圖,可以看到握手協議異步信號處理并不復雜,但是細心的朋友應該會注意到,這個處理方法信號傳遞的速度相對較慢。

從圖2 的波形來看,至少需要3個clk_in 和2個clk_out時鐘周期。根據不同的應用需求,人們會對圖2的波形做不同的改造。但萬變不離其宗,原理都是一樣的,電路也大同小異。

最后留4個問題供大家思考,以增進對handshake電路的理解:

- 圖2中的d_req的邏輯怎么實現?

- 圖2中的d_out的邏輯怎么實現?

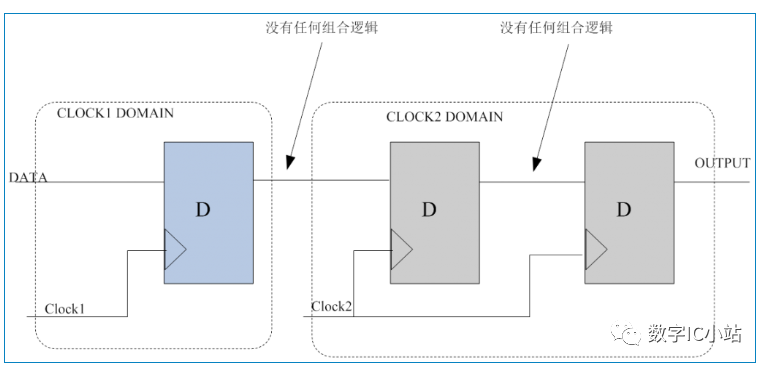

- 假設時鐘域clka比clkb 頻率高,如果輸入信號的兩個相鄰脈沖D0和D1非常較近,如下圖所示,如果使用握手協議處理,會發生怎樣的事情?

4.問題3里面,如果要確保D1數據一定要被能傳送到clkb,電路該如何實現?

-

信號處理器

+關注

關注

1文章

251瀏覽量

25252 -

同步器

+關注

關注

1文章

94瀏覽量

14617 -

CLK

+關注

關注

0文章

127瀏覽量

17126 -

dff

+關注

關注

0文章

26瀏覽量

3400

發布評論請先 登錄

相關推薦

所有的單比特信號跨時鐘域都可以用敲兩級DFF的辦法處理嗎?

所有的單比特信號跨時鐘域都可以用敲兩級DFF的辦法處理嗎?

評論