SOC芯片的基本構成

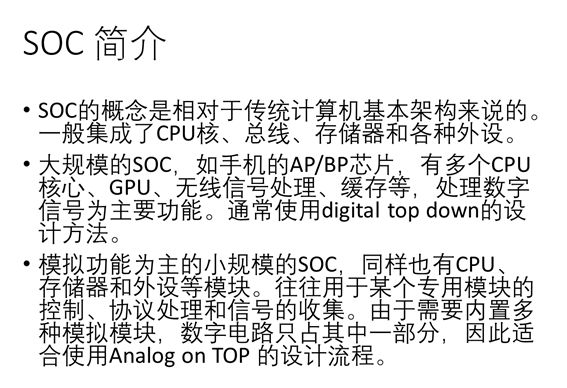

這是SOC的簡介,我們知道SOC的概念是相對于傳統的計算機基本架構來說的。傳統計算機我們都知道有CPU核,有總線,有各種內存,還有硬盤,各種外設。SOC實際上就把這些概念、模塊集成在一起,做在同一個芯片上面。大規模的SOC,像我們熟悉的手機上的SOC芯片,比如說華為的麒麟,高通的驍龍芯片,都是AP芯片,事實上它里邊有多個CPU的核心,包括還有GPU,基帶的處理,還有很大規模的緩存。這些芯片主要是處理數字信號為主要功能,所以通常使用Digital Top Down的設計方式。

模擬功能為主的小規模的SOC,同樣也有CPU、存儲器和外設這些模塊,可以說是麻雀雖小五臟俱全,以這些小規模的SOC作為一個切入點能夠去一窺SOC的一些設計方法,是一個很好的途徑。這些小規模的SOC往往能用于某種專用模塊的控制、協議的處理和信號的收集,由于需要內置多種模擬模塊,數字電路實際上只占用其中的一部分,其中模擬信號與數字信號有大量的交互信號及信號處理,所以比較適合于這些Analog on Top的設計流程。

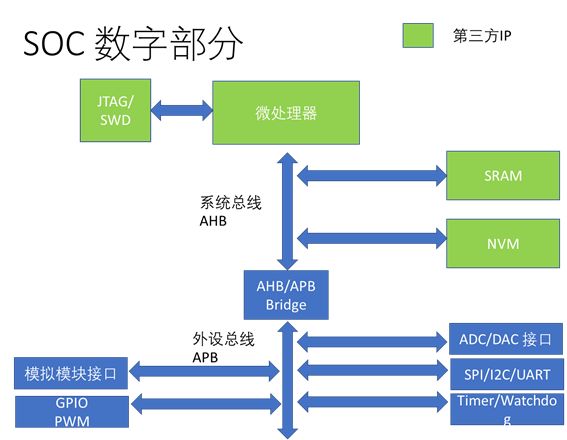

這張圖是SOC芯片的基本構成,中間是數字的控制電路,通常有微處理器、總線、SRAM (緩存,或者叫內存)、有NVM(非易失性存儲器),比如說像FLASH、EEPROM,或者OTP、MTP,還有外設的一些控制電路。

綠色的部分是模擬的模塊,通常有OSC振蕩器,有作為數字和外界的窗口ADC或者DAC,有邏輯控制的GPL作為通用的I/O接口,為了給數字電路供電有LDO,因為數字電路需要比較穩定的電源。

右邊第一個是PHY,是協議物理層,通常它本身也是一個數模混合的模塊,它既有數字電路也有模擬電路,把它放在這里就表示需要模擬工程師對它進行重點的關注。還有作為對微弱信號處理的放大器和AFE,AFE是模擬前端,將模擬信號經過放大處理,把它輸入到ADC或者數字電路當中。PowerManagement是經常會用到的一個模塊,包括BUCK,BOOST或LDO這些模塊,另外就是傳感器的控制電路。前面這幾個模塊每個芯片都不一樣,有可能有,有可能沒有。但是左邊這一列,基本上每個SOC芯片都會有。

這里講講SOC的數字部分的結構,標成綠色方塊的部分是第三方的IP,是需要向IP供應商去購買的,也有一些是自己設計。

微處理器是最核心的部分,比如向ARM購買的IP,有高端有低端的,低端如M0、M1這些32位的處理器,它往往需要一個DEBUG口,DEBUG口往往是JTAG或SWD。微處理器需要內存,以及用于存放程序的NVM,跟它通訊時使用系統總線叫AHB,ARM的話叫AMBA總線。

AMBA總線處理比較復雜,所以處理一些比較簡單的外設的時候,是通過從AHB到APB的橋接。

ADC或者DAC的這些接口是通過AHB的總線來控制的,其中包括一些跟外界的接口,像SPI接口、I2C接口或者UART、Timer、Watchdog、GPIO、PWM控制,還有這里比較關心的是模擬模塊的接口。

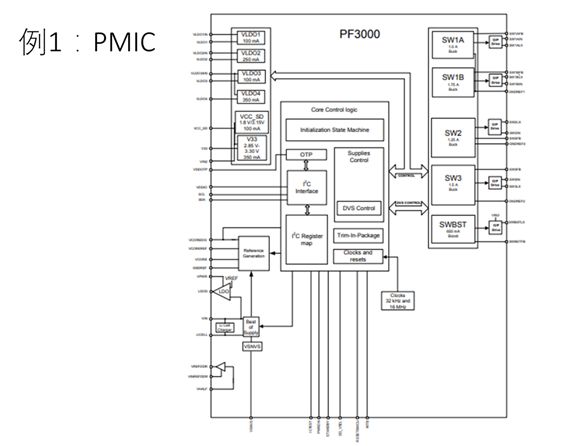

講了這么多,先來看幾個例子:這是一個PMIC,它是Freescale公司的給系統供電控制的PMIC,這個芯片是要根據外面系統上的主AP控制,針對主AP能夠控制電源的每路輸出,或者對輸出上電時序進行控制。

這個芯片可能是一個State Machine,也就是說相當于把內部的Firmware給固化了。但是我們也同樣可以看到它有相當多的數字控制邏輯,包括我們剛才講的模擬部分的OSC、Reference、LDO,還有左下角的鋰電池的充放電管理,上面幾個大的是LDO、BUCK、BOOST 這些Power Management模塊。

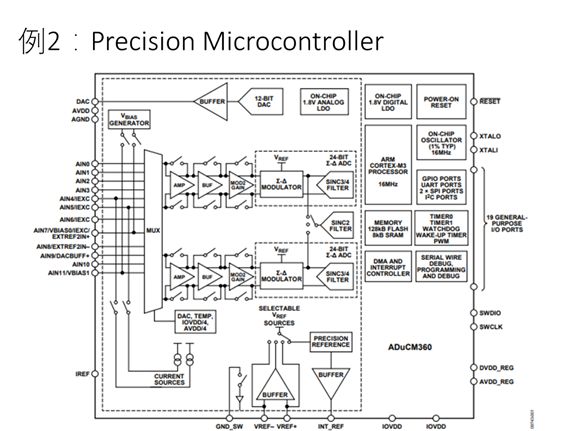

我們再來看看另外一個芯片,這個是Precision Microcontroller,這是ADI推出的一個對于微弱信號進行放大采集的一個SOC,可以看到右邊內部有一個ARM的M3的處理器,為了給這個處理器提供時鐘,有一個片上Oscillator,GPIO,UART,SPI、I2C接口都存在,還有很多個Timer、Watchdog、DEBUG接口,包括有一個128K的FLASH和8KB的SRAM。電源的供電是通過片上的1.8V LDO,左邊的模擬部分有12位的DAC,有24位的ADC, ADC的前面有放大器,Buffer跟PGA。

通過前面這兩個例子,我們能夠看到一個小規模SOC的基本構成,加入了一個內核以后對于芯片的可重構特性會大大的凸顯出來,能夠適用于多種場合的不同應用。

SOC TOP的設計

現在講講SOC TOP的設計,后面的講解以問答的形式。這里提出三個問題,第一個是SOC的Analog on Top的設計環境是什么,第二個是SOC TOP的設計與ASIC設計有什么不同,第三個是SOC TOP設計與模擬設計有什么不同的地方。

作為一個SOC設計,它的主要難點是需要同時去整合這兩套設計流程,而且要在頂層將這兩套設計出來的東西放在一起。

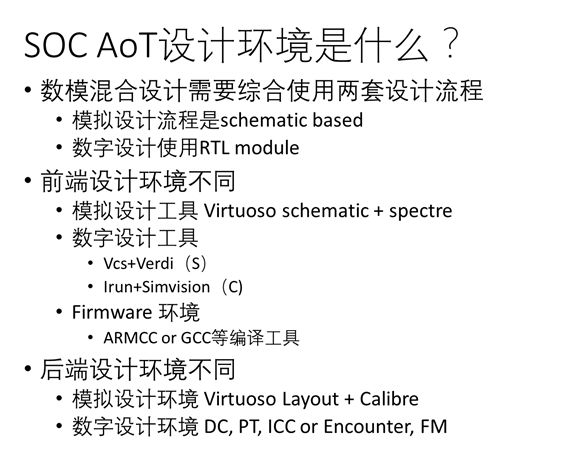

SOC的TOP設計環境是什么呢?我們知道數模混合設計環境是需要綜合使用兩套設計流程,模擬工程師比較熟悉的一個設計流程是Schematic Based,數字設計使用的是RTL module的形式。

對于一個模擬設計者來講,熟悉的工具就是Virtuoso schematic + Spectre。數字設計工具Synopsys用的是VCS+Verdi,Cadence用的是Irun+Simvison。除了這兩套工具之外,還需要搭建Firmware的設計環境,因為我們要驗證SOC,沒有程序是跑不動的,那要寫程序或者要編譯這個程序需要用到ARM CC或者像GCC之類的編譯工具,環境需要搭建。

后端的設計環境也是有相當的不同;模擬設計往往用Virtuoso Layout,再加上Calibre,做LVS和DRC;數字設計環境的話,首先需要去DC綜合,時序分析PT,自動布局布線往往使用ICC或者Encounter,后面FM是形式驗證,還有包括測試Patten的自動生成這這類工具。

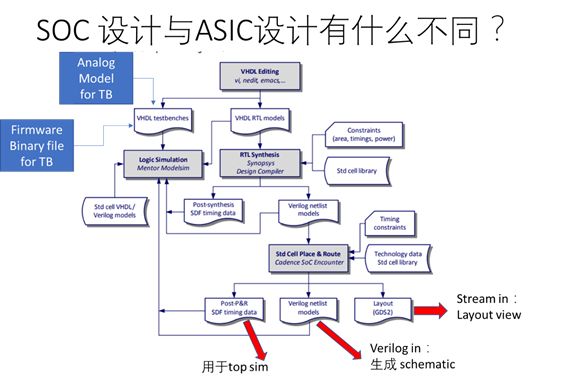

這個圖是從網上下載下來的一個ASIC設計的一個流程圖,我們可以看到一開始是用文檔編輯工具去設計數字電路(硬件描述代碼),把它制作成Testbench和Hierarchical的Modules,這些Modules首先用仿真工具去仿真,沒有問題以后對他進行DC綜合,綜合完了以后生成Verilog的Netlists,再對Netlists進行PR。

PR完成以后會有三個文件:一個是GDS,第二個是Verilog的Netlists,還有一個是PR以后的Timing信息叫做SDF文件,這三個文件在后面的設計當中都會用到,但是在對于ASIC來講,到這里可能就已經結束了。

有不一樣的地方標出來了,就是在左邊,在Testbench的設計階段就需要一些Analog的Model,給到Testbench,對這個數字控制模擬或者模擬返回到數字的這些信號進行模擬。還有是Firmware的Binary file,就是固件的二進制碼,也要給到這個Testbench,才能夠對SOC進行仿真。

輸出的文件處理,會把GDS導入到Analog設計Layout中,使用Virtuoso的Stream in導入;對于Netlist,會把它用Verilog in的方式生成Schematic;SDF文件也是必不可少的,在仿真的時候要用于TOP SIM的timing的仿真,如果沒有這個文件的話,有可能Verilog Netlist in的文件由于時序不對沒辦法做正確的仿真。

SOC設計與模擬設計有什么不同呢?

在上面我們會先去設計Block level,然后把它組成一個Analog TOP的Schematic,這個是沒有Digital模塊的,但是它會有一個Digital的空的block。

TOP仿真的時候是使用Digital的RTL、IP的Model和Firmware組合在一起進行Analog Top的仿真,這時因為沒有數字的Schematic,所以只能用AMS的方式進行仿真。

這步仿真通過以后,我們會對Digital進行PR,PR完了以后會由SchematicVerilog-in進來,組成最終的TOP的Schematic。對這個Top的Schematic進行PR后的仿真,這個仿真比較簡單,不會像前面那個Analog TOP的仿真這么詳細,后面只是簡單的驗證一下最后的電源軌和模塊連接是不是準確。

從后端上來看,在Analog Block Level或TOP做完以后馬上進行Analog layout,這時會等Digital PR完成,完成以后會Stream-in進來,兩個組成在一起形成TOP的Layout,當然還有一些購買的IP,有些IP可能不會給底層的GDS,只會給Phantom View,Phantom View拿進來以后形成TOP的Layout,再對它進行LVS。

SOC TOP的驗證

后面我們講一下SOC TOP的驗證,這里也采用問答形式,主要回答四個問題:第一個是怎么去仿真SOC TOP;第二個是我們重點要驗證哪些項目;第三個是我們經常會遇到的仿真速度很慢,我們怎么辦;最后一個是要不要做FPGA驗證,這也是經常會遇到的一個問題。

怎么去仿真SOC 的TOP?一個最基本的驗證方法是使用Virtuoso AMS仿真工具,我們先列一個TOP的Verification list,對它進行一個個的人工檢查,這是一個最基本的驗證方法。群主她們有一個更加高級的自動化的驗證工具,我們沒有這個條件,只能是比較原始的方式去人工檢查。

對于很多初學者或者對于一些小規模的SOC來說,這種驗證方法是足夠的。首先需要一個Config的文件,這個文件是Analog用于定義Schematic Hierarchy的View的方式,可以指定尋找View的順序,比如說優先尋找Schematic,再允許去尋找某一些模型。

這個時候針對Digital的Block,我們只需要指定頂層,指定頂層以后,因為Digital是需要有很多的Module組合在一起的,那么怎么去設置這個Module的尋找路徑呢?需要在Virtuoso AMS的設置里面去設置一個Digital的文件列表;第三個,在TestBench上面加一個模塊去設置仿真的初始條件。

先看看仿真器的設置,仿真器設置主要是Config file怎么去設置。在RTL仿真時,我們只需要去指定Digital Top的Cell View。舉個簡單例子,我們可以把Digital的Top,設置成functional,或者說是Schematic,都可以,那對functional只需要digitla 的top,它里邊會引用到很多的其它的Module,這個時候Config是指定不了的,需要在Virtuoso的AMS Option里邊去設定一個.f文件,這個.f文件里面設定了它的Module的全路徑。

另外一種方法也可以只在Digital TOP上做一個空的Schematic,再加一個Stop Point,加了這個Stop Point以后不會再往下去生成網表,只是在Schematic這一層生成一個空的,這時候,它會去在.f文件當中找相應的Module。

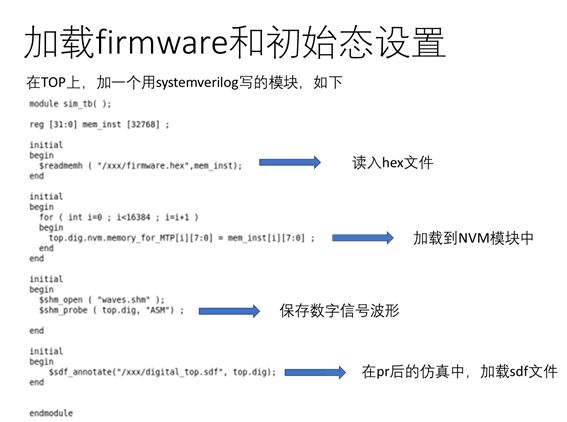

在TOP上我們還需要加載一個System verilog寫的模塊,這個模塊用于加載Firmware和初始態的設置。這里是一個例子,我們把這個Module生成一個Symbol,把這個Symbol放到TOP上就可以了。我們可以看到一開始會去讀入一個16進制HEX的Firmware文件,把它放到緩存當中,然后在初始化的時候把這個緩存一個個的寫入到NVM當中。

第三是用兩個語句去保存dig.top的數字波形,把它存放到Datebase當中。最后一個是在PR后的仿真中有用,在這里設置它的Timing信息sdf文件,因為只有設置文件后跑出來的數字時序才是正確的。

SOC TOP重點要驗證哪些項目呢?這里以我自己的經驗寫了幾項:第一個是上電使能的順序是重點需要驗證的,因為在數字模塊當中事實上沒辦法去驗證上電的時序,所以在這塊需要重點驗證;第二個是在多電源軌的設計當中電平轉換是不是正確,初始態也就是在Level Shift掉電的時候,是不是能夠輸入正確的初始態,這需要去做驗證,因為我們在數字仿真當中是沒辦法去做多電源軌的驗證,所以需要重點確保沒問題。

另外還有數字模塊輸出的初始態是不是正確,這點很多人可能往往會忽略掉,因為在模擬設計當中我們事實上不太清楚數字輸出,或者說我們經常會默認為數字模塊輸出是一個零狀態,事實上有可能不是,這個是需要去確認的。標紅色的幾項需要花大量精力去做,第一個是模擬模塊與數字模塊之間的連接是不是正確,這個是Mixed signal主要需要驗證的地方,第二個是需要與數字模塊交互的模擬模塊,這個非常費時,因為如果一旦出現這種交互的話要等到數字內部初始化完成才能夠仿真到需要的狀態。

第三點也是比較麻煩的,是測試模式的仿真。這里主要是一些測試模式接口,像測試模式入口、在線仿真入口,還有測試Pattern入口,這些事實上都是在不正常工作的時候的一種工作狀態。由于它不涉及到正常工作模式的狀態可能有些人會會忽略掉,但是一旦忽略的話,往往有可能這些測試模式是不成功的。

最后一個是異常的一些處理,包括下電或者電源上毛刺的處理等。

仿真速度很慢怎么辦?仿真速度慢首先我們要去檢查慢的原因,數字信號變化是不會使仿真變慢的,模擬信號變化如果觸碰到一個閾值會引發一次計算,我們知道模擬的計算是一個矩陣計算,如果是大規模的模擬模塊的話,它的仿真速度是將會非常慢,第三點就是模擬信號的一些不連續,叫做硬轉折,它會造成收斂性的問題,一旦碰到收斂性問題,會讓速度變得很慢。

加快仿真的方法有下面的幾點:第一點是我們可以用仿真器的Debug模式去檢查仿真慢到底慢在哪里,它的原因是什么;第二點一個基本的方式是我們把那些驗證項目不涉及到的模擬模塊用模型去代替它,這樣的話會避免不必要的模擬計算量;第三點是減少不必要的模擬信號的變化,這點后面會講到;第四個是優化涉及時鐘的模塊。

檢查仿真慢的原因,Debug模式是怎么做的呢?我們在Virtuoso里面Simulator option上添加一句diagnose=detailed,這樣的話就能夠打出很多的仿真過程當中的一些信息。觀察log文件,去看哪個模塊的信號將仿真的step變小了,或者在哪個點觸發了一次新的計算,去看這次計算是不是你想要的,或者說是不是可以避免的。

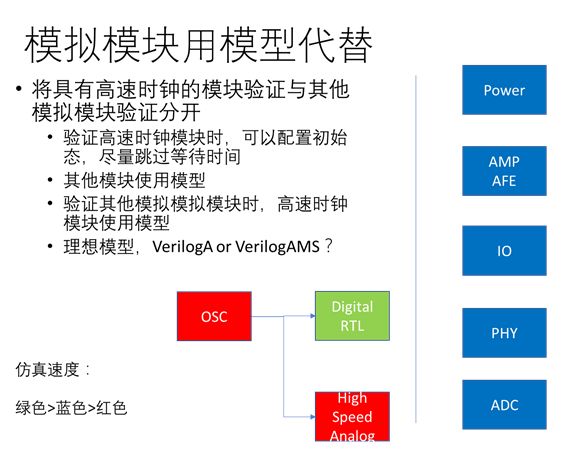

加快仿真速度的基本方法就是把模擬模塊用模型去代替,這里我畫了一個圖,它的仿真速度綠色的最快,藍色次之,紅色仿真速度最慢。什么東西仿真速度是比較慢的?一個是Oscillator,然后用到這種高速時鐘的高速模擬模塊,比如說高速ADC。什么東西是仿真速度比較快的呢,其他的一些模擬模塊,事實上只要它不涉及到動態波形、動態信號的話,它的仿真速度都還是挺快的。

為了加快仿真速度我們要把高速時鐘模塊的驗證跟其他的模擬模塊的驗證分開來,驗證高速時鐘模塊的時候可以配置一些初始態,盡量盡快地跳過等待的時間,讓它盡快的能夠驗證到你想驗證的一些信號。

這個時候其它的模塊使用模型,驗證其它模擬模塊的時候高速時鐘使用模型。這里有個問題就是,往往對模擬設計工程師來說不太熟悉Verilog-a或者Verilog-ams,就用理想的模型去搭了一個,那這種方式合不合適呢?

我們這里來看一個例子,以一個4M的時鐘作為一個例子來看看Verilog-a和Verilog-ams寫的模型的方法。對于Verilog-a來講,這里寫的是一個4M的時鐘,所以每過125ns會翻轉一次,osc_4M這個信號是個整形,要把這個整形變成一個輸出,這個輸出是一個模擬信號,所以要使用transition這個語句。這里需要注意,如果這個信號不用transition的話,有可能會遇到硬轉折,也就是說有收斂性的問題。

加入了transition以后會添加一個上升時間、下降時間、一個Delay時間,把它從0-1變成VDD、VSS的信號輸出去。如果用Verilog-ams就比較簡單,可以直接用類似于Verilog寫的語句,把它定義成一個邏輯信號,直接在125ns翻轉一次就可以了。

但是事實上我們會發現,不管是Verilog-a還是理想模型都是一個模擬信號,一旦是模擬信號的話,那么它就會頻繁的去觸發模擬計算。舉個例子,我們這里的transition語句,它每碰到125ns的時候就會去算,把它形成一個ramp波形,這個波形的計算可能有好幾個點。

我們來看使用Verilog-a和Verilog-ams有什么不一樣的地方,在上面這個圖我們使用Verilog-a,使用了Verilog-a以后可以看到OSC的理想模型輸出是模擬信號,然后輸入到Digital的RTL是數字信號,數字信號還是很快的,模擬信號比較慢,但是因為它已經變成了一個非0即1的或者說計算量很小的模塊,所以我們認為它計算量很小,然后把它輸入到高速的RTL模塊,這個模塊也用Verilog-a去寫。

我們可能會認為這樣的寫法會讓仿真速度大大加快,事實上它是可以加快點,但是并沒有很多,為什么呢?因為它存在模擬到數字的轉換,它在每半個時鐘都會去打斷一次,就會做模擬的計算。雖然模塊本身的模擬計算很小,但是他這個模擬計算會觸發其他所有的模擬模塊,所有模塊加起來的計算是很慢的,因此它事實上速度不會快很多。

為了加快仿真速度,我們可以用下面這種方式去寫,Oscillator用Verilog-ams,High speed analog也用Verilog-ams去寫,這樣的話在鏈路上面沒有模擬通路,所以這個鏈路用綠色去表示,它是一個Logic的信號,而不是analog,它并不會觸發模擬計算,所以會大大的加速模擬計算的速度,或者說是減少模擬計算工作量。我有一個例子,同樣的一個仿真Case用上面這種模型去寫仿真使用了大概幾天的時間,改用了下面的方法以后一個小時就可以跑完了。

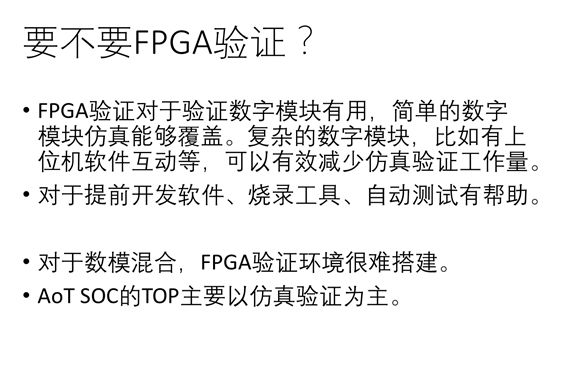

驗證的最后的一個問題是經常會聽到說要不要去做FPGA驗證?對于FPGA驗證來講去驗證數字模塊是非常有用的,因為剛才看到我們買了幾個IP是綠色的,但是藍色還是很多,這個時候FPGA驗證的應該是可以的,而且是比較有效的。事實上簡單的數字模塊的仿真驗證是能夠覆蓋的,復雜的數字模塊比如說有上位機的軟件的互動,有這些東西的話呢,FPGA驗證可以有效的減少仿真驗證的工作量,另外對于需要提前開發軟件,開發一些燒錄工具或者自動測試是有幫助的。

但是坦白講對于數模混合來講FPGA驗證環境是很難搭建的,因為對于模擬模塊來講,很難去找現成的比較接近的模塊,要去驗證它的話,需要搭建很復雜的接口,還有一些電源軌的轉換,都非常復雜,所以我們目前AOT的TOP主要是以仿真驗證為主。

經驗分享

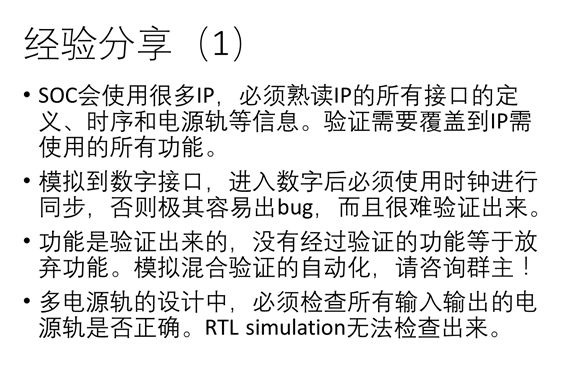

今天的分享最后講講幾個經驗:第一點是因為SOC會使用很多的IP,所以我們必須要去熟讀IP的所有的接口定義,還有它的時序跟電源軌的信息,驗證要覆蓋到我們用到IP的全部功能。這里其實有很多教訓,IP文檔讀的不夠仔細或者使用錯誤出現的問題,雖然大部分問題是可以在仿真的時候能夠驗證出來,但有的時候比較偏的一些功能沒有仿到,沒有覆蓋到,就會有問題或缺陷。

第二點是模擬到數字的接口進入數字后必須要使用時鐘進行同步,否則非常容易出Bug,而且很難驗證。因為這種Bug,只有在模擬信號正好在數字的時鐘上升沿那一瞬間來的時候變化才會遇到問題,所以很難去驗證到。

我們經常講的一點就是功能事實上是驗證出來的,某個功能沒有經過驗證,相當于說是你可以不關心或者放棄這個功能,這個時候模擬混合驗證的自動化的優勢就體現出來了,因為它能夠在一開始,即設計階段就能夠去定義哪些功能需要驗證,而不是在最后列個List一個個去檢查,因為到了那個時候是時間是非常有限的,可能來不及。

還有很重要的一點就是在多電源軌的設計當中必須要檢查所有的輸入輸出電源軌是不是正確,因為電源軌的問題RTL Simulation經常沒有辦法檢查出來。只有在模擬的仿真中才知道,比如輸出1.8V到了5V的電源軌,或者說5V的電源軌到了1.8V,那肯定器件就壞掉了。

第二再分享一個小工具,有些IP的供應商對于Standard Cell經常不提供Schematic view,這怎么辦?事實上,我們可以通過IP供應商提供的Spice model,或者說CDL網表,能夠自動的生成Schematic view。左邊是我們經常看到的一個Standard Cell的與門,可以看到里邊有網表,P管用PD來表示,N管用ND來表示,前面是它的連接,后面是W、L和multiple。在Spice in的時候,通過device map把這個MOS管PD對應成PMOS 5V的管子。可以把P管對應成PMOS 5V,然后是他的Pin order,Property需要注意一下,因為Property定義了W、L對應的是什么參數,W對應的W,L對應的L,但有的時候m要根據實際情況要去做修改,定義它的PDK里面的參數是什么。

使用了這個工具,最終導進去以后會發現雖然把W、L、m改對了,Model可能也改對了,但是其他的一些CDF參數沒有刷新,這時候怎么辦?因為如果我們光拿它來做LVS的話是不影響的,因為在LVS當中網表就是這個樣子,它只用到了這幾個參數,但是在其它電路仿真的時候如果用到Standard Cell,它的CDF參數沒有刷新的話有問題。

說明一下,CDF是PDK里邊經常看到的與器件相關的一些模擬參數,比如說Drain或者是Source的寬度,它的寄生,因為它要根據WL變化,所以它實際上是一個可變量,能把這個變量通過CDF傳遞到網表當中去。

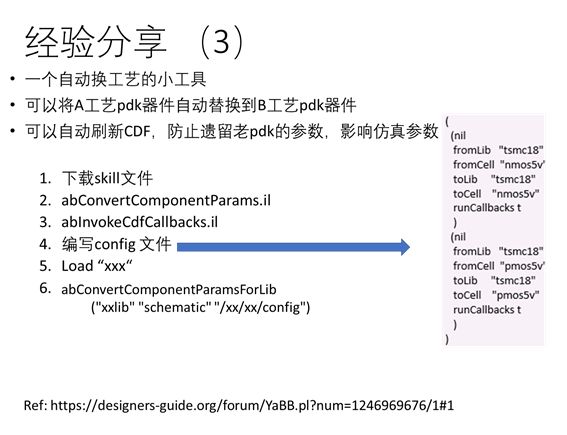

如果這個CDF沒有刷新怎么辦呢?這里有一個工具能夠去刷新這些CDF的一些參數。事實上這個工具不僅僅可以去刷新參數,還可以自動去替換工藝,這事實上是一個自動換工藝的小工具,可以把A工藝的PDK器件自動轉換到B工藝的PDK器件。

轉換以后同樣需要去刷新CDF,防止老PDK的參數影響到仿真參數。這個工具怎么用呢?可以去下載這兩個Skill文件,用搜索引擎應該能夠搜到,它的一些討論也在下面這個reference的網址當中有講到。這兩個文件里邊有說明文檔,需要去編寫這個config文件。就是A是什么工藝,把A工藝中的一個器件把它自動地換成B工藝當中的一個器件,然后再運行Callback。

我這個Config文件只是去刷新CDF的參數,所以它換成的工藝庫還是原來的工藝。有了這幾個文件,首先去Load前面兩個Skill文件,然后使用下面對整個庫進行替換的命令就可以了。

-

鋰電池

+關注

關注

259文章

8042瀏覽量

169603 -

存儲器

+關注

關注

38文章

7455瀏覽量

163623 -

AMBA總線

+關注

關注

0文章

35瀏覽量

9534 -

EEPROM

+關注

關注

9文章

1010瀏覽量

81413 -

SoC芯片

+關注

關注

1文章

608瀏覽量

34875

發布評論請先 登錄

相關推薦

求助帖!top switch反激式led驅動電源設計

SoC驗證平臺的FPGA綜合怎么實現?

如何縮短SoC的仿真時間?

SoC設計流程相關資料下載

一種數模混合SoC 設計協同仿真的驗證方法

一種數模混合SoC 設計協同仿真的驗證方法

用SystemC進行SoC的系統級設計與仿真

用于加速ARM SOC內IP模塊DSM仿真的啟動代碼設計方法

新思科技Synopsys收購SoC驗證仿真公司EVE

一文淺談SoC功能驗證中的軟件仿真

SOC TOP的設計與仿真

SOC TOP的設計與仿真

評論