偏差分類

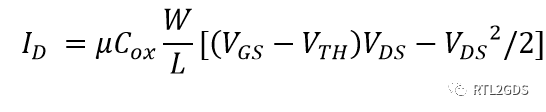

在芯片設計、制造、應用等各個環節都不可避免地會引入偏差,其直接造成的影響是晶體管、電阻電容以及繞線等電特性的不確定性。無源器件尺寸的偏差造成的影響顯而易見,那么對于有源器件,從MOS管線性區的I-V特性公式可以看出:

引入偏差的因素,主要分為工藝(Process),電壓(Voltage)和溫度(Temperature)三類,下面分別講解:

Process

公式中的遷移率、柵氧化層電容、寬長比、閾值電壓等受芯片制造過程中光刻、刻蝕、離子注入等操作精度的影響。有些偏差是系統性的,對所有芯片的影響是一致的,另一些偏差則是局部的,微觀上體現在同一顆芯片上完全相同的兩個邏輯單元表現出的電性能會有差異。

Voltage

公式中的柵極電壓,漏源電壓等與電源電壓的穩定性以及到達晶體管的電壓降(IR Drop)有關。前者是系統性的,芯片外接的電源電壓波動影響片上所有的器件,后者是局部的,微觀上體現在從電源管腳到達晶體管的IR Drop各不相同,各個區域的電流消耗不一樣也會導致IR Drop的差異。

Temperature

公式中的遷移率和閾值電壓直接受溫度變化的影響,芯片應用時的環境溫度是系統性的影響因素,在Signoff是要充分考慮,民用、軍用或者太空級別的應用場景對溫度變化范圍的要求也不同;此外,由于片上功耗分布的不均勻導致局部的溫度差異同樣需要考慮。

除了上述三個主要因素,這里還想強調兩個點:噪聲引入的偏差和時鐘偏差

Noise

這里所述的noise更多的是芯片應用時,從輸入管腳引入的噪聲,或者MOS管自身的襯底噪聲或者熱噪聲。特別是對于芯片中的模擬射頻電路,比如鎖相環,數模轉換,放大器等,噪聲是其電路設計時重點需要考慮的因素,有些是從結構的角度,有些是從工藝的角度。例如,利用差分信號可以抑制共模噪聲,增加Guide Ring可以減少外圍器件對其的噪聲干擾等等。

Clock

對于數字電路,時鐘的質量對其時序的影響非常關鍵。不管時鐘是片外輸入,還是片上PLL生成,都不是理想時鐘,會引入不確定性。其中,PLL一個很重要的指標就是jitter,而且往往大的SoC中一個源時鐘會分頻產生很多時鐘,分給不同的子系統使用,由于時鐘經歷的路徑不一樣,也會對其質量產生影響,所以設計時一般會要求設置clock uncertainty,來模擬考慮時鐘頻率不確定性的影響。

風控機制

上述的系統性偏差,一般通過不同的PVT Corners來控制,例如ssgnp0p72vm40c、tt0p8v85c 、ffgnp0p88v125c等等,他們分別對應不同的.lib庫文件,Foundary提供的Signoff Guide中一般會給出安全的Signoff Corner列表。具體關于工藝角的選擇,電壓的選擇,溫度的選擇以及RC Corner的選擇下回再展開講解。

上述的局部的偏差,一般通過OCV(On Chip Violation)機制來控制,從最早的Flat OCV,到AOCV(Advanced OCV),在到目前的POCV(Parametric OCV),一直在解放思想,釋放過約的Margin。

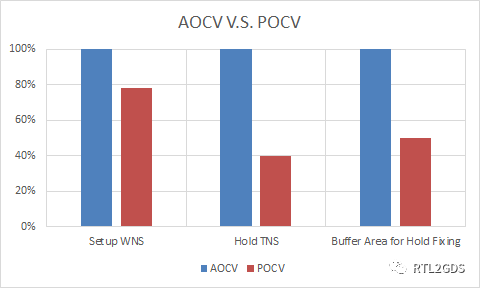

目前比較流行的POCV或SOCV,相比AOCV到底有多大的差別呢?這個需要根據情況具體分析,為了給大家更直觀的概念,下面基于某一個Post-Route的Database,分別用AOCV和POCV的方式進行STA分析,可以得出如下圖所示的比較結果:

可以看出,相比于AOCV來說,POCV降低了悲觀度,特別是對于Hold Timing,能節省很多面積和功耗。有些大公司還執著于用Flat OCV去Signoff,在先進工藝下的代價是很大,尤其是在極低電壓下。

對于噪聲引入的偏差,一方面,可以在仿真時引入噪聲源來模擬其帶來影響,另一方面,更多的是通過成功經驗得到最佳實踐的方式來控制風險。而對于時鐘頻率偏差,則可以通過設置不同的uncertainty的方式加以控制,例如根據時鐘的源頭的不同,設置不同時鐘之間的uncertainty。

此外,為了充分識別出工藝偏差對芯片的影響,在量產前,Foundary一般會要求把某些測試批次的Wafer故意往變慢或者變快的方向去調整工藝,看看哪一種方案對其芯片的影響是最優的。這也屬于流片后管控偏差風險的一部分。

-

放大器

+關注

關注

143文章

13554瀏覽量

213145 -

MOS管

+關注

關注

108文章

2397瀏覽量

66627 -

芯片設計

+關注

關注

15文章

1005瀏覽量

54819 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

電阻電容

+關注

關注

1文章

40瀏覽量

9515

發布評論請先 登錄

相關推薦

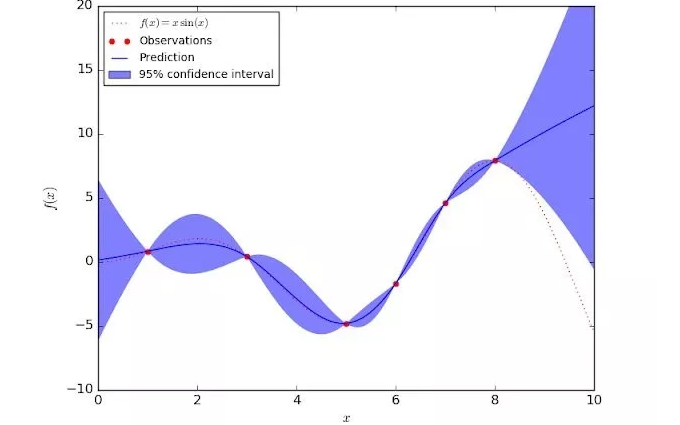

如何創造可信任的機器學習模型?先要理解不確定性

芯片Signoff是通過什么機制去控制偏差帶來的不確定性風險的?

芯片Signoff是通過什么機制去控制偏差帶來的不確定性風險的?

評論