T觸發(fā)器是一種可以切換其輸出的人字拖。切換意味著將其輸出切換到相反的輸出;1 變?yōu)?0,0 變?yōu)?。這種類型的觸發(fā)器通常用于計數(shù)器和分頻器。

在本快速入門教程中,你將了解其工作原理、真值表以及如何生成真值表。

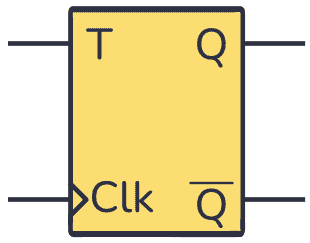

T 觸發(fā)器符號

什么是 T 字拖?

觸發(fā)器是通常用于在其輸出上存儲數(shù)字值的組件。它們有一個時鐘 (Clk) 輸入,用于決定何時更新其輸出。

T 觸發(fā)器是一種單輸入觸發(fā)器,可保存或切換其輸出值。

切換,這是名稱中“T”的原因,意味著在兩種狀態(tài)之間切換。如果輸出為 1,則切換會將輸出更改為 0。如果輸出為 0,切換會將輸出更改為 1。

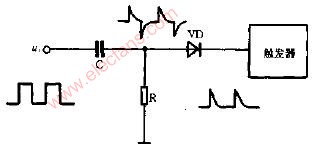

您可以從其他人字拖構(gòu)建 T 觸發(fā)器,例如通過使用 JK 觸發(fā)器并連接 J 和 K 輸入,如下所示:

T型觸發(fā)器電路設計

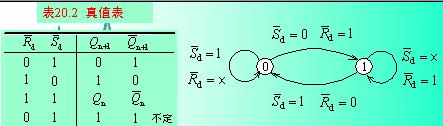

真值表

一般來說,您可以使用下降沿信號觸發(fā) T 觸發(fā)器,這是從數(shù)字狀態(tài) 0 到 1 ↓ 的變化,或者使用上升沿信號,從 1 到 0 ↑

的變化。以下真值表對應于在上升沿觸發(fā)的觸發(fā)器:

您可以看到,如果Clk輸入中沒有上升沿,無論您放入T輸入什么,Q輸出都將保持不變。

與前一種情況類似的情況發(fā)生在 T 輸入中有 0 時。即使觸發(fā)器被觸發(fā),如果Q輸出中有0或1,它也會保持這種狀態(tài)。

要獲得切換行為,您必須在 T 輸入中放置一個 1。您將觀察到每次觸發(fā)觸發(fā)器時從 0 到 1 或從 1 到 0

的變化。您可以在下面的時序圖中看到此行為:

T型觸發(fā)器的時序圖

構(gòu)建T型觸發(fā)器電路

您可以通過短路 JK 觸發(fā)器的 J 和 K 輸入來構(gòu)建 T

觸發(fā)器。但是,一些網(wǎng)站建議您構(gòu)建如下所示的電路。但這是一個不完整的電路,無法正常工作:

在紙面上,它似乎有效。但是大多數(shù)發(fā)布此電路的網(wǎng)站沒有提及的是,您需要一個非常短的時鐘脈沖才能工作。

在輸出 (Q)

改變狀態(tài)之前,時鐘脈沖需要變?yōu)楦唠娖剑缓笤俅巫兊汀7駝t,Q輸出將在整個正脈沖持續(xù)時間內(nèi)在1和0之間快速切換。您可以在以下時序圖中看到此行為:

這是一個叫做賽車的問題。但是通過使用邊緣觸發(fā)的JK Flip-Flop很容易解決。

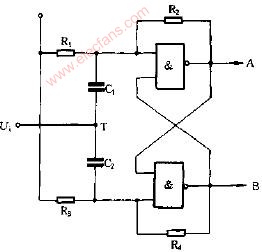

您還可以通過將 D 觸發(fā)器與 XOR 門結(jié)合使用來構(gòu)建功能齊全的 T 觸發(fā)器,如下所示:

邊緣觸發(fā)T觸發(fā)器電路

邊緣觸發(fā)T觸發(fā)器電路

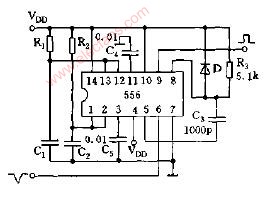

示例電路:切換 LED

舉一個實際的例子,你可以只使用一個按鈕、T Flip-Flop和一些電阻來切換發(fā)光二極管(LED)。查看以下電路:

您可以看到T輸入如何連接到5V,這意味著邏輯1。因此,每次觸發(fā) T 觸發(fā)器時,Q 輸出都會切換其狀態(tài)。

Clk 輸入使用下拉電阻配置,這意味著只要不按下按鈕,Clk 輸入為 0。當您按下按鈕PB1時,Clk輸入將從0變?yōu)?(上升沿信號)。

因此,每次按下PB1時,連接到輸出Q的LED都會打開或關閉。

要組裝上述電路,您需要:

1x T 觸發(fā)器電路(例如,通過組合 CD4013 和 CD4030 )

2x 10 kΩ電阻(R1和R2)

1x 330 Ω電阻器 (R3)

1x 按鈕

-

電路圖

+關注

關注

10324文章

10718瀏覽量

528246 -

真值表

+關注

關注

0文章

25瀏覽量

15165 -

觸發(fā)器

+關注

關注

14文章

1996瀏覽量

61053 -

時序圖

+關注

關注

2文章

57瀏覽量

22439

發(fā)布評論請先 登錄

相關推薦

零基礎學FPGA(二)關于觸發(fā)器

時序邏輯電路的概述和觸發(fā)器

R-S觸發(fā)器真值表 R-S觸發(fā)器工作原理及邏輯功能

JK觸發(fā)器 D觸發(fā)器 RS觸發(fā)器 T觸發(fā)器 真值表

單穩(wěn)態(tài)觸發(fā)器電路圖

CMOS觸發(fā)器的結(jié)構(gòu)與工作原理

rs觸發(fā)器電路圖與rs觸發(fā)器內(nèi)部電路圖

T觸發(fā)器的速入門教程(工作原理/真值表/時序圖/電路圖)

T觸發(fā)器的速入門教程(工作原理/真值表/時序圖/電路圖)

評論