JK觸發(fā)器是一種可以設置、重置和切換的人字拖。它可用于制造計數器、事件檢測器、分頻器等等。

在本教程中,您將了解它的工作原理、其真值表以及如何使用邏輯門構建一個。

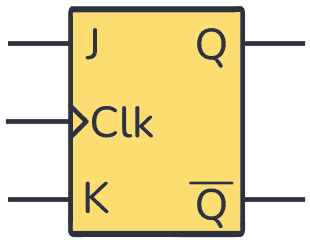

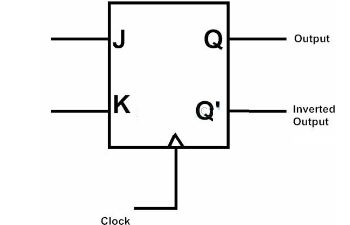

JK 觸發(fā)器符號

JK 觸發(fā)器符號

什么是 JK 觸發(fā)器?

觸發(fā)器是可以在其輸出上存儲數字值的組件。它們有一個時鐘輸入(Clk),用于確定何時可以更改輸出狀態(tài)。

與你的想法相反,JK

Flip-Flop的兩個輸入“J”和“K”并不是引腳功能的縮寫(S-R鎖存器就是這種情況)。它們的發(fā)明者杰克·基爾比(JK)選擇了它們,以將他的人字拖設計與其他類型的人字拖設計區(qū)分開來。

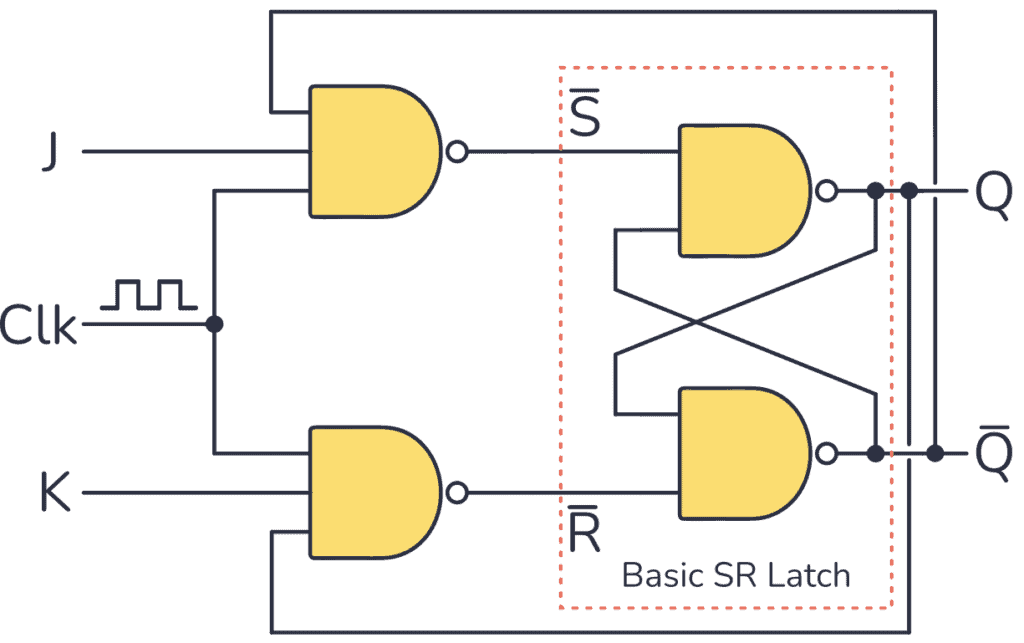

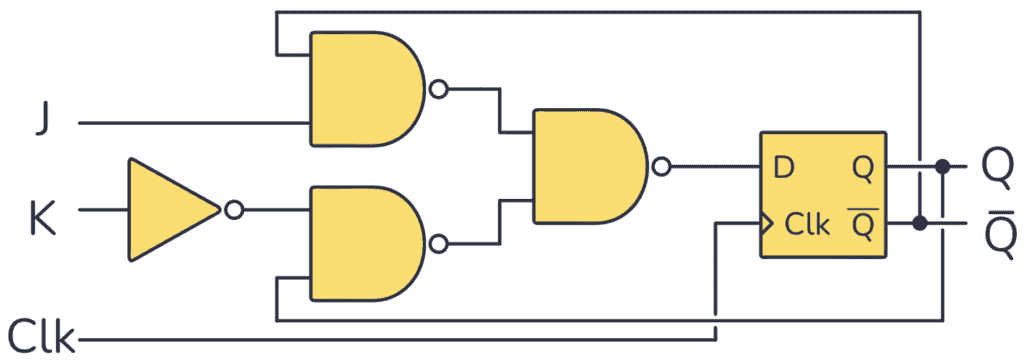

您可以在下面看到該電路的基本實現。它基于 S-R 鎖存器,采用 NAND 門構建:

JK觸發(fā)器基本電路

JK觸發(fā)器基本電路

JK 觸發(fā)器的 J 和 K 輸入可用于設置、復位或切換輸出,如下所示:

J=1 和 K=0 將輸出設置為 1

J=0 和 K=1 將輸出復位為 0

J=1 和 K=1 切換輸出

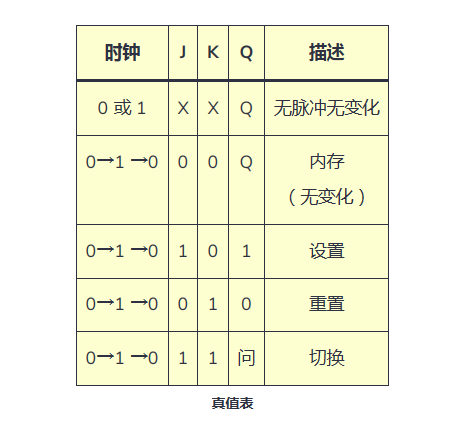

但要使觸發(fā)器進行任何更改,其時鐘輸入必須為 1。查看下面的真值表:

時鐘JKQ描述

0XXQClk in 0 Q 無

變化

100Q內存

(無變化)

1101設置

1010重置

111問切換

JK 觸發(fā)器真值表

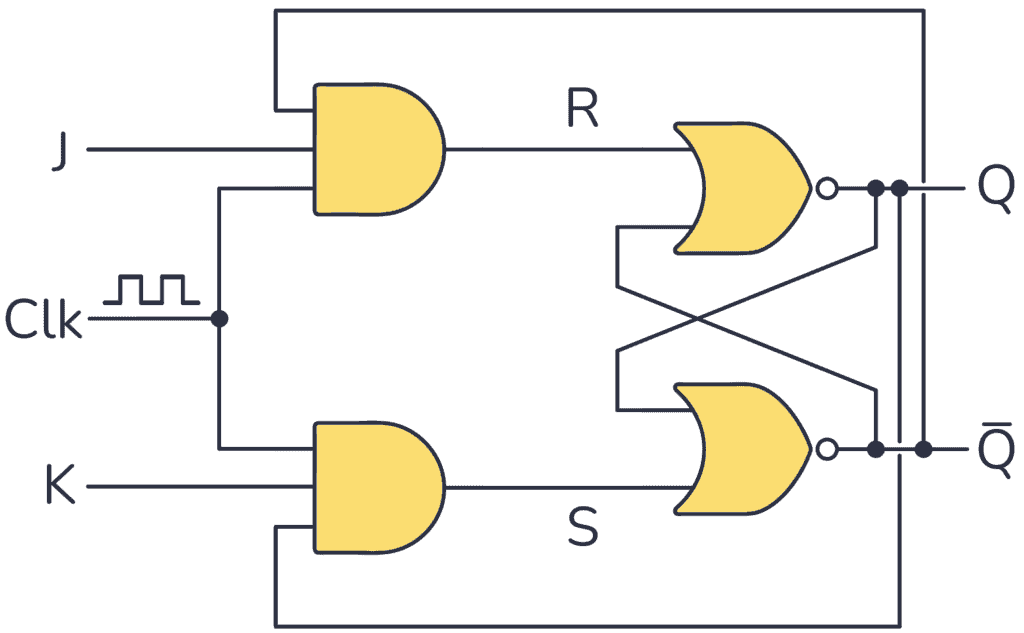

實現基本JK觸發(fā)器電路的另一種方法是使用兩個AND門和兩個NOR門,如下所示(它的工作原理與使用NAND門構建的完全相同):

賽車問題

原則上,上述基本實現有效,但會出現時序問題。當時鐘為“1”并且您想切換輸出時,它將在“1”和“0”之間快速切換,直到時鐘回到“0”。此問題稱為爭用條件。

您可以通過使觸發(fā)器脈沖觸發(fā)或邊緣觸發(fā)來解決此問題。

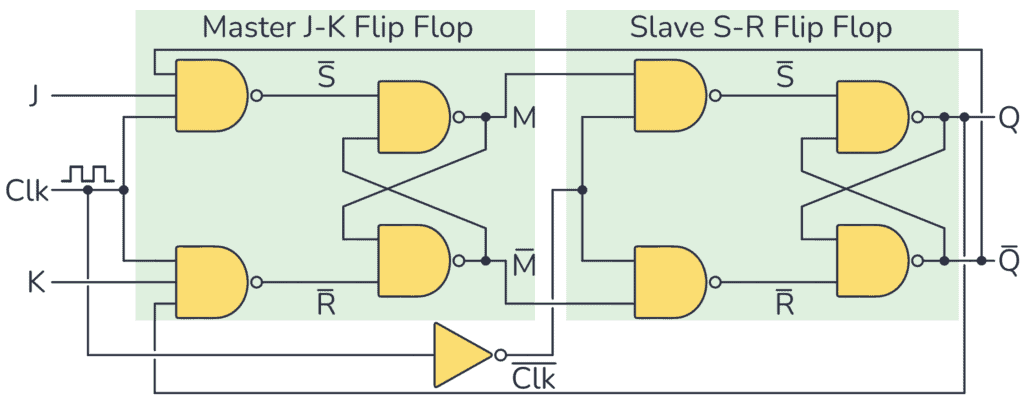

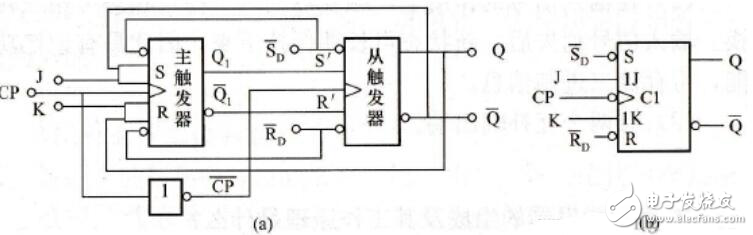

脈沖觸發(fā) JK 觸發(fā)器

下面是一個基于主從原理的脈沖觸發(fā) JK 觸發(fā)器:

主從電路

主從電路

如您所見,要構建此配置,您需要一個基本的 JK 觸發(fā)器電路,該電路與 S-R 觸發(fā)器連接在一起。

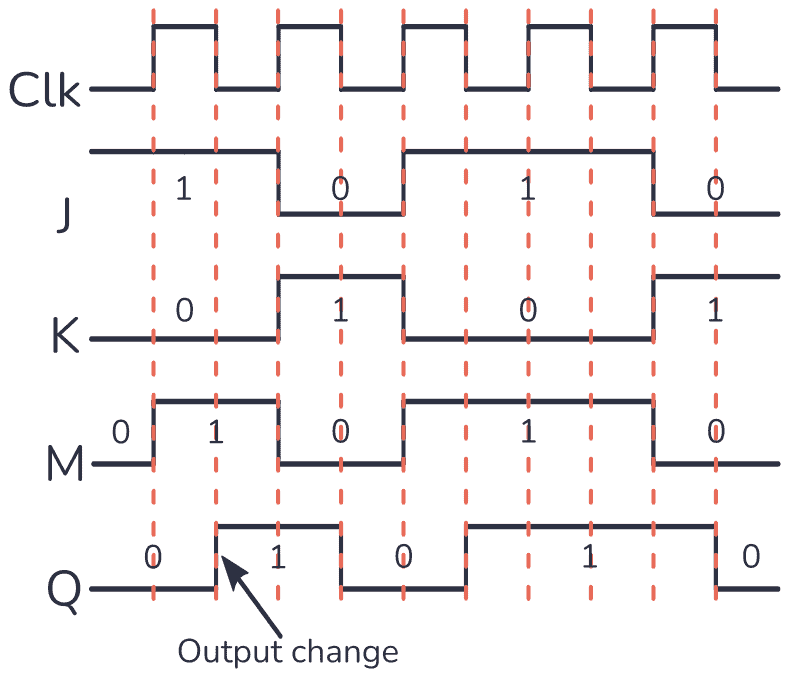

要了解此版本的工作原理,請查看下面的時序圖:

一旦時鐘產生上升沿 ↑,即從 0 到 1 (0→1

的變化),它就會觸發(fā)主部分。因此,此部分中輸出的值會更改。這些信號連接到從部分,但這不會在上升沿觸發(fā),因為時鐘已經反轉。

一旦時鐘信號產生下降沿↓,從1變?yōu)?(1→0),就會觸發(fā)從機部分,使Q輸出反映主機的輸出值。

因此,該電路需要一個完整的脈沖(0→1→0)才能改變輸出。這就是為什么這種配置被稱為脈沖觸發(fā)的JK觸發(fā)器。

邊緣觸發(fā) JK 觸發(fā)器

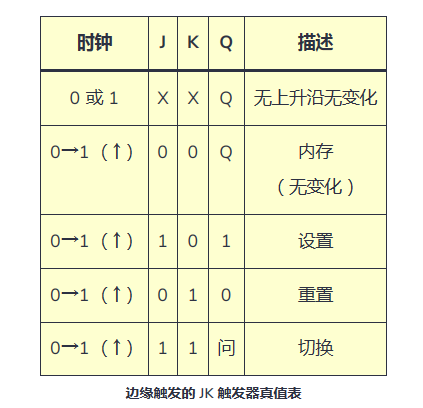

與需要完整脈沖的主從設計不同,您還可以構建從上升沿 ↑ 或下降沿 ↓ 觸發(fā)的邊沿觸發(fā)設計。

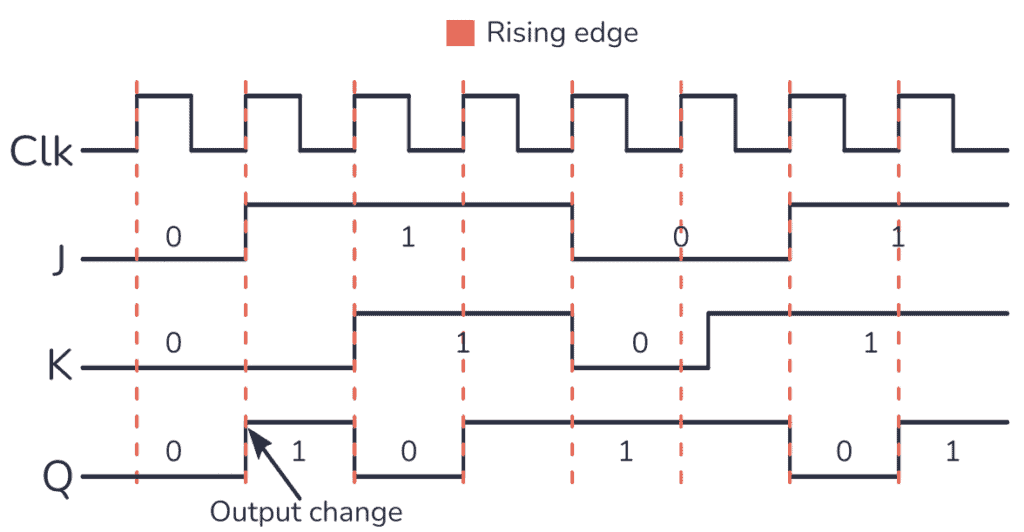

下面是在上升沿觸發(fā)的時序圖:

上圖顯示了該電路如何只需要Clk輸入上的上升沿來改變輸出Q的狀態(tài)。它只會在上升沿發(fā)生變化。

要構建僅由上升沿信號觸發(fā)的 JK 觸發(fā)器,您可以使用上升沿觸發(fā)的 D 觸發(fā)器、NOT 門和 NAND 門,如下所示:

邊緣觸發(fā) JK 觸發(fā)器電路

-

真值表

+關注

關注

0文章

25瀏覽量

15087 -

觸發(fā)器

+關注

關注

14文章

1990瀏覽量

60876

發(fā)布評論請先 登錄

相關推薦

R-S觸發(fā)器真值表 R-S觸發(fā)器工作原理及邏輯功能

JK觸發(fā)器基本教程,講的超詳細!!

JK觸發(fā)器 D觸發(fā)器 RS觸發(fā)器 T觸發(fā)器 真值表

JK觸發(fā)器原理是什么?

jk觸發(fā)器是什么原理_jk觸發(fā)器特性表和狀態(tài)轉換圖

JK觸發(fā)器的工作原理及真值表

JK觸發(fā)器的工作原理及真值表

評論