我們常用的debug UVM的方法是通過打印log實現。有沒有辦法像 debug RTL代碼一樣將 UVM 中變量拉到波形上看呢?答案是有的,下面讓我們看看是怎么做到的。

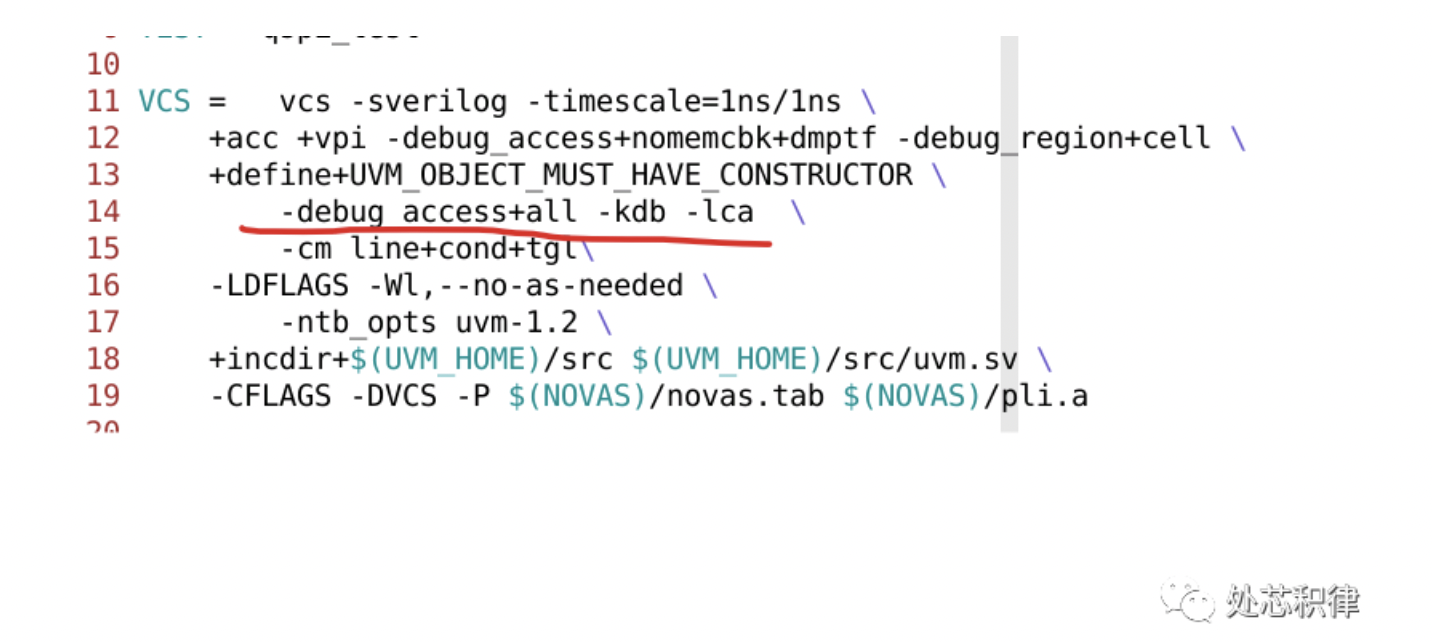

第一步在UVM compile 的選項里面加入 -debug_access+all

第二步在 simulation 選項中加入下面三個選項

-gui=verdi

** +UVM_VERDI_TRACE="UVM_AWARE+RAL+HIER+COMPWAVE"**

+UVM_TR_RECORD

這里 -gui=verdi是啟動verdi 和vcs聯合仿真。+UVM_VERDI_TRACE 這里是記錄 UVM中 register,component 的波形。+UVM_TR_RECORD記錄 transaction的信息。

我們 編譯完之后,然后開始跑仿真。跑仿真的時候會跳出下面verdi的界面。

接下來點擊綠色的箭頭就可以跑仿真

跑完仿真之后,我們點擊Verdi 里面 UVM這個地方,會出現UVM的環境。

下面我們看下 uvm component里面的信息,通過指定一個 component 然后右擊 add to waveform 就可以看 component的信息。

Sequence里面的信息怎么看呢?下面點擊sequence view 就可以看 sequnce的信息。

我們要看sequence里面的一個變量變化,可以這么做。

先將一個object或者一個sequence 添加到watch中。

從這個watch中的object或者sequence里面選擇一個變量到 waveform上。重跑simulation,就可以看到對應添加變量的值值。

下面是我們在波形上看到sequence里面變量的信息

看register model里面的值也是類似的做法,找到 register view,然后找到 register model 添加 register 到 waveform里面。

重跑simulation,就可以看到register值。

用verdi debug UVM總體感覺比較麻煩,個人還是喜歡打印log的方式debug。

-

仿真器

+關注

關注

14文章

1016瀏覽量

83638 -

RTL

+關注

關注

1文章

385瀏覽量

59701 -

UVM

+關注

關注

0文章

181瀏覽量

19139

發布評論請先 登錄

相關推薦

有沒有辦法像debug RTL代碼一樣將UVM中變量拉到波形上看呢?

有沒有辦法像debug RTL代碼一樣將UVM中變量拉到波形上看呢?

評論