時鐘門控(Clock Gating) 是一種在數(shù)字IC設計中某些部分不需要時關閉時鐘的技術。這里的“部分”可以是單個寄存器、模塊、子系統(tǒng)甚至整個SoC。

**為什么需要時鐘門控:**大多數(shù)SoC都是 power constrained ,mobile端不能夠充更多的電就只能盡可能地降低功耗了( 無法開源只能節(jié)流呀 ),也因為時鐘門控是降低芯片動態(tài)功耗最簡單,最常用的方法之一。

時鐘門控技術分類: 通常,有兩種不同的時鐘門控實現(xiàn)技術。

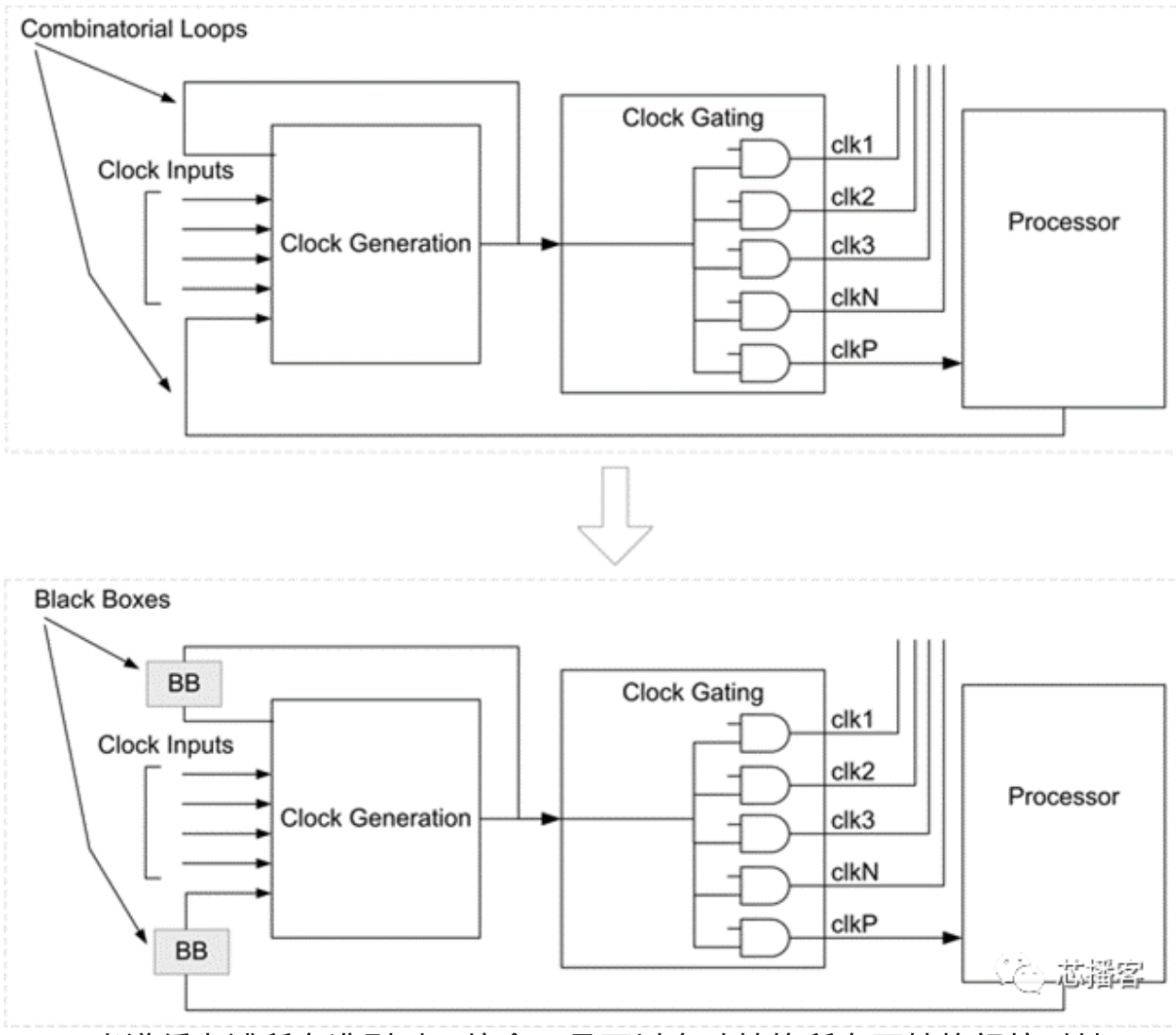

combinational clock gating –這種類型的時鐘門控由工具在綜合時自動識別引入。

**sequential clock gating ** –這種類型的時鐘門控作為功能的一部分引入RTL設計中。通常時鐘門控策略在系統(tǒng)架構中定義,然后由設計人員進行實現(xiàn)。

combinational clock gating

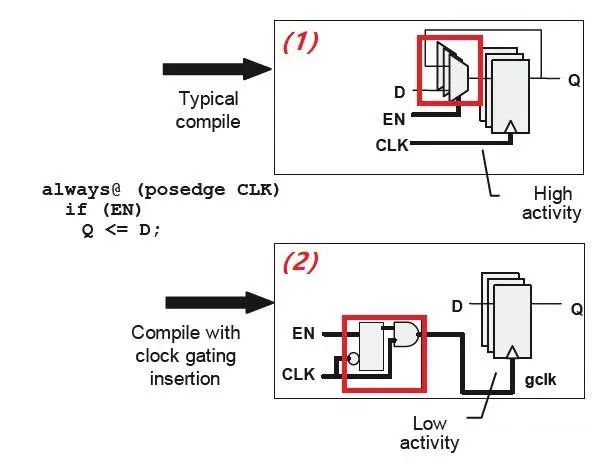

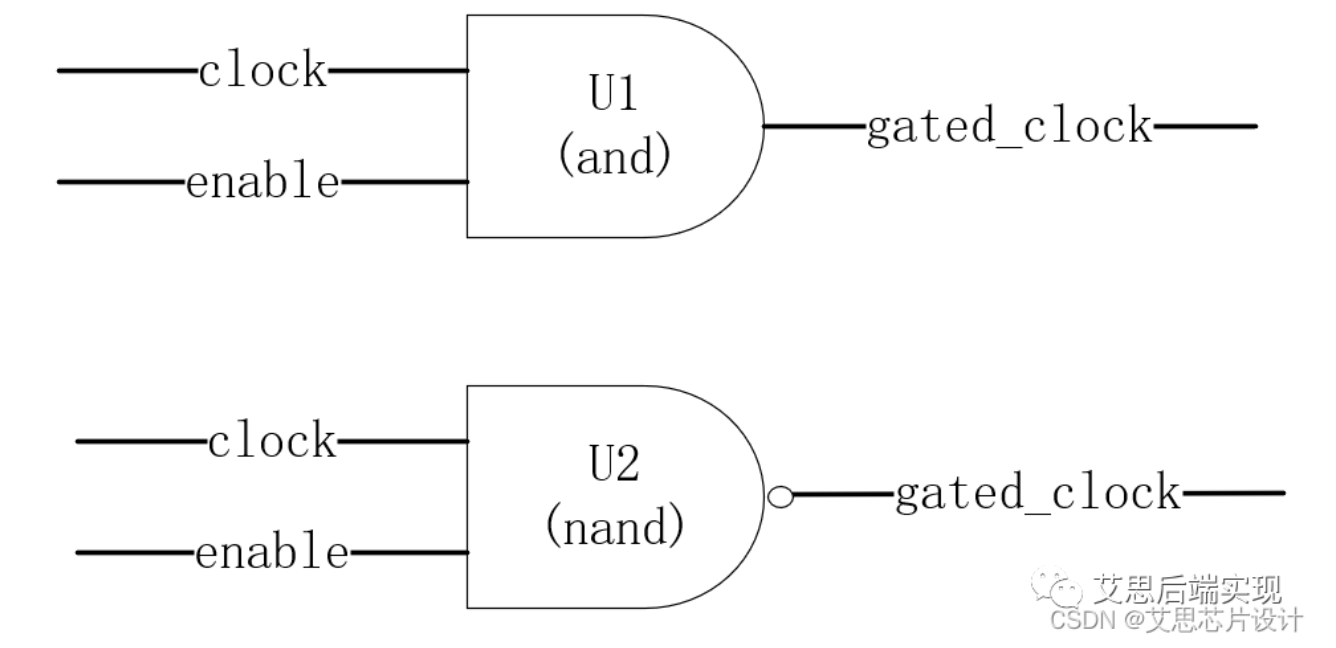

最簡單的combinational clock gating可以通過AND門實現(xiàn),如下圖所示

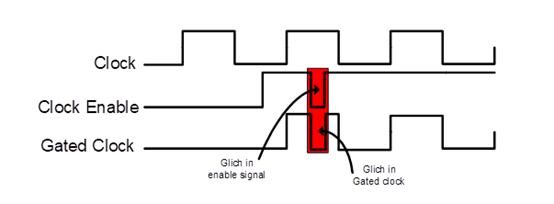

當enable為1時,時鐘會傳給寄存器FF;當enable為0時,時鐘將被關閉, FF將不起作用。這種最簡單的時鐘門控技術形式存在一些問題,即在提供給FF的時鐘中產生毛刺。

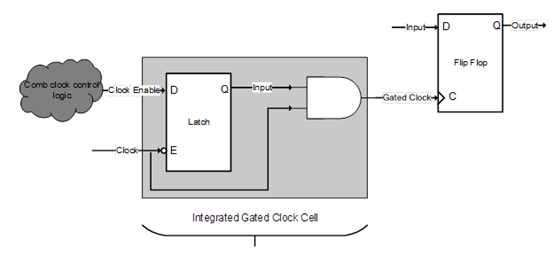

可以通過在時鐘使能信號的輸出端引入一個低電平敏感的鎖存器來解決這個問題。

鎖存器輸出僅在時鐘低電平內更新,因此與門的輸入將穩(wěn)定為高。

Integrated Gated Clock Cells(ICG Cell)

要實現(xiàn)這種時鐘門控可以實例化標準單元庫中的兩個Cell(Latch和AND門),秉著不重復造輪子的思想以及方便工具進行后續(xù)的時序分析更建議使用庫中的ICG Cell并且由工具自動綜合插入。

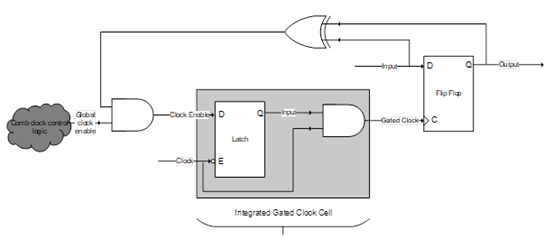

時鐘使能信號可以由軟件控制和硬件同時控制,即由軟件控制是否需要啟動時鐘門控,硬件動態(tài)控制時鐘使能。

軟件控制示例如下:

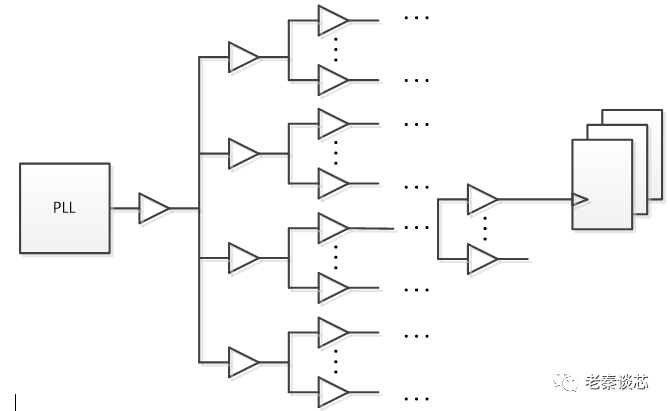

軟件控制這個全局時鐘使能信號, 為低電平時不打開時鐘門控 ,這種全局時鐘門控使能策略可以進行層次化的設計,從系統(tǒng)級到最終的單個寄存器。

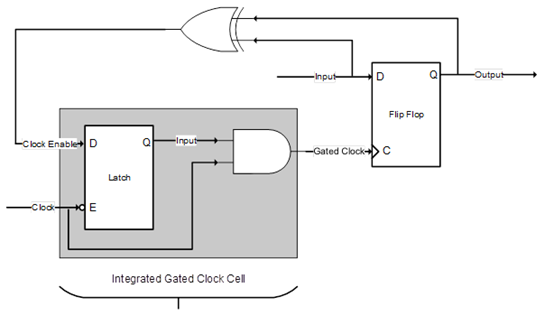

硬件控制示例如下:

XOR門的輸入連接到FF的輸入和輸出。如果FF的輸入和輸出相同,則無需觸發(fā)FF,此時可對時鐘進行門控。

在前端RTL級引入combinational clock gating很簡單,沒有對邏輯功能產生影響,可以由EDA工具自動插入。但是 在物理設計的視角 ,這可能是一個更大的課題,因為我們引入了一個實實在在的物理cell,更何況還是在時鐘路徑上。

從時序功耗上, clock gating應該離寄存器時鐘端遠還是近?

從面積功耗上,只有一個寄存器是否應該被門控?

sequential clock gating

除了上述combinational clock gating外,還有sequential clock gating,這涉及對RTL設計中多個時鐘周期進行深入分析。當然基本思想也很簡單,如果寄存器X在周期C中未更新,并且在時鐘周期C + 1中輸入給寄存器Y的D端,則無需在周期C + 1中使能寄存器Y的時鐘。

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

IC設計

+關注

關注

37文章

1292瀏覽量

103780 -

SoC芯片

+關注

關注

1文章

608瀏覽量

34875 -

鎖存器

+關注

關注

8文章

905瀏覽量

41448 -

時鐘門控

+關注

關注

0文章

7瀏覽量

6814

發(fā)布評論請先 登錄

相關推薦

fpga門控時鐘問題

什么是時鐘門控?如何去實線時鐘門控的設計呢

基于門控時鐘的CMOS電路低功耗設計

門控時鐘與時鐘偏移研究

通常有兩種不同的時鐘門控實現(xiàn)技術

什么是門控時鐘 門控時鐘降低功耗的原理

門控時鐘實現(xiàn)低功耗的原理

什么是門控時鐘?如何生成門控時鐘?

FPGA原型平臺門控時鐘自動轉換

為什么需要時鐘門控?時鐘門控終極指南

為什么需要時鐘門控?時鐘門控終極指南

評論