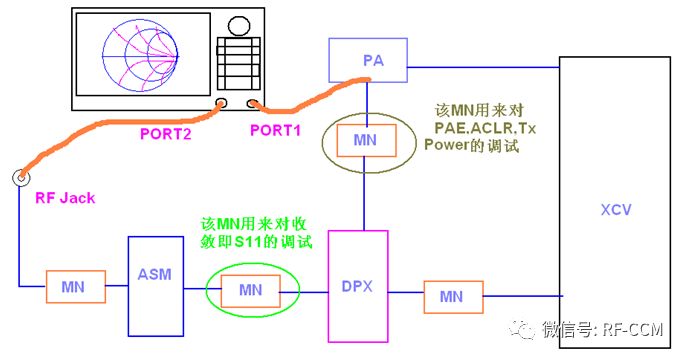

PA 調試block

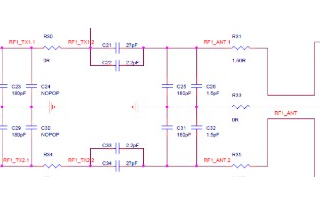

圖1 RF Block

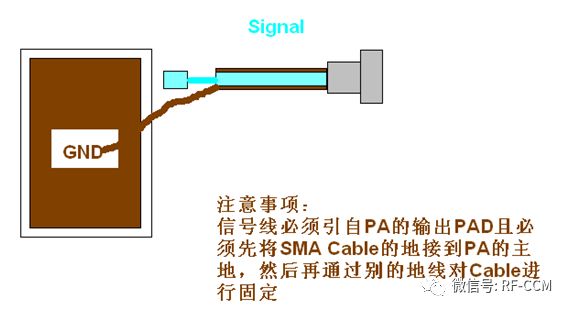

PA RF cable焊接

圖2 PA接線方式

PA匹配****調試具體步驟如下:

- 校準VNA并做測試Cable的延遲校準。即將Cable連接到VNA后通過校準程序,將其校準到Smith Chart右端開路點,完成延遲補償

- 焊接Cable,如上圖2注意事項,先將PA用熱風槍拿掉,然后將Cable的信號線接到PA的輸出引腳PAD上,將Cable的地接到PA封裝的主地上。然后再連到易于連接到的地上固定Cable。

- 以上圖1示例如何調試PA,上圖1的VNA兩個端口接線分別為Port1→PA output PAD,Port2→RF Jack,所以S11即從PA output到RFJack的收斂性。而S21為Port1到Port2的IL(好的IL通常為3.2左右的樣子),S21可用來判斷測試路徑是否是通的。

若收斂差的話則需要調節DPX ANT端口的MN,調試完DPX ANT端口的MN后還需確定是否對Rx Path產生影響。因為Port1在PA輸出端,Port2在RFJack端,所以通過匹配,可以調試整條Tx鏈路的收斂,Tx Path的收斂決定了功率的平坦度。

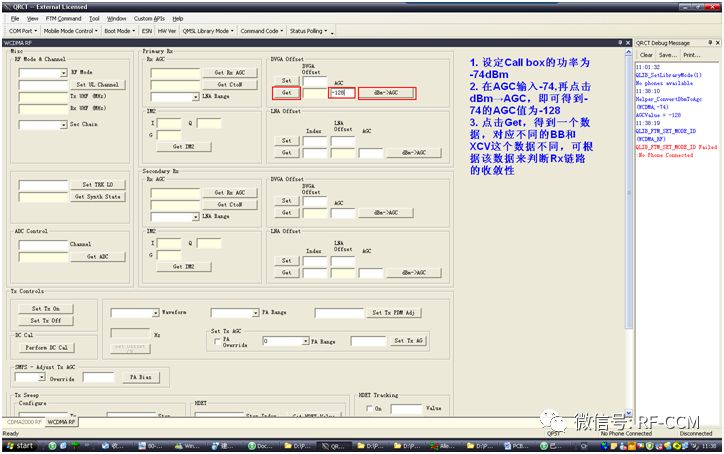

如下圖示可用來確認Rx Path的影響。因為這樣調試的時候S11經過了DPX,所以在調試收斂的時候不能以常規的并/串元件在Smith Chart上移動的方向來確認S11,經過DPX后很難預測S11走向,調試后需要用VNA進行驗證。

- 經常會遇到ACLR的問題,首先可以盲調PA的MN,若是PA的MN與PA放置較遠的話可以考慮并聯電感,若是緊挨PA放置的話并聯電感的效果較差。再就是找多家PA看看,最后查看PA供電是否穩定,電源是否受到干擾。

- 對比廠商提供的Load Pull的數據調試對應的MN來 優化ACLR,PAE,Tx Power要做好三者的均衡 ,通常按中信道Load Pull數據來調試PA輸出的MN,在實際信令情況下測試時候需看三個信道的具體情況。

由于要考慮高低溫,所以對ACLR應留有足夠的余量,溫度會對ACLR影響較大。

考慮到溫度上升帶來的Noise影響,估計能惡化2dB的ACLR性能,但是HSDPA由于其高的PAPR,所以對于HSDPA高溫時候ACLR的惡化不便于估計,盡量調試ACLR<-39。實際中遇到過在用RFMD的7225調試時候,不管怎么改變匹配電路,其ACLR的變化很少。考慮兩個方面:

1 PA電源問題

但是W2100&W1900均用同一組電源,這兩個Band的ACLR均<-40,所以考慮電源問題似乎不太合適。

2.器件本身問題

經調試MN無效后更換該PA為ANADIGICS的AWU6605后其ACLR表現極佳,±5M為-47~-48,所以該問題是器件本身性能不太理想,再加之PCB Layout的寄生影響導致ACLR結果不如意。

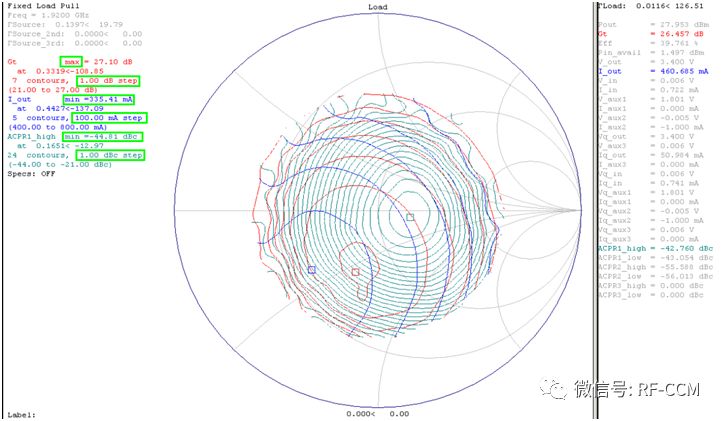

PA Loadull示例

藍框:如上圖左所示為電流最小的點,藍色的等高線代表了等電流點,100.0mA每Step

紅框 :如上圖左所示為功率最大的點,紅色線等高線代表了等功率點,各等高線間的間隔為1dB

綠框 :如上圖左所述為ACLR最小的點,水綠色等高線代表了等ACLR點,各等高線間隔為1.00dBc

三個框會圍成一個三角形,將PA的load往三角形內調是均衡三者的性能表現。

具體情況,具體參考loapull分析調試。

盲調小修是必要的。

-

RFMD

+關注

關注

1文章

71瀏覽量

21627 -

HSDPA技術

+關注

關注

0文章

3瀏覽量

5350 -

VNA

+關注

關注

0文章

33瀏覽量

16414 -

DPX

+關注

關注

0文章

4瀏覽量

8891 -

ACLR

+關注

關注

0文章

11瀏覽量

8087

發布評論請先 登錄

相關推薦

聊聊Rust與C語言交互的具體步驟

請問UCGUI中移植觸摸的具體步驟是什么?

阻抗匹配調試方法能改善嗎?

STM32新建工程具體步驟

學電機的具體步驟

西門子V20變頻器PID控制恒壓供水的具體步驟

PA匹配調試具體步驟

PA匹配調試具體步驟

評論