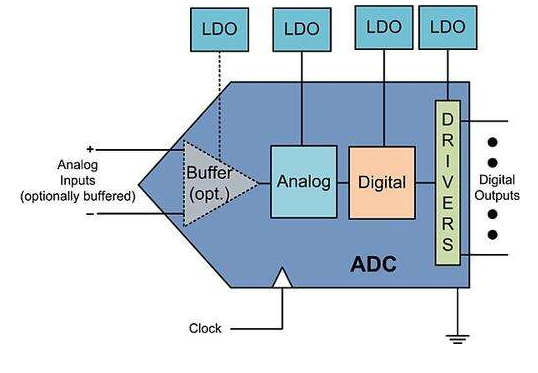

考慮到當前可用ADC的采樣速度以及典型ADC內部許多不同的電壓和時鐘域,通常建議在電源輸入中保持分離。通過將電源輸入保持在單獨的域上,可以最大限度地減少電源之間的串擾,并且噪聲在域之間的交叉時間要困難得多,在域之間可能會蔓延并導致ADC性能問題。如果無法將它們保存在單獨的域上,則至少可以使用鐵氧體磁珠等元件在電源域之間提供一些隔離。單獨驅動電源輸入的一種方法是使用低壓差(LDO)穩壓器。下面的示例如圖 1 所示。

圖1

使用單獨的LDO驅動ADC電源。

LDO通常是最安全的電源類型,在驅動ADC的電源輸入時通常風險最小。通常,LDO 具有非常低的噪聲和高電源抑制比 (PSRR)。低壓差通常意味著LDO的輸入電源可以比LDO的輸出電壓低至幾百毫伏。例如,ADP1741 2A LDO的裕量可低至400 mV(Vin必須比Vout大400 mV)。對于ADC上可能遇到的1.8 V典型電源軌,這意味著LDO的效率約為Vout/Vin = 1.8/2.2 = 81.8%。

這絕不是低效的,但正如我們將在我即將發布的博客中發現的那樣,我們可以使用更高效的器件來驅動ADC電源輸入。但是,這些其他設備的效率是有代價的。正如我所提到的,LDO的兩個主要優點是低噪聲和高PSRR。其他器件通常在噪聲換取效率方面。

對于ADP1741,輸出電壓為10.100 V時,65 Hz至2 kHz之間的輸出噪聲典型值為5 μVrms。讓我們看一下此貢獻的影響示例。在輸入滿量程為14.250 Vpp、SNR為2 dB的0位70 MSPS ADC中,本底噪聲為20 nVrms/rt-Hz。在第一個奈奎斯特區,ADC噪聲將為223.61 μVrms(20 nVrms/rt-Hz * sqrt(250 MHz/2))。在這種情況下,ADP1741的輸出噪聲遠小于ADC噪聲。此外,ADC的PSRR(典型值為60 dB)將進一步降低ADP1741噪聲,從65 μVrms降至65 nVrms (65 μVrms X 1 mV/V)。這樣就很容易理解為什么LDO是驅動電源輸入的好選擇。它對ADC噪聲幾乎沒有影響。

但是,這確實是有代價的。使用LDO的一個明顯缺點是潛在的功耗。例如,讓我們看一下上面示例中的14位ADC,并假設它是一個四通道器件,總功耗為2 W,其中AVDD電源需要1 W。在本例中,我們對LDO的輸入電源有限,只有6 V輸入可用于驅動1.8V AVDD電源。這意味著ADP1741需要耗散大約(6 V – 1.8 V)/1800 mA = 2.33 W的功率。這會將ADP1741的最大結溫(Tj)推高至TA + Pd X Θja = 85°C + (2.33 W X 42°C/W) = 183°C,超過LDO的最高額定值150°C。

當然,這是一個極端的例子,但它說明了LDO需要低輸入電壓的意義。這可能導致使用多個LDO將電壓從較高的輸入電源軌降壓到ADC所需的較低輸入電源軌。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17605瀏覽量

249562 -

ldo

+關注

關注

35文章

1919瀏覽量

153190 -

adc

+關注

關注

98文章

6452瀏覽量

544147

發布評論請先 登錄

相關推薦

ADC接口:電源,第1部分

ADC接口:電源,第1部分

評論