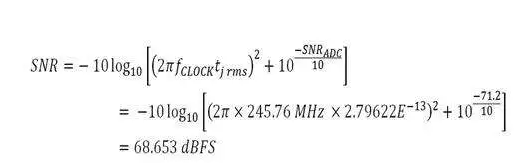

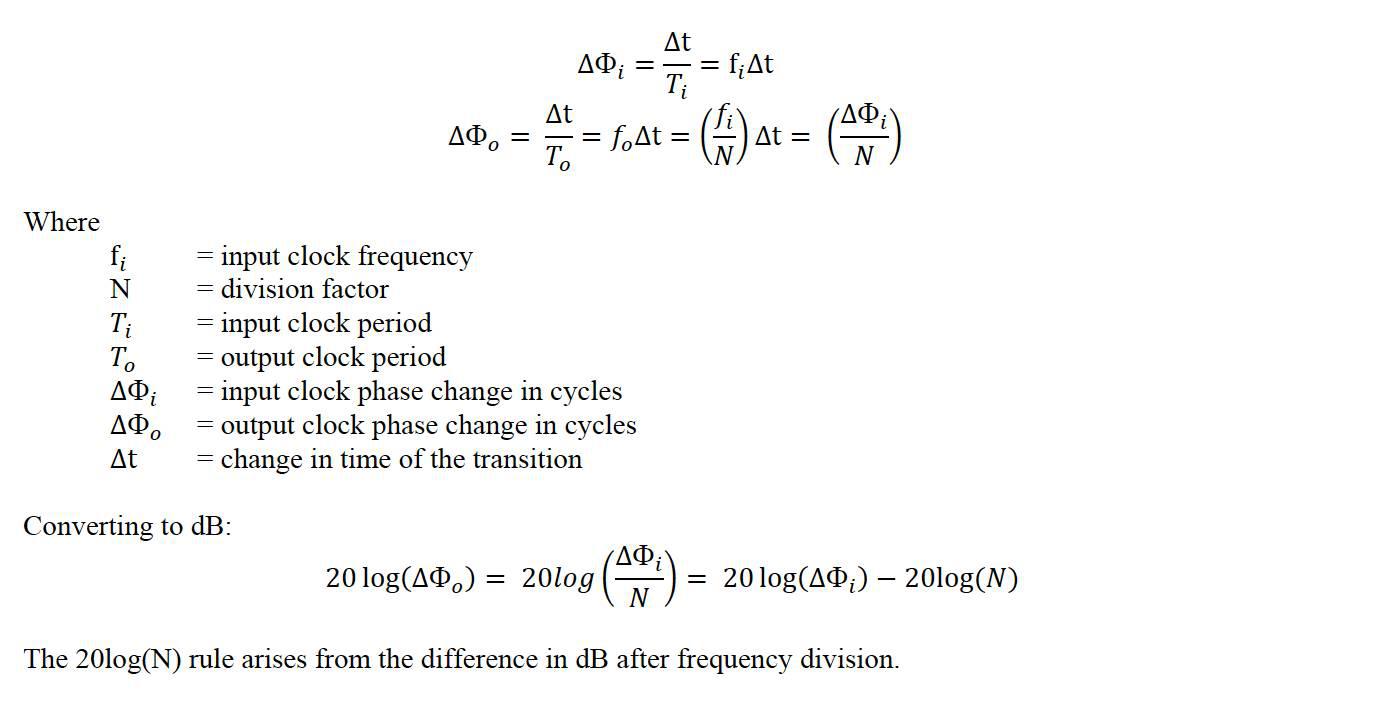

在本例中,我們將研究如何利用低抖動時鐘發(fā)生器AD9643對雙通道14位250 MSPS ADC進行計時。使用這些特定產品的常見時鐘頻率為9523.245 MHz,因此我們將為AD76使用30.72 MHz基準電壓源(外部振蕩器),并設置內部寄存器,為AD9523生成低抖動時鐘輸出。現(xiàn)在讓我們回顧一下我們上次看到的抖動方程:

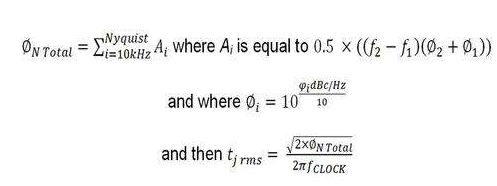

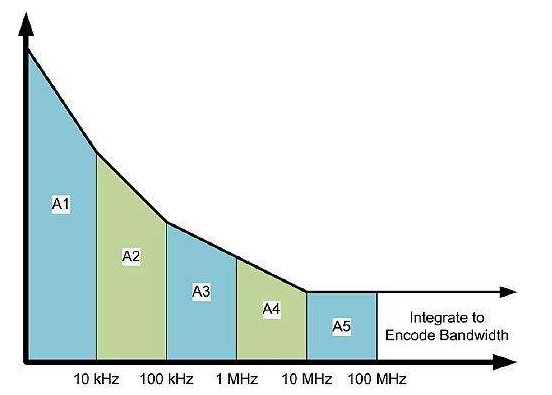

回想一下,我提到過,我們可以使用近似值來預測時鐘源抖動對SNR的影響。我提到寬帶相位噪聲是最重要的。我們可以使用AD9523從10 MHz偏移到編碼帶寬(245.76 MHz)的寬帶相位噪聲來預測ADC的SNR,如圖1所示。

圖1.編碼帶寬內的相位噪聲近似

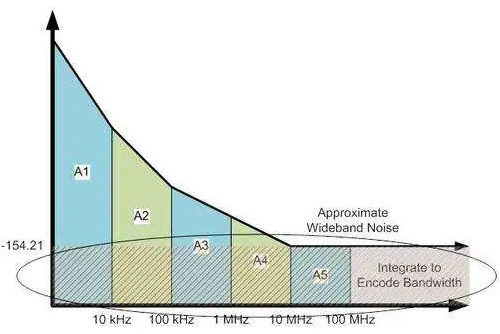

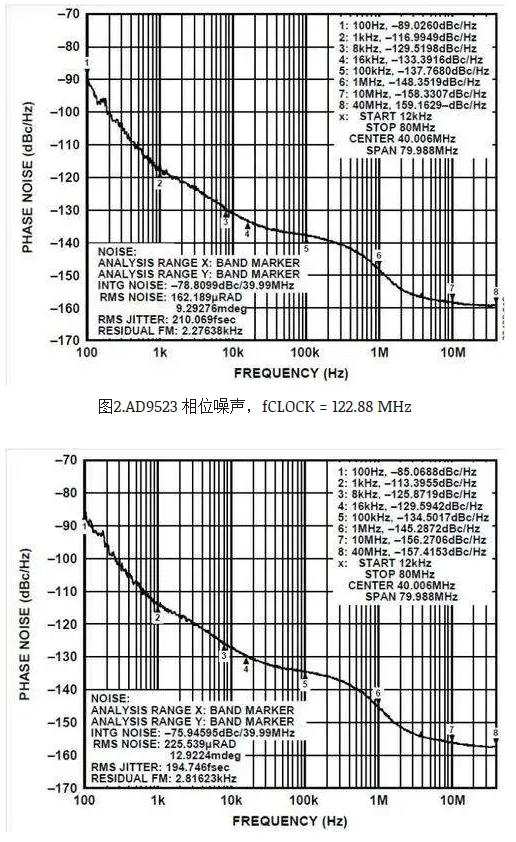

我從AD9523復制了在兩種條件下產生的相位噪聲圖。第一個輸出時鐘頻率為122.88 MHz,第二個輸出時鐘頻率為184.32 MHz。現(xiàn)在我將做另一個近似值,盡管在術語上有點寬松。我將使用這兩個圖中的數據,并執(zhí)行線性插值,以近似地估算出輸出時鐘頻率為10.245 MHz時76 MHz偏移時的相位噪聲。

圖3.AD9523 相位噪聲,fCLOCK = 184.32 MHz

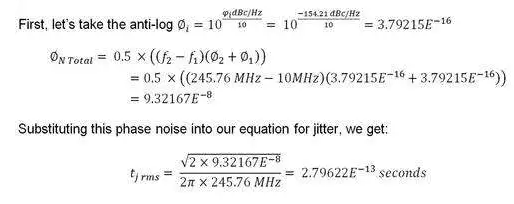

輸出頻率為122.88 MHz時,相位噪聲在158 MHz偏移時為-3307.10 dBc/Hz。同樣,輸出頻率為184.32 MHz時,相位噪聲為-156.2706 dBc/Hz。 執(zhí)行線性插值時,輸出頻率為10.245 MHz的76 MHz偏移處的預期相位噪聲為-154.21 dBc/Hz(如圖1所示)。現(xiàn)在,我們將使用面積近似方程來獲得積分相位噪聲。

現(xiàn)在我們有了我們需要的所有部分,但我們只缺少一個最終的方程式。我們需要計算這種抖動對AD9643SNR的影響。現(xiàn)在讓我們看看這個等式是什么樣子的,并插入我們所知道的。我們知道時鐘頻率和均方根抖動。根據AD9643數據手冊,我們在71 MHz模擬輸入頻率下的SNR值為4.140 dBFS。讓我們使用等式,看看結果是什么:

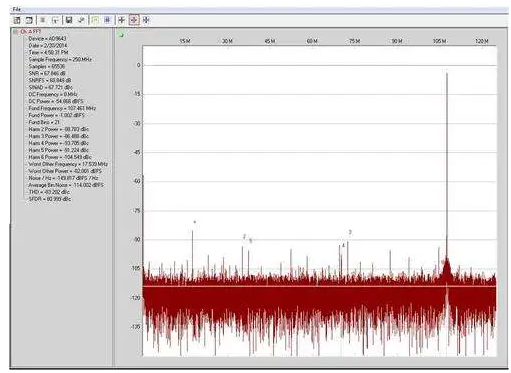

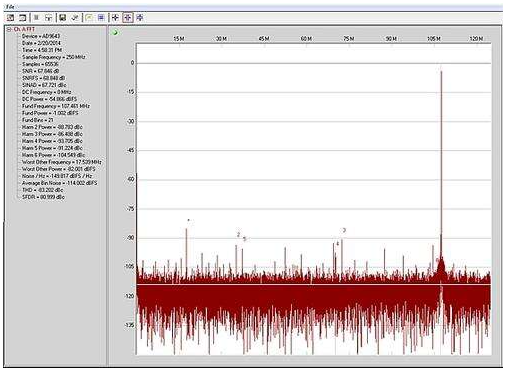

因此,現(xiàn)在使用AD68為AD763計時,我們的預期SNR值為9643.9523 dBFS。最后的檢查是在實驗室中實際設置并檢查我們的數字。讓我們看一下圖 4,看看我們是如何進行計算的。

圖4.AD9523 時鐘頻率為AD9643,頻率為245.76 MHz,fIN = 140.1 MHz

實驗室結果顯示 SNR 值為 68.848 dBFS:這是一個相當不錯的結果!這告訴我們,我可能對AD9523的預期相位噪聲有點悲觀,但實際測量結果非常接近68.653 dBFS的預測值。再一次,很高興看到預測結果和測量結果之間如此一致的結果。

審核編輯:郭婷

-

振蕩器

+關注

關注

28文章

3813瀏覽量

138871 -

adc

+關注

關注

98文章

6437瀏覽量

544088 -

時鐘發(fā)生器

+關注

關注

1文章

198瀏覽量

67226

發(fā)布評論請先 登錄

相關推薦

時鐘噪聲對于高速DAC相位噪聲的影響

測量較低時鐘頻率的相位噪聲和相位抖動

時鐘抖動(CLK)和相位噪聲之間的轉換

殘余相位噪聲測量從外部噪聲源中提取DUT噪聲

ADC噪聲:時鐘輸入和相位噪聲–測試設置

ADC噪聲:時鐘輸入和相位噪聲,第 2 部分

ADC噪聲:時鐘輸入和相位噪聲,第 2 部分

評論