我們已經看到了交錯帶來的優勢以及所有不錯的速度和帶寬帶來的一些缺點。現在讓我們繼續討論幾個讀者在不同點上評論過的另一個話題。

這個問題圍繞著ADC的噪聲貢獻因素。在評估ADC的噪聲時,我們需要考慮哪些事項?噪聲可以通過多種方式進入ADC。在接下來的幾篇博客中,我們將介紹噪聲進入ADC的所有門口,并可能出現在輸出數據的FFT中。首先,我們將從確定門口開始。

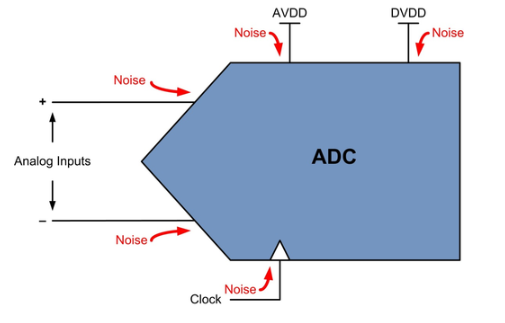

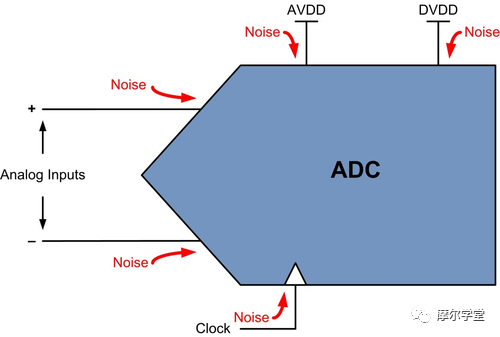

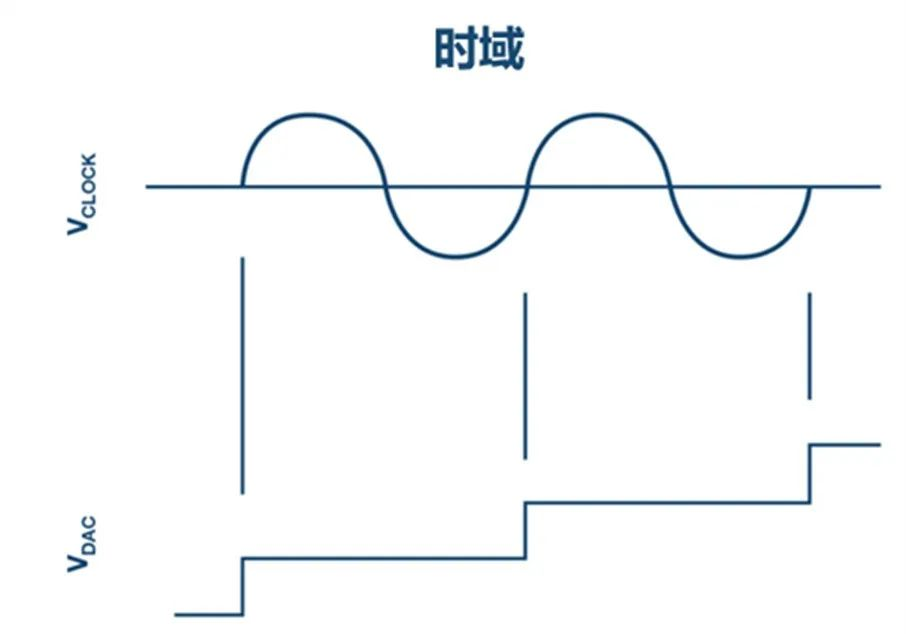

在考慮ADC中的噪聲時,幾乎可以將ADC視為混頻器。如果有噪聲從各種門口中的任何一個進入ADC,則噪聲可以表現在輸出數據的FFT中。如圖1所示,噪聲可以通過電源輸入、模擬輸入和時鐘進入轉換器。

圖1

ADC噪聲“門口”

由于噪聲在這里是一個相當寬松的術語,讓我們根據所討論的ADC的輸入(門口)來賦予它更多的含義。我們將從圖表的頂部開始,逆時針方向工作。

電源輸入是噪聲進入ADC并出現在輸出數據的FFT中的路徑。在這種情況下,有幾種方法可以評估這種噪聲及其對ADC性能的影響。ADC的設計應使器件本身衰減來自電源的噪聲輸入。這里用于評估電源噪聲的測量值是電源抑制比(PSRR)和電源調制比(PSMR)。通過測量這兩個參數,我們可以了解ADC處理通過電源輸入輸入的噪聲的能力。稍后我們將更詳細地介紹這一點。現在,讓我們繼續看噪音門口。

接下來,讓我們看一下ADC的模擬輸入。從這個角度來看,必須從兩個方面考慮噪聲。首先,一般寬帶噪聲通過模擬輸入進入轉換器,通常來自信號鏈中ADC之前的組件。我們可以為ADC選擇噪聲極低的驅動放大器,但放大并輸入ADC的噪聲量仍然有限。

為了幫助解決這個問題,ADC的輸入端通常使用抗混疊濾波器(AAF)。這有助于濾除可能進入ADC的大部分寬帶噪聲。這最終體現在ADC的信噪比(SNR)中。除寬帶噪聲外,雜散成分和諧波也可以通過模擬輸入進入ADC。AAF 也有助于過濾這些。這將反映在ADC的無雜散動態范圍(SFDR)上。擁有良好的 AAF 設計來幫助這兩個方面非常重要。同樣,我們將在以后的博客中更詳細地研究這一點。

當我們圍繞ADC逆時針移動時,我們看到的最后一個門口是時鐘輸入。該輸入與模擬輸入類似,允許寬帶噪聲以及雜散和諧波成分進入ADC,并出現在輸出數據的FFT中。確保選擇適當的時鐘輸入驅動器,為ADC提供干凈的低抖動輸入時鐘非常重要。

該時鐘信號應以這樣一種方式路由到ADC,使其不會耦合到可能進入ADC的噪聲中。與模擬輸入類似,時鐘輸入端可以使用濾波器來幫助濾除可能通過時鐘輸入進入ADC的噪聲。同樣,與模擬輸入的情況一樣,通過時鐘輸入的噪聲機制可以在ADC的SNR和SFDR性能中體現出來。

在使用ADC設計系統時,必須考慮所有這些門口。我們看到,我們應該將ADC視為一個混頻器,它將來自這些門口中的任何一個的各種噪聲成分混合到FFT的輸出數據中。顯然,系統設計人員希望僅在ADC的輸出端獲得所需信號。為此,我們必須對每個輸入采取適當的步驟,以確保噪聲最小化并且不會進入這些門口。請繼續關注我們更深入地探討這些輸入中的每一個,并更詳細地評估噪聲如何耦合到ADC中,以及可以采取哪些措施來防止噪聲。

審核編輯:郭婷

-

濾波器

+關注

關注

160文章

7729瀏覽量

177689 -

adc

+關注

關注

98文章

6438瀏覽量

544104 -

混頻器

+關注

關注

10文章

678瀏覽量

45616

發布評論請先 登錄

相關推薦

當堆棧被配置為空Mac地址時,無法理解Mac地址從何而來

STM32CubeIDE生成的固件文件字節從何而來

使用QSPI外設讀寫外部閃存存在的延遲從何而來?該如何解決?

SAI模塊輸出不包括WS信號,RT1024上的WS從何而來?

無線電技術NFC、RFID從何而來?

嵌入式系統上的軟件從何而來

步進電機的抖動和噪音從何而來 如何使步進電機完全靜音

ADC噪聲:從何而來?

ADC噪聲:從何而來?

評論