我們已經用我們漂亮的數學家的帽子來觀察失調和增益失配的雜散幅度,所以現在讓我們用它來量化由于時序不匹配引起的雜散水平。正如我們在之前的討論中看到的,由于時序不匹配引起的雜散出現在 fS/2 ± f在,這與出現增益失配雜散的位置相同。

現在,我們討論的結果將給我們留下信息,這些信息將告訴我們在f處有多少刺激。S/2 ± f在增益失配的結果以及時序失配的結果。這很重要,因為它將在交錯時幫助我們分辨出哪個不匹配給我們帶來了最大的麻煩。讓我們希望我們最終不會陷入一個兩者都非常糟糕的境地......但這不是首先嘗試交錯時的重點。我們希望從設計過程的開始,盡量減少不匹配。

因此,讓我們戴上數學家的帽子,再次深入研究數學,看看我們如何計算f處的雜散大小。S/2 ± f在由于時序不匹配。我想我們快要把這頂帽子收起來一段時間,讓我們的工程師的帽子重新戴上,但讓我們再用一會兒這頂數學帽子。

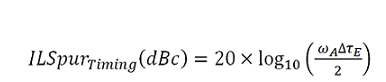

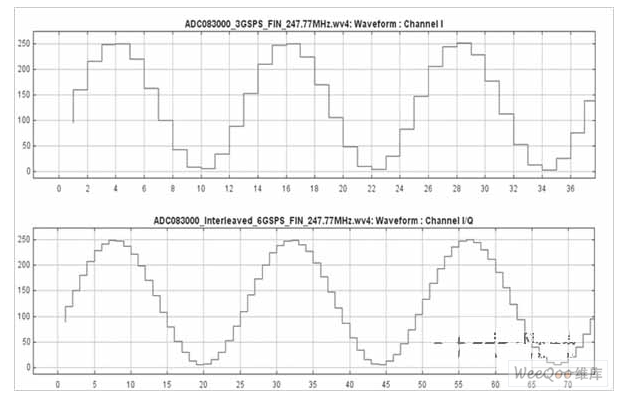

現在讓我們看看計算結果,看看時序不匹配的刺激會有多大。讓我們看一下下面的公式1,其中ω一個是模擬輸入頻率和 ΔτE是時序不匹配。

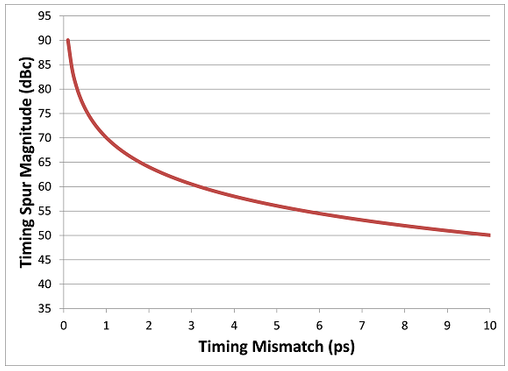

現在,讓我們考慮雙通道器件中兩個14位250MSPS ADC之間的典型時序不匹配。典型值可能在 1ps 左右。

1ps 時序失配將導致 f 時交錯雜散為 70dBcS/2 ± f在.對于大多數應用程序可以容忍的最大雜散水平來說,這是正確的。這仍然很容易主導交錯式ADC的無雜散動態范圍(SFDR)規格。

二次和三次諧波以及任何其他雜散輸出很可能小于70dBc。現在讓我們來看看我們可以做些什么來超過70dBc的水平。我們希望降低它,因為有些應用需要80至90dBc的無雜散動態范圍。在下面的圖1中,時序失配雜散的大小與以皮秒為單位的時序失配進行了示。

圖1

時序雜散與時序失配(交錯式14位ADC)。

這個情節向我們展示了幾件事。與增益失配圖類似,雜散的大小大致遵循指數衰減,一旦失配接近10ps,雜散幅度的圖就會變得幾乎平坦。此外,它告訴我們,我們需要使時序失配非常小(飛秒范圍),以使雜散幅度進入90dBc范圍。這讓我們了解兩個ADC之間的時序需要匹配的程度。當我們談論飛秒時,這是非常小的!

然而,隨著工藝技術的縮小和匹配技術的改進,將交錯ADC之間的時序失配降至最低變得有些容易。請注意,布局只是拼圖的一部分。在ADC目前達到的高速下,達到千兆采樣范圍,需要進行某種校準,以便將時序失配減少到飛秒范圍。這告訴我們,有希望;我們只需要找出一個好的校準方案來減少不匹配。

審核編輯:郭婷

-

adc

+關注

關注

98文章

6443瀏覽量

544130 -

SFDR

+關注

關注

0文章

38瀏覽量

12904

發布評論請先 登錄

相關推薦

設計實戰:怎么解決阻抗不匹配問題

PCB層級中時序交錯式高速類比ADC解決方案

DDR線長匹配與時序

交錯ADC之間的增益不匹配

模塊間接口設計不匹配問題

基于數學形態學的模糊模板匹配方法

時序交錯式類比數位轉換器的技術應用和系統設計解決方案

交錯雜散:增益失配的更多數學細節

什么是阻抗匹配 阻抗不匹配怎么解決

PCB層級中時序交錯式超高速ADC解決方案

交錯馬刺:時序不匹配的數學

交錯馬刺:時序不匹配的數學

評論