概述

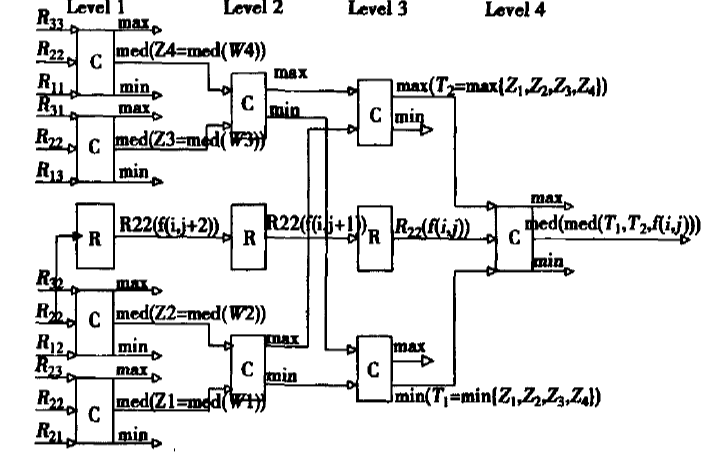

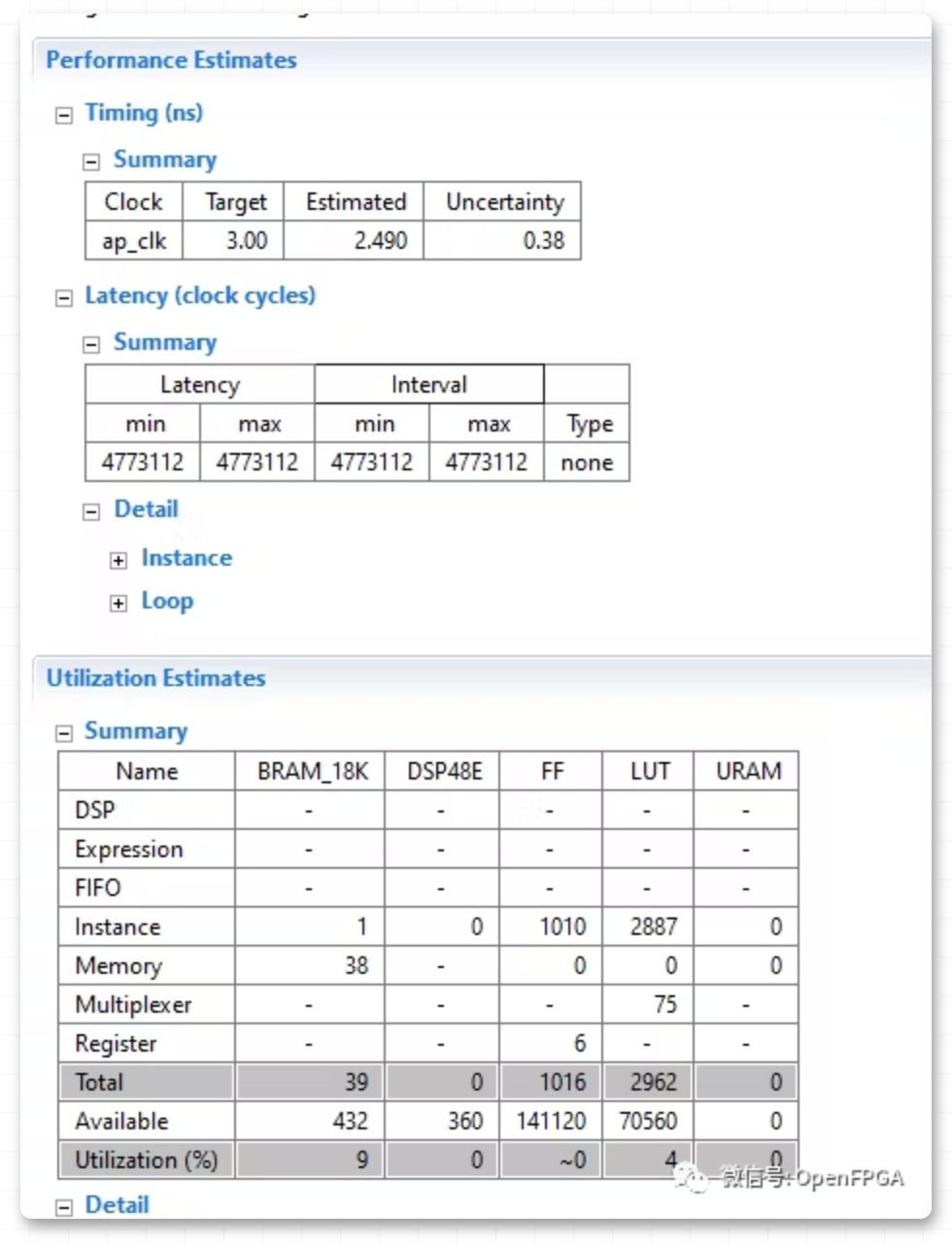

該項目包含使用高級綜合 (HLS) 的 2D 中值濾波器算法的實現。該項目的目標是在不到 3 ms的時間內對測試圖像進行去噪,同時消耗不到 25% 的可用 PL 資源。特征如下:

包含具有任意精度數據類型的高效數據類型管理。

采用 HLS 編譯指示來確保最佳系統性能。

通過多個測試用例進行驗證。

內容

該項目包含以下內容:

2D中值濾波器算法的源代碼文件

C 仿真文件

協同仿真文件

綜合文件

包含干凈和有噪聲的圖像數據的 CSV 文件

仿真和綜合過程的屏幕截圖

設置和安裝

該項目已在 Vivado HLS 中設計和測試。要設置并運行項目:

克隆此倉庫:git clone

打開 Vivado HLS 軟件并導入項目。

加載包含圖像數據的 CSV 文件。

運行 C 仿真以確保算法正常運行。

進行綜合和協同仿真。

用法

將項目導入 Vivado HLS 后:

運行 C 仿真以驗證中值濾波器的功能。

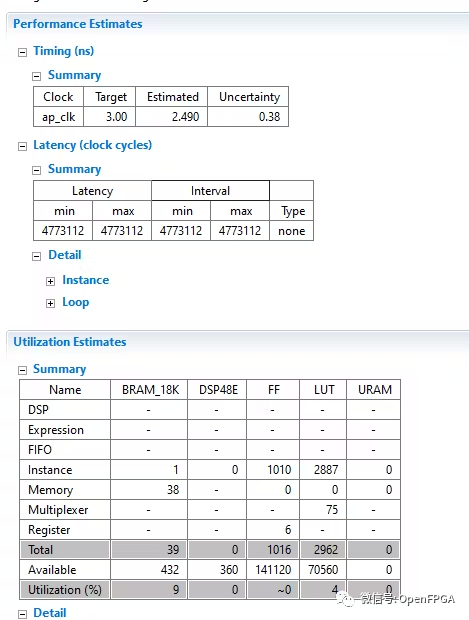

執行綜合過程以查看資源利用率報告并進行必要的調整。

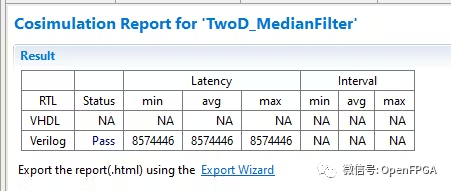

執行協同仿真以確保綜合設計的行為符合預期。

請注意:可能需要根據所使用的 FPGA 板調整代碼中的 HLS 編譯指示以獲得最佳性能。

最終設計應用于測試數據時,在不到 12 ms的時間內實現了去噪,總體 PL 資源利用率約為 13%。

審核編輯:劉清

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601814 -

濾波器

+關注

關注

160文章

7727瀏覽量

177671 -

Vivado

+關注

關注

19文章

808瀏覽量

66323 -

HLS

+關注

關注

1文章

128瀏覽量

24031 -

csv

+關注

關注

0文章

38瀏覽量

5804

原文標題:2D 中值濾波算法實現

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于算術平均算法的中值數字濾波器設計

使用高級綜合HLS開發2D中值濾波器算法

使用高級綜合HLS開發2D中值濾波器算法

評論