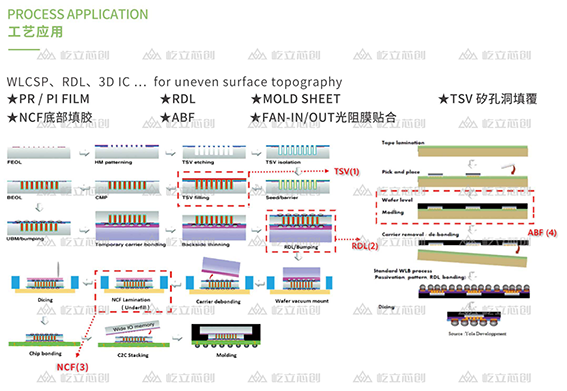

編者注:TSV是通過在芯片與芯片之間、晶圓和晶圓之間制作垂直導通;TSV技術通過銅、鎢、多晶硅等導電物質的填充,實現硅通孔的垂直電氣互聯,這項技術是目前唯一的垂直電互聯技術,是實現3D先進封裝的關鍵技術之一。

在2000年的第一個月,Santa Clara University的Sergey Savastiou教授在Solid State Technology期刊上發表了一篇名叫《Moore’s Law – the Z dimension》的文章。這篇文章最后一章的標題是Through-Silicon Vias,這是 Through-Silicon Via 這個名詞首次在世界上亮相。這篇文章發表的時間點似乎也預示著在新的千禧年里,TSV注定將迎來它不凡的表演。

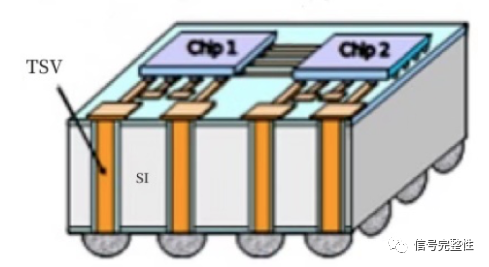

TSV示意圖

TSV,是英文Through-Silicon Via的縮寫,即是穿過硅基板的垂直電互連。

如果說Wire bonding(引線鍵合)和Flip-Chip(倒裝焊)的Bumping(凸點)提供了芯片對外部的電互連,RDL(再布線)提供了芯片內部水平方向的電互連,那么TSV則提供了硅片內部垂直方向的電互連。作為唯一的垂直電互連技術,TSV是半導體先進封裝最核心的技術之一。

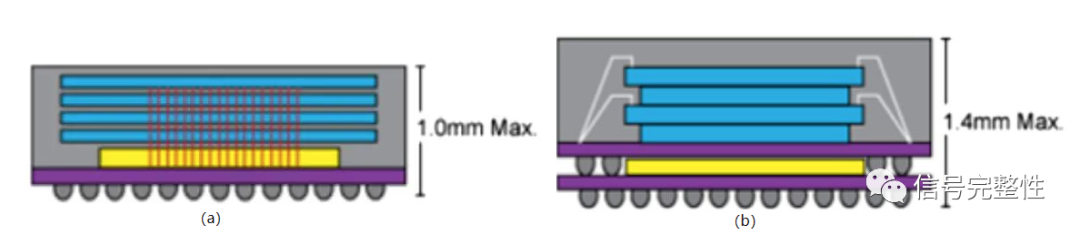

TSV封裝(a)與wirebond疊層封裝(b)對比圖

與集成電路一起誕生的垂直互聯

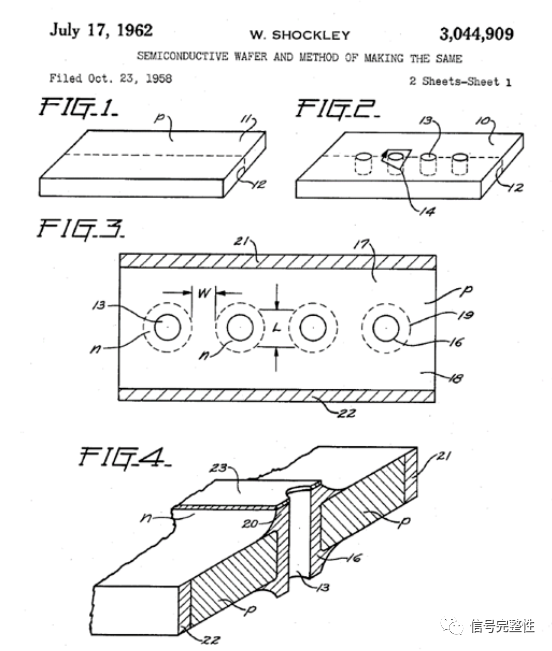

1958年的秋天,肖特基(William Shockley)坐在辦公室思考著如何設計晶體管可以實現高頻的應用。早在1947年,他便與巴丁、布拉頓一起研制出了第一個晶體管,并在1956年一起獲得了諾貝爾獎。 “為什么不能在晶圓上打些孔?” Shockley喃喃自語。 不久Shockley申請了一項專利 -(SEMICONDUCTIVE WAFER AND METHOD OF MAKING THE SAME),這是歷史上第一項在晶圓上刻蝕通孔的專利。雖然這項專利的初衷是只為了晶體管在在高頻率領域的應用,但在這項專利中,肖老也提到了如果需要可以在通孔中填充導電金屬。就這樣,發明晶體管的人也成了第一個想到在晶圓做導電孔的人。同一年還發生一件大事,將多個晶體管制造在一起的集成電路(芯片)也被發明出來了。

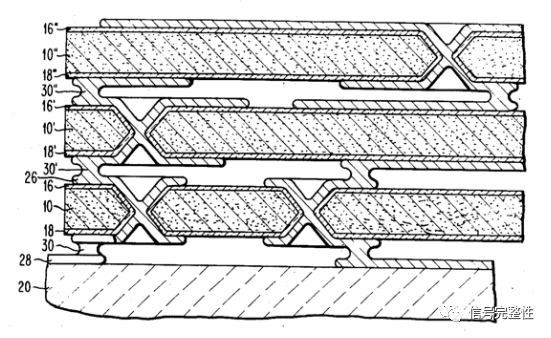

肖特基的硅片上制作孔專利 此后, IBM開始在集成電路領域發力,并在垂直電互連方面取得了突破。 6年之后的1964年,IBM申請了一項專利(METHODS OF MAKING THRU- CONNECTIONS IN SEMICONDUCFOR WAFERS),提出了利用在通孔中做簡并摻雜降低電阻的方式實現硅片的垂直互連,即用低阻硅為導電材料。但是這項專利還只是停留在硅片自身上下表面器件的,并沒有用于多芯片的堆疊。直到5年后的1969年,IBM才在另一項專利(HOURGLASS-SHAPED CONDUCTIVE CONNECTIONTHROUGH SEMCONDUCTOR STRUCTURES)中首次提出了基于垂直互連的多層芯片的堆疊,如下圖:

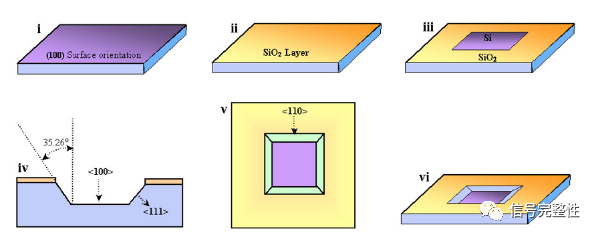

第一個芯片堆疊專利 似乎只用了11年,甚至在TSV這個名詞被正式發明前,垂直互連的概念和工藝都已經發展好了。只是IBM的這項專利并沒有得到大規模的應用。原因在于這個專利中導通孔的形狀,如其專利名字“HourGlass”所示,是沙漏形的,它占用太多的面積。這種形狀的通孔涉及到2年前(1967年)Bell Telephone Laboratories的H.A. Waggener的一項發現:KOH對于單晶硅的不同晶面的腐蝕速率有巨大的差異【1】。 例如對<100>晶面的腐蝕率要比<111>晶面大幾百倍。利用這個特點可以在常用的<100>硅晶圓很方便的刻蝕的通孔,但是孔形是倒金字塔形狀的(或者說是沙漏形的)。隨著摩爾定律的不斷發展,單位面積上晶體管越來越密集,這種占用大量表面積的垂直互連顯然失去了其存在的意義。

KOH刻蝕示意圖 但或許是受IBM提出的這個堆疊芯片概念的影響,三維集成芯片這個理念在半導體行業像星星之火燎原一樣傳播開來。此后共計有40多家研究機構和公司參與了相關技術的研究【2】,而作為三維堆疊芯片中最核心的垂直電互連技術自然也倍受關注。在接下來的70到90年代,半導體微加工技術的多項突破將為現代TSV的誕生打下堅實的基礎。

技術的突破

硅作為一種半導體材料,既沒有很好的導電性也沒有很好的絕緣性。要在硅片上實現垂直的電互連,一般需要在上面制作微孔(取決于具體的應用,一般孔徑在幾個微米到幾百微米,頭發絲約為50微米,而且單片硅片上需要的孔數量可達數十萬);在孔的側壁沉積絕緣材料;在微孔中填充導電材料等制造步驟。其中最具挑戰的是微孔的批量刻蝕和導電化。

首先,在硅晶圓上加工微孔不是件容易的事。硅硬度大且脆,而需要加工的孔徑小且量大,用傳統的機械加工方式根本不可行。在1958年肖特基的專利中,他提出了用晶料界面的化學腐蝕速率的差異來實現微孔的刻蝕(因為歷史久遠加上缺少足夠資料,未能完全理解肖老的這種腐蝕方法*_*)。 反向濺射(即等離子物理轟擊刻蝕)也曾被嘗試做刻蝕,但是速率太慢,于是人們不得不又回到化學腐蝕的老路上。

上文提到的KOH刻蝕是化學腐蝕的一種,屬于各向異性腐蝕,只是無法實現最合適TSV的圓柱孔。80年代開始,日本開始在三維集成方面發力,成立了“Three-Dimensional Circuit Element R&D Project”。1983年和1984年Hitachi的兩項專利中都提到了用激光打孔的方式來解決硅片上微孔刻蝕的問題【3】。

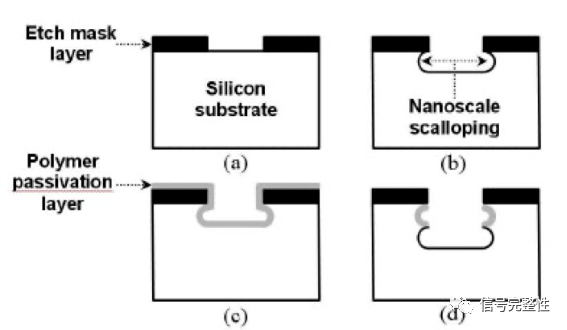

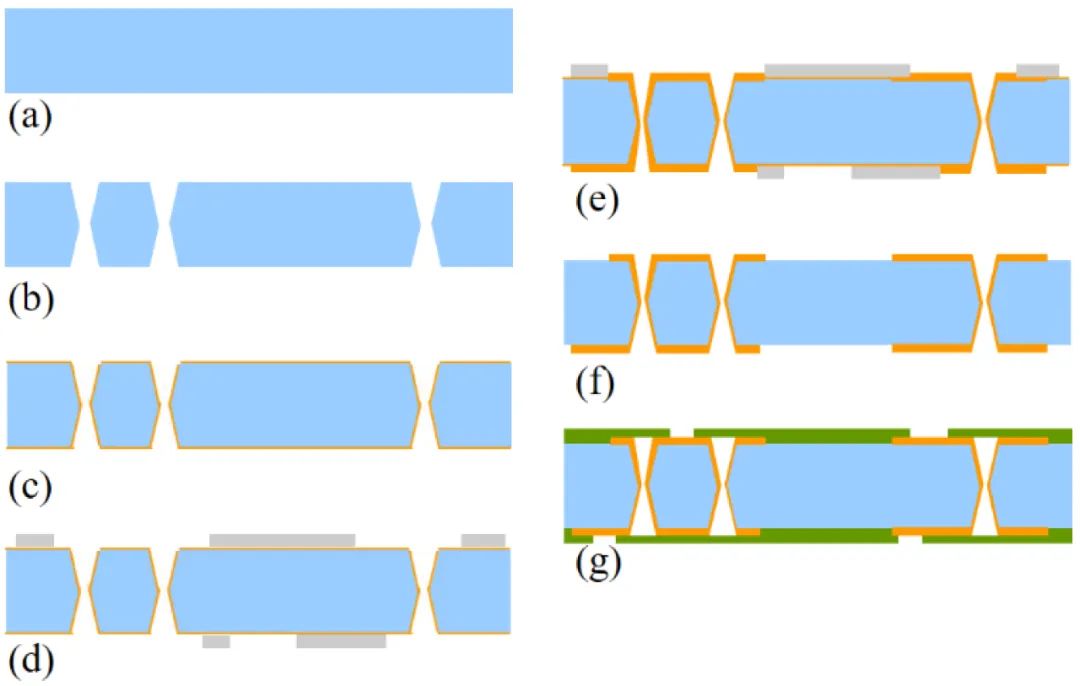

不同于KOH刻蝕的“沙漏孔”,這些專利都使用了圓柱孔。但是激光加工也存在不少問題,一方面孔只能一個個加工比較耗時,另外加工的孔存在表面粗糙以及崩邊等問題。直到90年代,硅刻蝕才迎來了突破,DRIE深硅刻蝕技術橫空出世。 DRIE,Deep Reactive Ion Etching的首字母縮寫。 這項技術是1994年德國Robert Bosch公司在此前一項低溫離子硅刻蝕技術的基礎上發展的一項高深寬比硅刻蝕技術【4】。

這項技術用了一種很巧妙的方法實現了各向同性腐蝕來刻蝕圓柱孔。各向同性腐蝕與上面講的KOH這種各向異性腐蝕不同,它在腐蝕硅片時各個方向是均勻的,所以正常情況下它只能在硅片上刻蝕出球狀的孔。使各向同性腐蝕實現圓柱孔刻蝕的核心思想是將腐蝕分割成無數的小步。

它的具體方法是:先在硅片把需要刻蝕微孔的位置的硅裸露出來,用各向同性的腐蝕氣體在硅片上刻蝕下去一薄層,然后在刻蝕出來的坑的表面沉積保護層,再用等離子打掉坑底的保護層打掉,再用各向同性的腐蝕氣體刻蝕一薄層,通過這樣多次微小的各向同性腐蝕循環就可以在硅片上實現批量的高深寬比微孔的刻蝕。事實上這項技術如此重要,后來也成為MEMS的核心制造技術。

DRIE的示意圖 微孔的導電化也同樣富有挑戰。在1958年肖老的專利中只是提及在孔中填充金屬的想法,但并未提供任何具體的實施方法;1964年IBM的專利中是利用簡并摻雜來降低硅的電阻從而將硅自身轉化導電介質,這種方法無法用于微孔的導電化;而在1969年IBM申請的專利中,金屬層是通過濺射的方式實現的。

雖然濺射在當時是半導體主流的金屬沉積方法,但是濺射一般只能用于厚度在1um以下的薄金屬沉積,并且包覆性差,只能用于沙漏形孔的金屬化。 1970年,Hitachi公司在一個專利中首次提出將用電鍍在半導體晶圓中實現金屬沉積【5】,雖然這個專利中電鍍只是為了實現金屬與硅的歐姆接觸,但這項研究開啟了電鍍用于半導體加工的序幕。

電鍍技術是19世界上半葉由英國和俄羅斯的科學發明的一種全新的金屬成形技術,與以前人類所有的純物理金屬加工方式,例如鍛造,鑄造,蒸發沉積,濺射沉積,機加工等都不同,電鍍是一種電化學技術。這項技術一開始主要被用于金屬藝術品的批量制造。

因其沉積速度相對較快并且可以實現批量的沉積這個特點,電鍍這項技術在被發明100多年后,終于與半導體走到了一起。 5年后的1975年,IBM進一步將X射線光刻與電鍍結合,開始探索電鍍用于晶圓厚金屬的沉積【6】。

1982年,這項技術在德國被進一步發展成一項重要的 MEMS技術LIGA。全稱叫Lithographie, Galvanoformung, Abformung (英語:Lithography, Electroplating, and Molding)【7】。

這是一項結合光刻和電鍍的用于高深寬比金屬結構沉積的技術。作為MEMS(微電子機械)的核心技術,LIGA為MEMS早期的發展立下不少功勞。如果對上文還有印象的話,DRIE深硅刻蝕后來也成為MEMS的核心技術。所以說TSV和MEMS在技術是孿生兄弟一點都不為過! 90年代中期,半導體行業發生一件大事:IBM用銅電鍍大馬士革工藝全面替代的濺射鋁作為集成電路中晶體管互連。這樣電鍍銅在半導體行業便開始成為標準工藝,這讓電鍍銅用于TSV的微孔金屬化填充更加順理成章。 至此,現代TSV的兩項核心技術:深硅刻蝕和電鍍都出現了。

走向商用

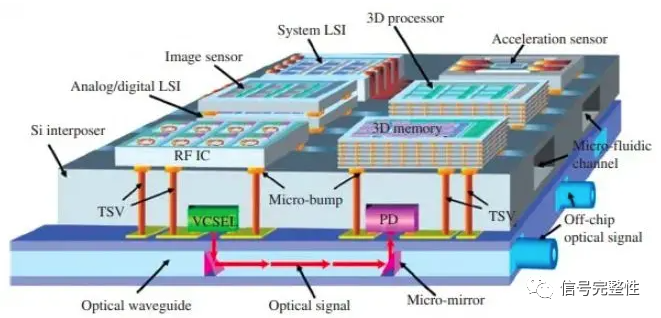

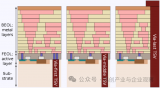

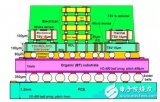

TSV不僅賦予了芯片縱向維度的集成能力,而且它具有最短的電傳輸路徑以及優異的抗干擾性能。隨著摩爾定律慢慢走到盡頭,半導體器件的微型化也越來越依賴于集成TSV的先進封裝。TSV對于像CMOS Image Sensor(CIS,CMOS圖像傳感器),High Bandwidth Memory(HBM)以及Silicon interposer(硅轉接板)都極其重要。因為存在感光面的緣故,CIS芯片的電信號必須從背部引出,TSV因此成為其必不可少的電互連結構。

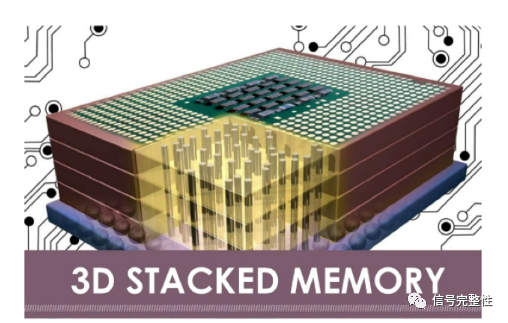

HBM是基于多層堆疊的存儲芯片,如今HBM已經可以實現12層的堆疊,16層以上更多層的堆疊相信在不久的將來也會實現,當然這一切都離不開TSV的互連。而Silicon interposer可以將多種芯片,像CPU, memory, ASIC等集成到一個封裝模塊的關鍵組件,它的垂直互連同樣需要TSV。事實上,法國的Yole development咨詢公司曾做過一項研究發現TSV幾乎可以應用于任何芯片的封裝以及任何類型的先進封裝,包括LED, MEMS等。

正是因為TSV的重要性,各大Foundry和OSTA公司也不斷投入TSV技術的研發。這階段的研發重點是如何保證電鍍沉積主要發生在TSV孔內而不是硅片表面。如果不采取任何措施,電鍍時硅表面金屬沉積的速度會遠快于TSV孔內。這個問題目前的解決方法是在電鍍液中添加抑制劑和加速劑,分別抑制硅片表面的金屬沉積并加速TSV孔內的沉積。為了獲得完美的填充效果和足夠高的良率,各大Foundry和OSTA公司都做了大量研究以獲得最佳的電鍍的參數,例如電流,溫度,硅片的與電極的相對位置,添加劑的濃度等。各大半導體設備公司也開始針對TSV的電鍍推出專用的半導體設備。

21世紀,基于深硅刻蝕和銅電鍍工藝的TSV技術日漸成熟,并開始正式走向商用。1999年和2000年,日本分別率先研發出第一款三層堆疊的圖像傳感器和三層堆疊的存儲器件。2004年,出于對TSV未來應用前景的看好,TSV名詞的提出者Sergey Savastiou教授成立了ALLVIA的公司專注于TSV代工制造。2005年,10層堆疊的存儲芯片被研制出來。2007年集成TSV的CIS芯片由Toshiba公司量產商用,同年ST Microelectronics和Toshiba一起推出8層堆疊的NAND閃存芯片。2013年第一款HBM存儲芯片由韓國Hynix推出。2015年,第一款集成HBM的GPU由AMD推出。

不走尋常路的Sil-Via

隨著TSV在CIS和HBM中的大規模應用,似乎TSV技術已經成熟并沒有太多可以創新的空間了。但是無論是CIS還是HBM,其中用到的TSV都是孔徑只有10微米左右的小孔徑TSV,而基于電鍍的TSV卻一直沒能攻下最后一個陣地:大孔徑TSV的實心填充。對于大孔徑例如直徑50微米以上甚至100多微米的微孔,如果用電鍍填充滿需要幾個小時,不僅成本非常高而且良率也難以保證。

對于大孔徑TSV,瑞典有家MEMS公司卻走出了另外一條“特色”技術路線。這家叫 Silex的公司不走尋常路,獨立開發出了一項基于低阻硅的Sil-Via的TSV技術。Sil-Via與電鍍TSV有兩大不同:首先,它用的硅基板材料本身就是低阻硅,類似于1964年IBM專利中的簡并摻雜硅。其次,在制造過程中,Sil-Via刻蝕的不是孔而是環槽,通過在環槽是填充絕緣材料的方式實現中心低阻硅圓柱作為導電介質。

Sil-Via主要用于MEMS器件的封裝中,正是因為Sil-Via的巨大成功,Silex也成為世界最大的MEMS代工廠。2015年7月,中國資本收購了Silex,只是Sil-Via這項技術的核心,在幾十微米的圓槽中飽滿填充可以耐800度以上溫度的絕緣材料,仍然被瑞典人所掌握著。但Sil-Via并不完美,低阻硅只能滿足MEMS器件的導電要求,金屬化的大孔徑TSV孔依舊有著很大的需求,而這又涉及到一條新的技術路線,以后專門寫一篇細說。

Sil-Via(from silex website )

高密度集成:通過先進封裝,可以大幅度地提高電子元器件集成度,減小封裝的幾何尺寸和封裝重量。克服現有的2D-SIP(System In a Package,二維系統級封裝)和PoP(Package on Package,三維封裝堆疊)系統的不足,滿足微電子產品對于多功能和小型化的要求。

提高電性能:由于TSV技術可以大幅度地縮短電互連的長度,從而可以很好地解決出現在SOC(二維系統級芯片)技術中的信號延遲等問題,提高電性能。

多種功能集成:通過TSV互連的方式,可以把不同的功能芯片(如射頻、內存、邏輯、數字和MEMS等)集成在一起實現電子元器件的多功能。

降低制造成本:雖然目前TSV三維集成技術在工藝上的成本較高,但是可以在元器件的總體水平上降低制造成本。

TSV技術實現CMOS、MEMS以及光電子電路三維混合集成示意圖

TSV的主要技術環節

通孔的形成

晶片上通孔的加工是TSV技術的核心,目前通孔加工的技術主要有三種,一種是干法刻蝕,一種是濕法刻蝕,還有一種是激光打孔。在這三種方法中,干法刻蝕具有速度快、方向性好、控制性強等優點成為通孔制造的最常用方法;激光打孔速度更快,但因為熱損傷將導致精度降低,所以現行并未常用。

相關特殊晶片的制作

如果晶片用于3D封裝則需要減薄,以保證形成通孔的孔徑與厚度比例在合理范圍。若不考慮層堆疊的要求,芯片間的通孔互連技術要求上層芯片的厚度在20-30微米。晶片減薄技術中需要解決磨削過程晶片始終保持平整狀態,減薄后不發生翹曲、下垂、表面損傷擴大、晶片破裂等問題。

通孔的金屬化

TSV的通孔金屬化,通常是以電鍍的方法進行的。但由于硅基板本身基體的導電性較差,不能直接進行電沉淀。所以,其金屬化將首先使用PVD沉淀(Physical Vapor Deposition,物理氣相沉淀)出厚度為數個納米的電子層,使得硅基板有導電性之后,再進行電鍍。

TSV鍵合

完成通孔金屬化和連接端子的晶片之間的互連通常稱為TSV鍵合技術。這種技術采用的工藝有金屬-金屬鍵合技術和高分子粘結鍵合等,而目前以金屬-金屬鍵合技術為主要方式,因為這種技術可以同時實現機械和電學的接觸界面。例如銅-銅鍵合在350-4000℃下施加一定壓力并保持一段時間,接著在氮氣退火爐中經過一定時間退火而完成TSV鍵合。

TSV的技術關鍵

3D IC技術繼續向細微化方向發展,硅通孔3D IC技術互連尚待解決的關鍵技術之一是通孔的刻蝕。TSV穿孔主要有兩種工藝取向---先通孔(via first)和后通孔(via last),前者是在IC制作過程中制作通孔,后者在IC制造完成之后制作通孔。先通孔工藝又分為兩種---前道互連型和后道互聯型。前者是在所有CMOS工藝開始之前在空白的硅晶圓上,通過深度離子刻蝕(DRIE,Deep Reactive Ion Etching)實現,由于穿孔后必須承受后續工藝的熱沖擊(通常高于1000℃),因而多使用多硅晶作為通孔的填充材料;而后道互連型則是在制造流程中在制造廠實現的,一般使用金屬鎢或銅作為填充材料。顯然,先通孔方法必須在設計IC布線之中預留通孔位置,在IC器件制造完成之后,在預留的空白區域進行穿孔,一般采用激光鉆孔的方式,通過電鍍鍍銅實現金屬化,因而具有更好的導電性能。

此外,3D TSV的關鍵技術還包括:通孔的形成;堆疊形式(晶圓到晶圓、芯片到晶圓或芯片到芯片);鍵合方式(直接Cu-Cu鍵合、粘接、直接熔合、焊接);絕緣層、阻擋層和種子層的淀積;銅的填充(電鍍)、去除;再分布引線(RDL)電鍍;晶圓減薄;測量和檢測等。

結 語

2022年3月9號,蘋果公司推出的M1 ULTRA處理器,這款性能爆表的處理器中,多個CPU使用帶TSV的Silicon interposer進行集成的。如今,無論是AI/AR/VR中用到的傳感器,圖像傳感器,堆疊存儲芯片以及高性能處理器,都越來越離不開TSV。 TSV, 這項并不為人熟知的技術,正在硬件的底層深深的影響著人類的生產生活方式。 半個多世紀前的那個秋天,肖特基那個在硅片上打孔的想法最終將人類帶入了人工智能的時代。

審核編輯:劉清

-

CMOS

+關注

關注

58文章

5689瀏覽量

235171 -

mems

+關注

關注

129文章

3903瀏覽量

190376 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

TSV技術

+關注

關注

0文章

17瀏覽量

5669

原文標題:【科普】硅通孔TSV-Through-Silicon Via

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

硅通孔(TSV)電鍍

TSV與μbumps技術是量產關鍵

12英寸深硅刻蝕機銷售突破百腔,北方華創助力Chiplet TSV工藝發展

先進封裝技術之爭 | 巨頭手握TSV利刃壟斷HBM市場,中國何時分一杯羹?

開啟高性能芯片新紀元:TSV與TGV技術解析

硅通孔TSV-Through-Silicon Via

硅通孔TSV-Through-Silicon Via

評論