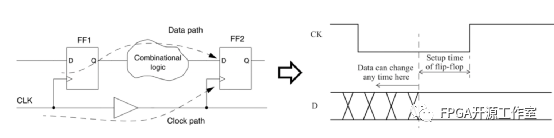

1 setup time

Setup time (建立時間)是數據信號(D)在時鐘事件(這里以時鐘上升沿為例)發生之前保持穩定的最小時間。以便時鐘可靠地對數據進行采樣。適用于同步電路,如觸發器(flip-flop)。

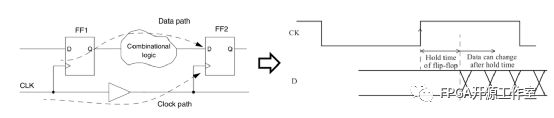

2 hold time

Hold time (保持時間) 是數據信號(D) 在時鐘事件(這里以時鐘上升沿為例)發生之后保持穩定的最小時間。

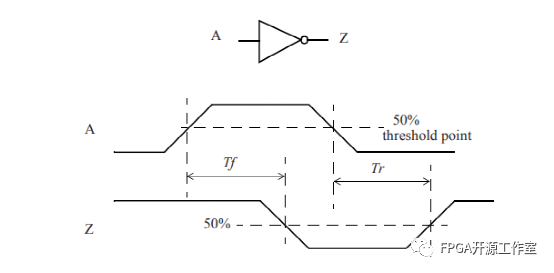

3 Propagation Delay

信號傳播延時(Propagation Delay),以反相器(Inverter)為例,A輸入信號變化(0-1的50%)為開始,到Z輸出信號變化(1-0的50%)所需的時間稱為Tf, A輸入信號變化(1-0的50%)為開始,到Z輸出信號變化(0-1的50%)所需的時間稱為Tr。

Output fall delay (Tf)

Output rise delay (Tr)

# Threshold point of an input falling edge: input_threshold_pct_fall : 50.0; # Threshold point of an input rising edge: input_threshold_pct_rise : 50.0; # Threshold point of an output falling edge: output_threshold_pct_fall : 50.0; # Threshold point of an output rising edge: output_threshold_pct_rise : 50.0;

審核編輯:劉清

-

觸發器

+關注

關注

14文章

1996瀏覽量

61057 -

時序分析

+關注

關注

2文章

127瀏覽量

22551 -

同步電路

+關注

關注

1文章

60瀏覽量

13299

原文標題:時序分析的基本概念(1)

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序分析基本概念

時序分析基本概念介紹

FPGA設計中時序分析的基本概念

時序分析基本概念介紹—Timing Arc

時序分析基本概念解析

時序分析的基本概念

時序分析的基本概念

評論