今天我們要介紹的基本sdc是 時序特例 ,也就是我們常說的Path exception。針對一些路徑需要的一些特殊設定,常用的有set_false_path, set_multicycle_path, set_max_delay,set_min_delay等

set_false_path : false path是指在正常工作環境下,并不真實存在或者經過的路徑,比如說一些靜態輸入信號產生的path。像這樣的path,我們可以指定set_false_path。這樣工具在計算timing時就不會去分析它。值得注意的是,設定false path時一定要非常小心,一定要和designer仔細確認下,不要把正常的path給誤傷掉。

例: set_false_path-from ff1/CK -through {u1/Y} -to ff2/D

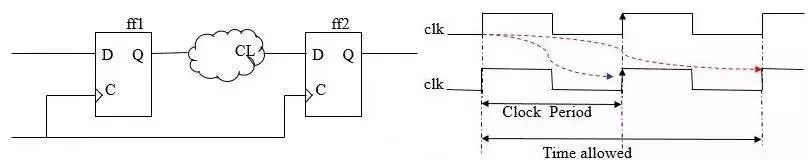

set_multicycle_path : 指的是兩個寄存器之間數據要經過多個時鐘才能穩定的路徑,一般出現于組合邏輯較大的那些路徑,也有可能是一些慢時鐘去踩快時鐘的路徑。對于這些路徑,我們可以設置multicycle path。同樣的,設置multicycle path時,也需要非常謹慎,需要和前端溝通好,該條path要設幾個cycle, -start還是-end也要理解清楚,而且默認的hold的multicycle比setup少一個。

例:

set_multicycle_path 2 -setup -from ff1/CP -to ff2/D

set_multicycle_path 1 -hold -from ff1/CP -to ff2/D

set_max_delay: 指定某段path的最大延遲,超過就是violation。用于某些特定的path,限定該path只能走這么長delay.

例:set_max_delay 8.0 -from {ff1/CP} -to {ff2/D}

set_min_delay: 指定某段path的最小延遲,小于該值就是violation。用于某些特定的path,限定該path至少應該走這么長delay.

例:set_min_delay 4.0 -from {ff1/CP} -to {ff2/D}

-

寄存器

+關注

關注

31文章

5322瀏覽量

120018 -

SDC

+關注

關注

0文章

48瀏覽量

15528 -

時序分析器

+關注

關注

0文章

24瀏覽量

5270

發布評論請先 登錄

相關推薦

VIVADO時序約束及STA基礎

時序約束 專版

介紹系統接口sdc

時序分析基本概念—SDC概述

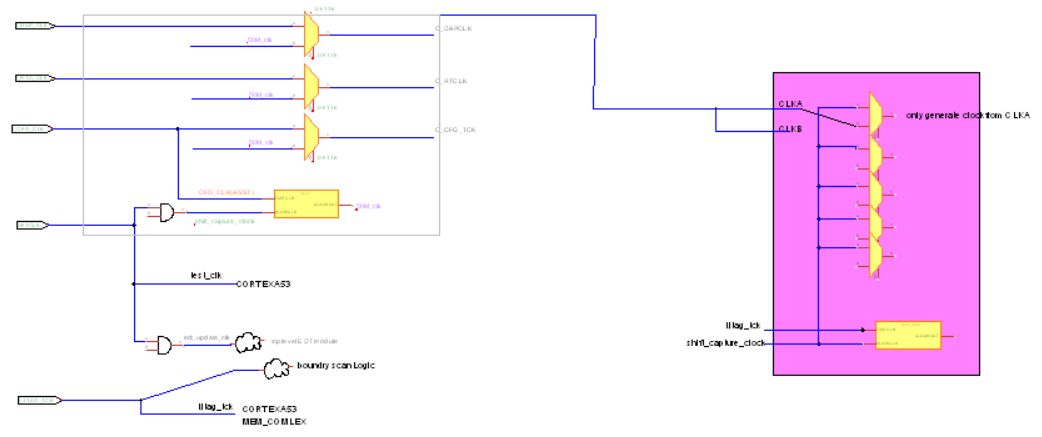

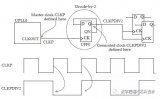

時序分析基本概念介紹<generate clock>

介紹基本的sdc時序特例

介紹基本的sdc時序特例

評論